## Porta-SIMD: An Optimally Portable SIMD Programming Language Duke CS-1990-12 UNC CS TR90-021

May 1990

Russ Tuck

Duke University Deparment of Computer Science Durham, NC 27706

The University of North Carolina at Chapel Hill Department of Computer Science CB#3175, Sitterson Hall Chapel Hill, NC 27599-3175

Text (without appendix) of a Ph.D. dissertation submitted to Duke University. The research was performed at UNC.

© 1990 Russell R. Tuck, III

UNC is an Equal Opportunity/Affirmative Action Institution.

## PORTA-SIMD: AN OPTIMALLY PORTABLE SIMD PROGRAMMING LANGUAGE

by

Russell Raymond Tuck, III

Department of Computer Science Duke University

| Date: april 26, 1990                 |

|--------------------------------------|

| Approved 1. N. NO O II               |

| Medin P. Brochy                      |

| Frederick P. Brooks, Jr., Supervisor |

| Min a. froand. M.                    |

| John A. Board                        |

| Hen Jule                             |

| Henry Fuchs                          |

| Merrell L. Patrick                   |

| Merrell L. Patrick                   |

| Con the R Reservera                  |

| Jonathan B. Rosenberg                |

|                                      |

Dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the Graduate School of Duke University

Copyright © 1990 by Russell Raymond Tuck, III All rights reserved

## Abstract

Existing programming languages contain architectural assumptions which limit their portability. I submit optimal portability, a new concept which solves this language design problem. Optimal portability makes it possible to design languages which are portable across various sets of diverse architectures. SIMD (Single-Instruction stream, Multiple-Data stream) computers represent an important and very diverse set of architectures for which to demonstrate optimal portability. Porta-SIMD (pronounced "porta-simm'd") is the first optimally portable language for SIMD computers. It was designed and implemented to demonstrate that optimal portability is a useful and achievable standard for language design.

An optimally portable language allows each program to specify the architectural features it requires. The language then enables the compiled program to exploit exactly those features, and to run on all architectures that provide them. An architecture's features are those it can implement with a constant-bounded number of operations. This definition of optimal portability ensures reasonable execution efficiency, and identifies architectural differences relevant to algorithm selection.

An optimally portable language for a set of architectures must accommodate all the features found in the members of that set. There was no suitable taxonomy to identify the features of SIMD architectures. Therefore, the taxonomy created and used in the design of Porta-SIMD is presented.

Porta-SIMD is an optimally portable, full-featured, SIMD language. It provides dynamic allocation of parallel data with dynamically determined sizes. Generic subroutines which operate on any size of data may also be written in Porta-SIMD. Some important commercial SIMD languages do not provide these features.

A prototype implementation of Porta-SIMD has been developed as a set of #include files and libraries used with an ordinary C++ compiler. This approach has allowed more rapid prototyping and language experimentation than a custom compiler would have, but modestly constrained the language's syntax. The result is a very portable but only moderately efficient implementation. Porta-SIMD has been implemented for the Connection Machine 2, for Pixel-Planes 4 and 5, and for ordinary sequential machines.

Optimal portability is an important new concept for developing portable languages which can handle architectural diversity. Porta-SIMD demonstrates its usefulness with SIMD computers.

i

#### Abstract

## Acknowledgements

I am most thankful to God, who has made possible what I could not have done alone. He enabled me to finish work which looked like it could drag on forever, and to do it in time for an impossible looking graduation deadline. He taught me a lot about faith, trust, prayer, and His peace in the process. He has given me a wonderful wife, Debbi, who loves me and makes life fun. Most of all, God gave His son Jesus to die for my failures and give me new life with meaning and hope.

I appreciate Debbi's unending patience, prayers, sacrifice, and encouragement. These have been especially important during my final push to finish, during which she has been busy finishing her own graduate degree. Our family, our church and some special friends have joined in with encouragement and prayers, for which I am very grateful. Dad's quick mid-day phone calls from California several times over the last few weeks were especially helpful.

Dr. Frederick P. Brooks, Jr. has been the consummate advisor. He has provided critically important insight, advice, and perspective. He has regularly and dependably scheduled time for our meetings, despite the many demands on his time, and that has been very important to my steady progress. I am grateful to Dr. Brooks for accepting me as his student and providing me with assured grant support, guidance, and freedom, even when all I knew about my research goals was that I wanted to improve the programming of SIMD computers. I appreciate his deep Christian faith, and have enjoyed participating in Wednesday lunch Bible studies with him.

I appreciate my committee for their encouragement and sound advice. Dr. Henry Fuchs has supported my work financially as part of the Pixel-Planes project since I began working on Porta-SIMD, and has been very supportive personally as well. Dr. Merrell Patrick also served on my M.S. committee, and has shown a personal interest in my success that was especially helpful during my transition into doctoral research. Dr. Jothy Rosenberg's ideas, interest, and personality have made him a very valuable source of encouraging advice and positive suggestions. Dr. John Board has provided sound comments and helpful references.

I appreciate Dr. Jan F. Prins' service on my committee as an *ex officio* member, doing significant work without official recognition. He has often been the most accessible member of my committee, and has served as a valuable sounding board for ideas and dilemmas.

Greg Turk, a fellow graduate student and member of the Pixel-Planes team, has been valuable as a pioneering Porta-SIMD user and for his willingness to discuss and comment on how Porta-SIMD should work. I appreciate his willingness and that of Tim Cullip for me to use their programs as examples and include them in this dissertation.

I want to thank Michael Tiemann for writing G++ (the GNU C++ compiler), for making it freely available, and for providing timely fixes to compiler bugs as they were reported.

I appreciate the encouragement and friendship of many members of the Duke and UNC Computer Science Departments, including especially my long-time office mates at Duke, Jack Briner and Mark Jones, and the entire Pixel-Planes team at UNC.

I appreciate the time Carlton Brown and Debbi Tuck spent patiently and carefully

reading drafts of this document to point out and suggest corrections for my writing errors. I appreciate the time Herb Taylor of the David Sarnoff Research Center spent helping

me understand details of the Princeton Engine, and also his friendship and encouragement.

Several institutions have been important to my research. The Departments of Computer Science at the University of North Carolina at Chapel Hill and Duke University have provided critically important computing resources and office space. My research at UNC has been supported by the Pixel-Planes Project, Drs. Henry Fuchs and John Poulton, P.I.s, and its grants: National Science Foundation grant #MIP-8601552, Defense Advanced Research Projects Agency order #6090, Office of Naval Research contract #N0014-86-K-0680; and by the GRIP Project, Frederick Brooks, P.I., under National Institutes of Health grant #RR 02170.

Access to a Connection Machine was provided first by the Advanced Computing Research Facility (ACRF) at Argonne National Laboratories, under grants NSF-ASC-8808327 and DOE-W-31-109-ENG-38, and more recently by the Connection Machine Network Server (CMNS) Pilot Facility at Thinking Machines Corporation under DARPA contract DACA76-88-C-0012.

## Contents

| A                   | bstra | act     |                                              |     | i               |

|---------------------|-------|---------|----------------------------------------------|-----|-----------------|

| Acknowledgements ii |       |         |                                              | iii |                 |

| 1                   | Inti  | roduct  | ion, Thesis, and Overview                    |     | 1               |

| 2                   | Opi   | timal I | Portability                                  |     | 5               |

| 3                   | A S   | IMD '   | Taxonomy for Optimal Portability             |     | 11              |

|                     | 3.1   | Defini  | tion of SIMD Architectures                   |     | 11              |

|                     | 3.2   | Taxon   | nomy of SIMD Architectures                   |     | 12              |

|                     |       | 3.2.1   | Feature Names                                |     | 14              |

|                     |       | 3.2.2   | Communication                                |     | 14              |

|                     |       |         | 3.2.2.1 Labeling (number, N)                 |     | 17              |

|                     |       |         | 3.2.2.2 Communication (C)                    |     | 17              |

|                     |       |         | 3.2.2.3 Collision Resolution, Write (W)      |     | 19              |

|                     |       |         | 3.2.2.4 Collision Resolution, Fetch (F)      |     | 20              |

|                     |       |         | 3.2.2.5 Piped Communication (P)              |     | $20^{-0}$       |

|                     |       |         | 3.2.2.6 Cut-Through Communication (T)        |     | 21              |

|                     |       | 3.2.3   | Local Addressing                             |     |                 |

|                     |       | 0.2.0   | 3.2.3.1 Local Addressing (L)                 |     |                 |

|                     |       | 3.2.4   | Reduce and Scan                              |     | 23<br>24        |

|                     |       | 0.4.1   | <b>3.2.4.1</b> Reduce (R)                    |     | $\frac{24}{24}$ |

|                     |       |         | 3.2.4.2 Scan (S)                             |     | $\frac{24}{25}$ |

|                     |       | 3.2.5   | Parallel I/O                                 |     | $\frac{25}{25}$ |

|                     |       | J.4.J   | 3.2.5.1 Input (I)                            |     |                 |

|                     |       |         |                                              |     | 25<br>01        |

|                     |       | 0.0.4   | 3.2.5.2 Output (O)                           |     | 25              |

|                     |       | 3.2.6   | PE to Host $I/O$                             |     | 26              |

|                     |       |         | 3.2.6.1 Get (G)                              |     | 26              |

|                     |       | 3.2.7   | Naming a Classification                      |     | 26              |

|                     | 3.3   |         | axonomy in Use                               |     | 26              |

|                     |       | 3.3.1   | PxPl4 (Pixel-Planes 4)                       |     | 29              |

|                     |       | 3.3.2   | Oldfield (Oldfield et al.)                   |     | 30              |

|                     |       | 3.3.3   | PxPl5 (Pixel-Planes 5)                       |     | 30              |

|                     |       | 3.3.4   | AIS-5000 (Applied Intelligent Systems, Inc.) |     | 30              |

|                     |       | 3.3.5   | Centipede                                    |     | 30              |

|                     |       | 3.3.6   | Princeton Engine                             |     | 31              |

|                     |       | 3.3.7   | ASP (Associative String Processor)           |     | 31              |

|                     |       | 3.3.8   |                                              |     | 31              |

CONTENTS

|   |            | 3.3.9    | SOLOMON (Simultaneous Operation Linked Ordinal MOdular Net-   |          |

|---|------------|----------|---------------------------------------------------------------|----------|

|   |            |          | work)                                                         | 32       |

|   |            |          | MPP (Massively Parallel Processor)                            | 32       |

|   |            |          | DAP (Distributed Array Processor)                             | 32       |

|   |            |          | BLITZEN                                                       | 32       |

|   |            |          | YUPPIE (Yorktown Ultra Parallel Polymorphic Image Engine)     | 33       |

|   |            |          | Unger (S. H. Unger)                                           | 33       |

|   |            | 3.3.15   | GAM Pyramid (George Mason University, Adder pyramid, MPP cir- | 0.0      |

|   |            | 9910     | cuits, Pyramidal topology)                                    |          |

|   |            |          | BVM (Boolean Vector Machine)                                  |          |

|   |            |          | GF11 (11-Gflop target performance)                            | 34       |

|   |            |          | BSP (Burroughs Scientific Processor)                          | 34       |

|   |            |          | MP-1 (MasPar Computer Corp.)                                  | 34<br>25 |

|   | 3.4        |          | CM-2 (Connection Machine, model 2)                            | 35<br>95 |

|   | <b>ð.4</b> | Previo   | bus SIMD Taxonomies                                           | 35       |

| 4 | Por        | tability | y of Existing SIMD Languages                                  | 37       |

|   | 4.1        |          | y of SIMD Languages                                           | 38       |

|   |            | 4.1.1    | Illiac IV Languages                                           | 38       |

|   |            | 4.1.2    | MPP Language                                                  | 38       |

|   |            | 4.1.3    | BVM Language                                                  | 38       |

|   |            | 4.1.4    | BSP Language                                                  | 38       |

|   |            | 4.1.5    | MP-1 Language                                                 | 38       |

|   |            | 4.1.6    | CM Languages                                                  | 38       |

|   |            | 4.1.7    | Fortran $8x$                                                  | 39       |

|   |            | 4.1.8    | Other Languages                                               |          |

|   | 4.2        |          | ng Languages Are Not Optimally Portable                       |          |

|   | 4.3        | Non-P    | Procedural Languages                                          | 40       |

| 5 | Por        | ta-SIM   | ID Language Design                                            | 41       |

|   | 5.1        |          | rements for an Optimally Portable Language                    | 41       |

|   |            | 5.1.1    | Specify Target Architecture                                   |          |

|   |            | 5.1.2    | Provide Architectural Features                                |          |

|   |            | 5.1.3    | Enforce Architectural Limits                                  |          |

|   | 5.2        | Design   | 1 Strategy and Goals                                          | 43       |

|   |            | 5.2.1    | Implementation Technology                                     |          |

|   |            | 5.2.2    | Strategy for Optimal Portability                              |          |

|   |            |          |                                                               | 45       |

|   | 5.3        |          | age Overview and Example                                      | 46       |

|   | <b>5.4</b> | Porta-   | SIMD Language Definition                                      | 50       |

|   |            | 5.4.1    | Reserved Words                                                | 50       |

|   |            | 5.4.2    | Architecture Identifiers                                      | 50       |

|   |            | 5.4.3    | Target Architecture                                           | 51       |

|   |            | 5.4.4    | Types                                                         | 51       |

|   |            |          | 5.4.4.1 Virtual Machines                                      | 51       |

|   |            |          | 5.4.4.2 Parallel Data                                         | 51       |

|   |            |          | 5.4.4.3 Declaration                                           | 52       |

|   |            |          | 5.4.4.4 Allocation                                            | 54       |

|   |            | <b>-</b> | 5.4.4.5 Lvalues                                               | 54       |

|   |            | 5.4.5    |                                                               | 54       |

|   |            | 5.4.6    | Conversions                                                   | 55       |

vi

|           | 5.4.6.1   | Representation Changes                                                                                                                                        |    |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | 5.4.6.2   | Casting                                                                                                                                                       |    |

|           | 5.4.6.3   | Assignment                                                                                                                                                    | 6  |

|           | 5.4.6.4   | Usual Unary Conversions                                                                                                                                       | 6  |

|           | 5.4.6.5   | Usual Binary Conversions                                                                                                                                      | 7  |

|           | 5.4.6.6   | Function Arguments and Return Values                                                                                                                          | 7  |

| 5.4.7     | Express   | ions                                                                                                                                                          | 7  |

|           | 5.4.7.1   | Enabled and Disabled PEs                                                                                                                                      | 3  |

|           | 5.4.7.2   | Primary and Postfix Operators                                                                                                                                 | 3  |

|           | 5.4.7.3   | Unary Operators                                                                                                                                               | 3  |

|           | 5.4.7.4   | Assignment Operator                                                                                                                                           | 3  |

|           | 5.4.7.5   | Arithmetic Operators                                                                                                                                          | )  |

|           | 5.4.7.6   | Shift Operators 59                                                                                                                                            | )  |

|           | 5.4.7.7   | Bitwise Operators                                                                                                                                             |    |

|           | 5.4.7.8   | Relational Operators                                                                                                                                          |    |

|           | 5.4.7.9   | Logical Operators                                                                                                                                             |    |

|           | 5.4.7.10  |                                                                                                                                                               |    |

| 5.4.8     |           | $\mathbf{r}$                                                                                                                                                  |    |

| 5.4.9     |           | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                          |    |

| 5.4.10    |           |                                                                                                                                                               |    |

| 5.4.11    |           |                                                                                                                                                               |    |

| 9.4.11    |           | 5                                                                                                                                                             |    |

|           |           | 1, 2, $\dots$ , N (Cartesian Coordinates) $\dots \dots \dots$ |    |

| 5 4 10    | 5.4.11.2  | p2 (Level and 2-D Coordinate)                                                                                                                                 |    |

| 5.4.12    |           | nication (C) $\ldots \ldots \ldots$           |    |

|           |           | aC (Adjacent) 64                                                                                                                                              |    |

|           |           | mC (Pyramid)                                                                                                                                                  |    |

|           |           | cC (Cube Connected Cycles)                                                                                                                                    |    |

|           |           | pC (Preselected Permutation)                                                                                                                                  |    |

|           | 5.4.12.5  | gC (Global)                                                                                                                                                   |    |

| 5.4.13    |           | Resolution, Write (W)                                                                                                                                         |    |

|           | 5.4.13.1  | sW (Select)                                                                                                                                                   | \$ |

|           |           | lW (Logically Combine)                                                                                                                                        |    |

|           |           | aW (Add or Compare) 68                                                                                                                                        | 5  |

|           | 5.4.13.4  | mW (Multiply)                                                                                                                                                 | ;  |

| 5.4.14    | Collision | Resolution, Fetch (F) 69                                                                                                                                      | )  |

|           | 5.4.14.1  | sF (Select)                                                                                                                                                   | )  |

|           | 5.4.14.2  | rF (Replicate)                                                                                                                                                | ļ  |

| 5.4.15    |           | $pmmunication (P) \dots \dots$                          | )  |

| ÷         | 5.4.15.1  | u (Unlimited)                                                                                                                                                 | ļ  |

|           | 5.4.15.2  | c (Copy)                                                                                                                                                      |    |

| 5.4.16    | Cut-Thr   | ough Communication (T) 70                                                                                                                                     |    |

|           | 5.4.16.1  | r (Restricted) and l (Local)                                                                                                                                  |    |

|           | 5.4.16.2  | c (Connect Through Switch)                                                                                                                                    |    |

|           |           | o ("Or" Combine)                                                                                                                                              |    |

| 5.4.17    |           | ldressing (L)                                                                                                                                                 |    |

| 31 41 A I |           | $lL (Limited) \dots \dots$                              |    |

|           |           | uL (Unlimited) $\ldots$ 72                                                                                                                                    |    |

|           |           | c (Communication with Local Addressing)                                                                                                                       |    |

| 5 1 19    |           | $\mathbf{R}$ )                                                                                                                                                |    |

| 9.T.10    |           | $d^*R$ (Dimensioned)                                                                                                                                          |    |

|           |           |                                                                                                                                                               |    |

|           | 0.4.10.2  | $m^*R$ (Multi-dimensioned)                                                                                                                                    |    |

| A | Not            | e on Pr          | rototype Porta-SIMD #include Files          | 118   | 5      |

|---|----------------|------------------|---------------------------------------------|-------|--------|

| 8 | $\mathbf{Con}$ | clusion          | l                                           | 113   | 3      |

|   | 1.4            | nost/ F          | L-Allay intellace                           | . 110 | J      |

|   | 7.4            |                  | E Language Design                           |       |        |

|   | 7.3            | rona-a<br>Imper  | ed Language Design                          | . 101 | 9<br>0 |

|   | 7.1<br>7.2     |                  | SIMD Language Design                        |       |        |

| ' | 7.1            |                  | ype Porta-SIMD Implementation               |       | -      |

| 7 | Rea            | ommer            | adations                                    | 109   | a      |

|   |                | 6.3.4            | Overall Performance of Porta-SIMD Prototype | . 10' | l      |

|   |                | 6.3.3            | Parallel Overhead in Porta-SIMD Prototype   |       |        |

|   |                | 6.3.2            | Achievable Efficiency                       |       |        |

|   |                | 6.3.1            | Constant-Bounded Simulation                 |       |        |

|   | 6.3            |                  |                                             |       |        |

|   | 69             | 6.2.7<br>Desfere | Portability of Implementation               |       |        |

|   |                | 6.2.6            | Using Porta-SIMD                            |       |        |

|   |                | 6.2.5            | Example Programs                            |       |        |

|   |                | 6.2.4            | Status                                      |       |        |

|   |                | 6.2.3            | Implementation Difficulties                 |       |        |

|   |                | 6.2.2            | Structure                                   |       |        |

|   |                | 6.2.1            | History                                     |       |        |

|   | 6.2            |                  | SIMD Implementation Results                 |       |        |

|   |                | 6.1.2            | Enforce Architectural Limits                |       | _      |

|   |                | 610              | 6.1.1.2 Many Architectures                  |       | -      |

|   |                |                  | 6.1.1.1 Many Operations                     |       | -      |

|   |                | 6.1.1            | Provide Architectural Features              |       |        |

|   | 6.1            |                  | ements for an Optimally Portable Language   |       |        |

| 6 |                |                  | ting an Optimally Portable Language         | 7:    | -      |

| - | -              |                  |                                             |       | _      |

|   | 5.5            | Potent           | ial Language Enhancements                   |       | 7      |

|   |                |                  | 5.4.22.2 G (Get)                            |       | 7      |

|   |                |                  | 5.4.22.1 rG (Restricted Get)                |       |        |

|   |                | 5.4.22           | Get (G)                                     |       |        |

|   |                | -                | 5.4.21.2 O (Output)                         |       | 7      |

|   |                |                  | 5.4.21.1 dO (Display Output)                |       | 6      |

|   |                | 5.4.21           | Output (O)                                  |       | 6      |

|   |                |                  | 5.4.20.1 I (Input)                          |       | 6      |

|   |                | 5.4.20           | Input (I)                                   |       | 6      |

|   |                |                  | 5.4.19.2 $g^*S$ (Global)                    |       | 6      |

|   |                | 0.1.40           | 5.4.19.1 d*S (Dimensioned)                  | 7     | 6      |

|   |                | 5.4.19           | Scan (S)                                    |       | 5      |

|   |                |                  | 5.4.18.4 Flow Control with "goR"            | 7     | 5      |

|   |                |                  | 5.4.18.3 g*R (Global)                       | 7     | '4     |

# List of Tables

1.

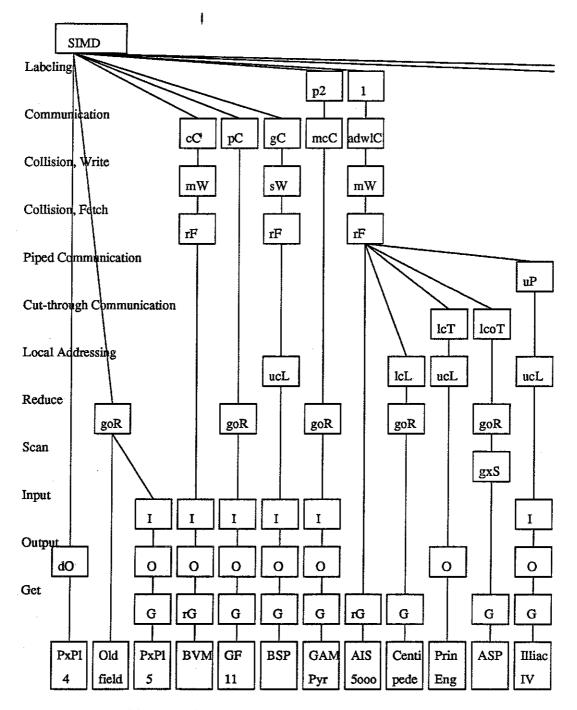

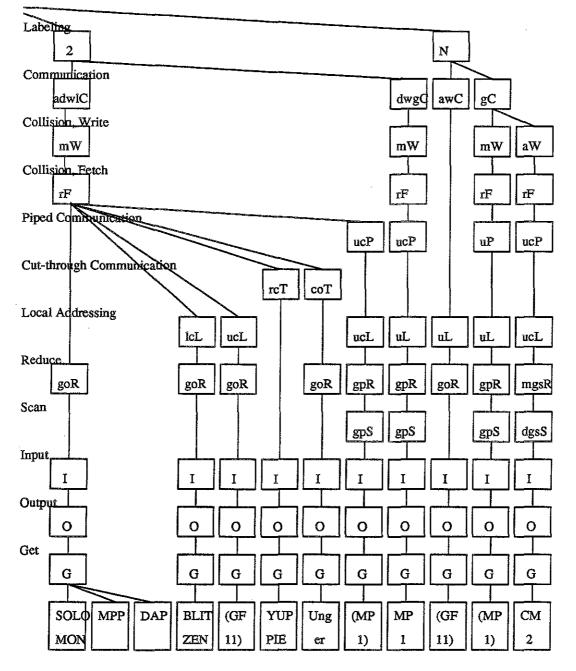

| 3.1        | Communication Features of SIMD Architectures | 15 |

|------------|----------------------------------------------|----|

| <b>3.2</b> | Other Features of SIMD Architectures         | 16 |

| 3.3        | Classification of SIMD Architectures         | 29 |

<u>.</u>....

# List of Figures

| 3.1        | 1-D and 2-D Adjacent Communication Networks                |

|------------|------------------------------------------------------------|

| 3.2        | Examples of Cut-Through Communication                      |

| 3.3        | Tree of SIMD Architectures                                 |

| 3.4        | Tree of SIMD Architectures (cont.)                         |

|            |                                                            |

| 5.1        | rectangle.C — Example Porta-SIMD program                   |

| 5.2        | Fragment of example Porta-SIMD "life" program              |

| 6.1        | julia.C — Julia Set Program (part 1)                       |

| 6.2        | julia.C — Julia Set Program (part 2)                       |

| 6.3        | julia.C — Julia Set Program (part 2)                       |

| 6.4        | julia.C — Julia Set Program (part 4)                       |

| 6.5        | julia.C — Julia Set Program (part 5)                       |

| 6.6        | julia.C — Julia Set Program (part 6)                       |

| 6.7        | life.C — Game of Life Program (part 1)                     |

| 6.8        |                                                            |

| 0.8<br>6.9 | life.C — Game of Life Program (part 2)                     |

|            | life.C — Game of Life Program (part 3)                     |

|            | surface.C — Intensity Axis of Symmetry Program (part 1)    |

|            | surface.C — Intensity Axis of Symmetry Program (part 2)    |

|            | surface.C — Intensity Axis of Symmetry Program (part 3) 97 |

|            | surface.C — Intensity Axis of Symmetry Program (part 4) 98 |

|            | surface.C — Intensity Axis of Symmetry Program (part 5) 99 |

| 6.15       | surface.C — Intensity Axis of Symmetry Program (part 6)    |

| 6.16       | surface.C — Intensity Axis of Symmetry Program (part 7)    |

| 6.17       | surface.C — Intensity Axis of Symmetry Program (part 8)    |

xi

### LIST OF FIGURES

## Chapter 1

## Introduction, Thesis, and Overview

Portable high-level languages for von Neumann computers are major accomplishments in computer science. These languages have radically improved the quality, cost, reliability, and availability of software. However, the greater architectural diversity of SIMD (Single-Instruction Multiple-Data) parallel computers has kept them from fully benefiting from such languages. Each existing SIMD language assumes some particular set of features is available, and is therefore suitable for programming only some subset of SIMD machines. Architectural differences such as communication and local addressing are too important for algorithm selection to be hidden from the programmer in this way. They are too powerful to ignore when available, but too expensive to simulate when not supported in hardware.

Optimal portability is a new language design concept which can bring the benefits of portable high-level languages to architecturally diverse families of computers, including SIMD computers. Here is an informal definition of optimal portability: given a set of architectures, and a taxonomy for those architectures which can be expressed in a tree structure, a language is optimally portable for the set of architectures if: (1) it requires each program to specify at compile time a subtree of the taxonomy as the set of architectures on which it will run; (2) it allows the program to take full advantage of the features common to all the nodes of that subtree; and (3) it prevents the program from using any features not common to all the nodes of that subtree. The full definition adds a key requirement: the taxonomy must consider two nodes, or a node and a computer, equivalent if and only if each can simulate the other with a constant-bounded number of its own operations. This is called the *constant-bounded simulation criterion* within this work.

The basis for optimal portability is recognizing that each algorithm has some inherent range of portability implicitly defined by the operations (or architectural features) it uses. An optimally portable language allows every algorithm appropriate for its set of architectures to be expressed naturally, and to execute on all architectures which support the set of operations used by the algorithm. An optimally portable language provides some consistency checking: it generates an error message if the program uses operations not common to all nodes in the specified subtree of the taxonomy. Finally, the constant-bounded simulation criterion ensures reasonable execution efficiency. In short, an optimally portable language lets the programmer use all the features shared by any specified set of target architectures, while being protected from using features they do not share.

By specifying a broad or narrow set of target architectures, the programmer can select just the right tradeoff between universal portability with limited features and limited portability with more powerful features. The language thereby provides the optimal degree of portability for each program. An additional benefit is that the programmer may use a single language for many architectures instead of having to learn many different languages.

I have developed a taxonomy of SIMD architectures which uses the constant-bounded

simulation criterion. Using it, I designed Porta-SIMD (pronounced "porta-simm'd"), the first optimally portable SIMD programming language. Porta-SIMD provides a set of types corresponding to each point in the taxonomy. These types support exactly the operations appropriate to that point. By declaring the data types of each algorithm's variables, the programmer specifies which operations the algorithm may use. The set of all data types used in a program's declarations determines the program's portability. The program will run on any architecture which supports all the architectural features implied by the set of data types.

Porta-SIMD has been implemented on Pixel-Planes 4 and 5 and the Connection Machine, as well as on a sequential computer simulating parallel architectures.

I am prepared to defend the following thesis statements:

- Optimal portability is an important new concept for handling architectural diversity in programming language design, and is particularly important for SIMD architectures.

- Porta-SIMD is the first optimally portable programming language for SIMD computers. It demonstrates that optimal portability is an achievable goal for SIMD languages.

My argument that these statements are correct has three main parts: analysis, design, and implementation.

The analysis portion of this dissertation contains three chapters. Chapter 2, "Optimal Portability", presents a precise definition of optimal portability, and discusses issues involved in formulating this definition.

None of the existing SIMD taxonomies used the constant-bounded simulation criterion, so I developed one that does. Chapter 8 presents this new taxonomy and discusses previous SIMD taxonomies. It demonstrates the new taxonomy's completeness by using it to characterize a large number of published SIMD architectures. While developing this taxonomy was a necessary step in applying the concept of optimal portability to SIMD language design, the taxonomy is a useful contribution to knowledge in its own right. It is more complete in coverage and comprehensive in scope than previous work, and benefits from the well-defined and defensible level of detail provided by optimal portability's constant-operation simulation criterion.

Despite the wide variety of existing SIMD languages, none are optimally portable. Chapter 4, "Portability of Existing SIMD Languages," surveys existing SIMD languages and shows how each fails to satisfy the definition of optimal portability. The principal way these languages fail is that each language provides only a single set of architectural features for all programs to use. As a result, each language can only be implemented on architectures which support all the features it requires. And if the architecture provides additional features, the language provides no way to take advantage of them. The language determines the degree of portability instead of the programmer, which is the opposite of optimal portability.

The design portion of the dissertation consists of chapter 5, "Porta-SIMD Language Design." It describes the first optimally portable SIMD programming language. Porta-SIMD was designed to show how the concept of optimal portability can be applied to language design. For convenience, Porta-SIMD is an extension of C++. Porta-SIMD provides parallel data types with an additional characteristic included in the type: the set of architectural features available for using and manipulating data of that type. Because these features are those defined by the taxonomy of chapter 3, this allows the program to specify exactly which features are used by each algorithm and each program. The implementation provides type checking to ensure that features not specified by an object's type are not used with that object.

The primary argument in support of the dissertation's thesis concludes with chapter 6, "Implementing an Optimally Portable Language". Just as the design of Porta-SIMD was undertaken to demonstrate the value and applicability of optimal portability, a prototype implementation of Porta-SIMD was done to demonstrate the completeness and usefulness of the language design.

This chapter describes the requirements an implementation of any optimally portable language must meet, then moves on to the specific prototype implementation of Porta-SIMD. Because Porta-SIMD's implementation is intended as a proof-of-concept tool, it has been done as a set of libraries and **#include** files for use with an unmodified C++compiler. Despite some limitations, C++ was the right tool for this stage of the research, allowing successively more complete prototypes on a wide variety of platforms. Writing a full optimizing compiler for Porta-SIMD would have been inappropriate for this work, and impossible with the resources available.

Porta-SIMD has been implemented for the Connection Machine, Pixel-Planes 4, the Pixel-Planes 5 simulator (hardware was not yet available), and sequential computers simulating SIMD architectures. In addition to describing the Porta-SIMD implementation, chapter 6 presents some example Porta-SIMD programs. It goes on to discuss the performance of this multi-targeted implementation and potential future implementations, using both analytic methods and actual measurements based on the example programs. There is no reason to believe that a compiler for an optimally portable language cannot provide performance comparable to other languages which are not optimally portable but have equivalent features otherwise. The price of the portability appears to be paid entirely in compile time. However, using the *prototype* Porta-SIMD implementation, programs run up to 10 times slower than using machine-specific SIMD languages, and potentially use 50

Chapter 7, "Recommendations," follows the formal argument in support of the thesis. It presents opportunities for future research and my personal view of how the concept of optimal portability should influence existing and future SIMD languages. It begins with opportunities related specifically to the prototype implementation of Porta-SIMD, and the Porta-SIMD language design. This leads to a discussion of improved optimally portable languages, and other characteristics I consider important for SIMD languages. Finally, I discuss the interface between the host and the PEs. It can be improved through both hardware architecture and compiler technology.

Finally, chapter 8, "Conclusions," summarizes the results of this research. Optimal portability appears to be a clarifying concept for handling architectural diversity. Its application in Porta-SIMD provides a new mode of portability for SIMD languages, and demonstrates that such portability is achievable in practice. The requirements of optimal portability contributed to the development of a SIMD taxonomy in which equivalence is defined by constant-bounded simulation. This taxonomy consequently has many dimensions of equivalence-versus-difference.

I hope this work will have a strong influence on future SIMD languages, and that optimally portable languages will bring more, cheaper, and better software to all SIMD architectures.

## Chapter 2

## **Optimal Portability**

An optimally portable language allows a programmer to write code which is exactly as portable as the algorithm being coded. This is the optimal degree of portability: exactly what is needed for each situation. Defining this level of portability, and making it available in a SIMD programming language, is the key contribution of this dissertation.

In contrast to optimal portability, existing SIMD languages artificially restrict or extend portability. Some restrict portability by requiring specific architectural features (e.g., arbitrary global communication) to be present whether they are used or not. Some extend portability by not allowing the use of some architectural features. They thereby ban efficient execution of some algorithms. Most do both.

Of course, designing and implementing an optimally portable language requires a precise definition of optimal portability. This chapter presents and justifies that definition. A key feature of this definition is the strict lower bound it places on execution efficiency. This bound ensures that optimally portable languages provide useful portability, not just theoretical portability. Succeeding chapters demonstrate this definition's value by applying it to existing languages, and to the design and implementation of an example language.

Optimal portability is best defined using operations on sets of abstract architectures. Blaauw and Brooks define the *architecture* of a computer as "a minimal behavioral specification," and distinguish it from the implementation and realization. [BlaauwBroo90] Specifically, variable quantities such as the number of processors in a parallel computer and the amount of memory per processor are not specified by the architecture. They are details of the hardware realization. Within this work, I define an *abstract architecture* to be the set of data types and operations provided by a computer's architecture, without regard to how the data and operations are represented. Every data type is assumed to have a fixed size which is the same in all the processors of a system. Except where explicitly stated otherwise, I use *architecture* as a synonym for abstract architecture. Where I need to distinguish abstract architecture. The operations and data types of an architecture are collectively referred to as the architecture's *features*, another synonym for abstract architecture.

Language definitions share many characteristics with architectures (which are themselves machine languages). Languages are implemented by compilers and interpreters. Dealing with an abstract (as opposed to a detailed) architecture gives the degree of portability found in most sequential languages, such as C and Fortran. These languages provide portability only between closely related architectures following the von Neumann model. [Dasgupta89, pp. 103–108] Note that languages do not impose limits on architectural variables. But the implementation of a language may fail to execute a program which is perfectly legal according to the language, if some resource (e.g., memory) is exhausted during its execution.

The members of a set of architectures are equivalent if and only if their intersection is identical

to their union. The union of a set of architectures is an architecture containing all data types and operations contained in any member of the set. The definition of intersection is more complicated, and introduces key elements in the overall definition of optimal portability. The point of the two-step construction of a set's intersection is to synthesize the most powerful architecture which can be simulated efficiently by all members of the set. The *intersection* of a set S of architectures is an architecture constructed as follows:

- 1. Let architecture u be the union of S. To each member  $A_i$  of S add each data type and operation in u which  $A_i$  can simulate with a constant number of its own data elements and operations.

- 2. Take the intersection of the sets of data types and operations of all members of S, as augmented by the previous step, to create the intersection architecture.

The intersection of a set of architectures will also be called the *shared architecture* of the set. The first step in constructing a set's intersection expands each member architecture to include all the features it can simulate efficiently. Then the second step can recognize the features shared by all members, even if they were initially expressed differently. The two most important parts of the definition of intersection are the phrases "number of ...data elements and operations" and "constant." These phrases address the issue of efficiency.

First, the number of operations and data elements is measured, not time (in clock cycles or milliseconds) or space (in processor word size, bits of memory, logic elements, or silicon area). Measures of time and space apply to implementations and realizations, not architectures. Architectures have operations and data elements; simulation efficiency is measured by counting these. The dynamic number of operations executed is counted, not the static number written in an algorithm or the number of distinct types used. This corresponds to the implementation concept of execution time, rather than code size or instruction set size. Data elements are counted by the high-water mark, or the maximum number ever allocated simultaneously. In implementation terms, this would be the amount of memory required to execute the code.

The second phrase, "constant," introduces the constant-bounded simulation criterion which is used to distinguish architectures and their features. Constant-bounded simulation is the simulation by some architecture of one or more architectural features, using only a constant number of the architecture's operations and data elements. Any Turing-equivalent machine can simulate any architecture, but not always with useful performance. The constantbounded criterion provides a tight bound on simulation overhead. It also fits well with intuitive notions of equivalent architectures, by making equivalence transitive. If architecture  $A_i$  can do a constant-bounded simulation of  $A_j$ , and  $A_j$  can likewise simulate  $A_k$ , then  $A_i$  can also do a constant-bounded simulation of  $A_k$ . Though the simulation of  $A_k$  by  $A_i$ may be a two-level process that multiplies the constants of the two levels, the product of any finite set of constant-bounded numbers is also constant-bounded. It will be shown in chapter 3 that the set of distinct features of SIMD architectures is finite.

A looser bound on simulation for defining equivalent architectures, such as a logarithmic or polynomial bound in the amount of memory or number of processors, would not allow equivalence to be transitive. A tighter bound, such as a limit on the constants allowed in constant-bounded simulation, would be arbitrary. It would also be meaningless in the face of large constant-factor differences in execution times for identical features on different implementations.

The result of the definition of a set of equivalent architectures is that any member of the set can simulate any other member, and the number of native operations they execute will be within a constant factor of each other.

An architecture *supports* a language feature (which may be an operation, statement type, data type, standard library function, or other construct) if and only if the language feature can

be implemented with a constant number of the architecture's operations and data elements. A set of language features *provides access to* (or *provides*) an architectural feature if and only if it enables a program to express within a constant-bounded number of symbols all computations performable by a single use of the architectural feature. A program is *portable* across a set S of architectures if and only if it uses only language features supported by the shared architecture of S. The *target architecture* of a program is an architecture across which the program declares it is portable.

A programming language L is *optimally portable* for a set S of architectures if and only if all of the following are true:

- L requires each program p to declare some architecture A<sub>p</sub> ∈ S as its target architecture. (A default target architecture may be implicitly specified in the absence of an explicit specification.)

- L does not allow p to use any language feature not supported by  $A_p$ .

- L provides all architectural features in  $A_p$ , and allows p to use any language feature supported by  $A_p$ .

By satisfying this definition, an optimally portable language gives p exactly the portability and power implied by its architectural assumptions, as embodied in its target architecture  $A_p$ . As a result, p is as portable as possible without changing its architectural assumptions. Of course, if p has specified a target architecture supporting architectural features it actually does not use, then p can be made more portable simply by specifying a target architecture which more precisely reflects the program's intrinsic portability. The definition implies that p is portable across any set  $S_1 \subseteq S$  such that  $A_p$  is the shared architecture of  $S_1$ , including the maximal such set,  $S_p$ . Therefore, p cannot be portable across a larger set of architectures without giving up the use of one or more data types or operations. (But if p does not actually use all the features in its target architecture gives p its full intrinsic portability without otherwise changing the program.) In addition, p cannot use additional data types or operations without adding to  $A_p$ . If the augmented architecture were not equivalent to  $A_p$ , this would reduce p's portability by removing architectures from  $S_p$ . If it were equivalent, it would not increase the power available to p.

It is important that optimally portable languages are not allowed to provide language features not supported by the target architecture. Providing such features would require the compiler to generate code which uses arbitrary data elements and operations to simulate the unsupported features. That would destroy the constant-bounded execution guarantee for language features.

Prohibiting compilers from simulating data types and operations not supported by the target architecture helps ensure portability with useful performance, not just theoretical portability. This does not restrict the function of programs, since a program may simulate such data types and operations itself. The implementers of a language may even provide, as a convenience to programmers, an optional library to do this simulation.

The definitions given so far ensure constant-bounded execution overhead from language features down through abstract architectures. However, this performance guarantee is meaningless without a similar assurance concerning execution overhead in implementing the architecture. A particular computer must be considered to *implement* only a single set of equivalent architectures. This set must be the set of architectures equivalent to the architecture defined by the computer's lowest-level publicly documented programming interface. This definition says that every computer implements a single architecture, and specifies how to determine the definition of that architecture. In some cases, a single machine may be reasonably described by two or more quite different abstract architectures. As long as they are equivalent, they are equally valid descriptions. For example, a bit-serial SIMD machine may be described as having operations on bits, on multi-bit integers, or on floating-point numbers. Operations on the multi-bit data types can be simulated by a constant number of bit-serial operations. The constant (which may be over 1000) depends on the nature and size (in bits) of the simulated data type, but does not depend on the values stored in data elements of that type. The architectures are equivalent. This is consistent with the common practice of building implementations of a single architecture with varying execution speeds.

Another example is a SIMD machine with a 2-dimensional grid interconnection network which allows communication in parallel between pairs of adjacent PEs (Processing Elements), using its lowest-level publicly documented programming interface. With an additional layer of software to do automatic routing, the machine might also be described as providing communication between arbitrary pairs of PEs. The number of operations required to simulate arbitrary communication with this 2-D grid depends heavily on the dynamically chosen communication pattern. A lower bound for the worst case is the diameter of the network, which is at least the square root of the number of PEs. Since a SIMD architecture does not specify a maximum number of PEs, this is not a constant bound. Therefore, the two descriptions are not equivalent, and only the first is part of a valid abstract architecture for this machine. However, if the automatic routing software were hidden beneath the lowest-level publicly documented programming interface, the architecture would be considered by the above definitions to provide communication between arbitrary pairs of PEs.

For most sequential computers, the lowest-level publicly documented programming interface is assembly language. For some SIMD computers it is a library, or even a high-level language and its standard library. For example, on the Connection Machine the lowest-level publicly documented programming interface is Paris, a library callable from several sequential languages. On the MasPar MP-1, it is MPL (which is C with simple parallel extensions) and its standard library.

There are several reasons to define a machine's architecture by its lowest-level publicly documented programming interface, rather than by its hardware. A programmer has no access to the hardware except through this interface, so a language which provides features equivalent to this interface is neither hiding features from nor inventing features for the programmer. Hardware documentation is not always publicly available. When it is, it is often less complete and precise than the programming interface, largely because programming interfaces must be well documented in order for important software to be developed. Machine builders are free to implement, transparently to the programmer, a single architecture with different hardware designs. These identically programmed machines should be considered by languages to have the same architecture.

Although I believe this is the best available method for defining a computer's architecture, it leads to some apparent contradictions. For example, the CM-2 (Connection Machine, model 2) and MP-1 both define global reduction and parallel prefix computations as single operations. This is despite the fact that any implementation using pairwise operations (which they in fact use) must take  $O(\log_2 n)$  steps when there are n PEs. Arbitrary global inter-PE communication is another example. Both the CM-2 and the MP-1 implement this operation with an iterative procedure, the number of iterations of which is not bounded by a constant with respect to the number of PEs. Even sequential machines have a slight non-constant element to their implementation; memory access with address decoding is theoretically logarithmic in the size of the address space (linear in the number of address bits). However, the architects and implementers of these machines, and those of all the languages designed and implemented for them, concur that these features should be considered part of the programming model. They are powerful abstractions, and can be implemented reasonably efficiently with a combination of hardware and firmware. Defining these machines' architectures by their lowest-level publicly documented programming interface captures this collective judgement, which further supports the use of this definition.

The definition of optimal portability allows a strong statement to be made about the efficiency of optimally portable languages: every language feature available on a particular computer is implementable with a constant number of operations and data elements at the computer's lowest-level publicly documented programming interface. This is as strong a statement of efficiency as any portable language can make. Anything stronger would require knowledge of implementations, which is beyond the scope of language definitions.

### Chapter 3

## A SIMD Taxonomy for Optimal Portability

While the architectural differences between sequential (not vector) computers are significant to cost and performance, it is very rare for them to influence algorithms in application programs. This is because purely sequential computers share the von Neumann model of architecture, and are equivalent by the definition in chapter 2. Therefore, sequential languages are optimally portable by that chapter's definition.

In contrast, the family of SIMD architectures is large and diverse. SIMD architectures aim to apply unmatched computational power to suitable problems. They do this by replicating the essential processing elements abundantly and distributing the data store among them, without also duplicating the instruction fetch and decode, flow control, and code store components. But choosing the precise set of features to replicate in each PE, and the network by which PEs exchange data, involves trade-offs between power and cost per PE. There is no single "right" set of trade-offs which is best for all applications, since applications vary in the benefit they derive from each feature. This is the source of the architectural diversity which makes optimally portable SIMD languages necessary and non-trivial.

A programming language can be optimally portable only for a specific set of architectures. That set must be well defined, so a definition of SIMD architectures is presented in section 3.1. The architectural features within the set must be identified and distinguished using the constant-bounded simulation criterion. I have developed a new SIMD taxonomy which does exactly that; it is presented in section 3.2. Section 3.3 demonstrates this taxonomy by using it to classify some important existing SIMD architectures. For the purpose of this classification, each SIMD computer is considered to implement the architecture defined by its lowest-level publicly documented programming interface. This is required by the definition of optimal portability. Finally, section 3.4 reviews some existing taxonomies and discusses why none of them is a suitable basis for designing an optimally portable language. They are discussed at the end of the chapter primarily so the vocabulary of architectures and architectural features developed in the rest of the chapter can be used in the discussion.

### 3.1 Definition of SIMD Architectures

An architecture A is a SIMD architecture if and only if all of the following are true:

- A has a host computer which handles ordinary scalar computations and flow control, and which broadcasts instructions, one at a time, to all PEs (Processing Elements).

- A has n > 1 identical PEs which each execute, simultaneously, each instruction broadcast by the host.

- Each PE is able to evaluate basic arithmetic and logical expressions.

I believe every useful SIMD architecture also has the following properties:

- 1. Each PE is able, in response to broadcast instructions, to independently choose whether to ignore instructions to modify its memory. (PEs executing all instructions are *enabled*, while those ignoring instructions to modify memory are *disabled*. PEs can be considered to have an *enable-bit* which is 1 only in enabled PEs.)

- 2. Each PE is able to compute its unique PE number  $0 \le p \le n-1$ .

- 3. Each PE has its own private memory.

Property 1 can be simulated with a constant number of ordinary arithmetic and logical operations. Architectures that do not have this property are therefore equivalent to those that do, and can be considered to have it. This property takes many different but equivalent forms in various machines, with it being possible to ignore different subsets of the instruction set.

Property 2 holds for every architecture which can, by any means, load into each PE a different member of a set of distinct values. To see this, consider the set of PE numbers as the data to be loaded. If there is a SIMD architecture which does not have this property, I do not think it is very interesting because the PEs cannot be given unique predetermined data on which to operate.

The only claimed exception to property 3, that I am aware of, is an alternative set of architectures where PEs access a global memory space through a network of some kind (cf., [HwangBrigg84, pp. 326-327]). I believe that any such architecture is equivalent to a local-memory architecture in which the PEs are connected to each other by the same network that connects the PEs to the global memory.

Specifically, the BSP (Burroughs Scientific Processor, section 3.3.18) is the only non-local memory architecture I know of. It is equivalent to a large subset of the CM (Connection Machine, section 3.3.20) architecture. (Both architectures are discussed briefly in section 3.3.) The BSP can simulate the CM's local memory model simply by assigning a distinct portion of global memory to each PE for private use, and accessing memory assigned to other PEs only to simulate communication. Similarly, the CM can simulate the BSP's global memory model by using its communication primitives to access memory, treating all the private memory as a single global memory space. Both are constant-bounded simulations, so the BSP's global memory and arbitrary PE to memory interconnection network is equivalent to the CM's local memory and a subset of its communication primitives. The only difference between the memory and communication systems of the architectures is that the CM has more powerful mechanisms for resolving multiple simultaneous writes to a single memory location.

If any of these properties is not true of all SIMD architectures, then the taxonomy of the next section is considered to have an additional feature for each such property. Because all architectures currently classified by this taxonomy have all these features, they will not be mentioned further.

#### 3.2 Taxonomy of SIMD Architectures

This section presents a new taxonomy of the diverse architectures that exist within the definition of SIMD just presented. The taxonomy's purpose is to provide a basis for designing optimally portable SIMD languages. Therefore, its criterion for distinguishing architectural features from one another is constant-bounded simulation.

Of course, some of the constant factors ignored by this criterion are important for other purposes. Designers of SIMD machines must decide not only which features to implement,

#### 3.2. TAXONOMY OF SIMD|ARCHITECTURES

but also how much hardware to devote to minimizing each constant. Constant factors can also be important to users choosing the best machine on which to run a program. But these constants reflect the performance of an implementation, not the suitability of an algorithm to an architecture. So this taxonomy appropriately ignores them.

The taxonomy presented here is reasonably comprehensive, but not exhaustive. No static SIMD taxonomy could remain exhaustive in any case, since new architectural features can always be invented. All that is needed is to propose implementing as a single operation some computation which cannot be implemented by existing architectures using constantbounded simulation.

Communication networks are a good example of this. There is an infinite number of communication networks which are not equivalent (by the constant-bounded simulation criterion). A finite taxonomy cannot describe them all. Fortunately, the set of communication networks and other architectural features proposed in the literature is much more manageable. There are many common features and similarities, which makes it possible to describe most proposed architectures as combinations and variations of a few important architectural concepts.

The taxonomy presented here is intended to classify architectures which have been implemented or proposed in the literature. It is not intended to classify all conceivable architectures, or even all architectures obtainable by combining the features of proposed architectures in new ways. Where several architectures are sufficiently similar, I have sought to generalize the similar features and provide a unifying classification. For example, my description of cut-through communication is more general than connection autonomy as proposed by Maresca and Li [MarescaLi88, MarescaLi89]. I believe I am the first to identify the segmented communication bus architectures of the Princeton Engine (section 3.3.6 and ASP (Associative String Processor, section 3.3.7) as special 1-D cases of connection autonomy, and the first to integrate the communication capabilities of Unger's architecture (section 3.3.14) into a more general framework.

Some less common architectural features have not been used enough to suggest which possible generalizations are most useful. In particular, where pairs of features that might interact have never been proposed as part of the same architecture, I have not attempted to define what their interactions might be.

The taxonomy presented here classifies an architecture as a set of architectural features. A classification contains at most one feature chosen from each of 12 feature categories. The categories are grouped and named as follows. The groups are in order of decreasing significance for most algorithm selection tasks.

Communication:

Labeling (number, N) Communication (C) Collision Resolution, Write (W) Collision Resolution, Fetch (F) Piped Communication (P) Cut-Through Communication (T) Local Addressing: Local Addressing (L) Reducing and Scanning: Reduce (R) Scan (S) Parallel I/O: Input (I) Output (O) PE to Host I/O: Get (G)

The items in parentheses identify the categories.

The sections that follow describe the naming of architectural features, and the features in each category. In some cases, a feature or set of features can perform a constant-bounded simulation of some other feature. The simulating feature or set of features is then said to *subsume* the simulated feature. This is mentioned where it is particularly important or common. Tables 3.1 (p. 15) and 3.2 (p. 16) summarize the features in each category.

#### 3.2.1 Feature Names

Every feature has a name. A feature name consists of a number or an upper-case letter, optionally preceded by one or more lower-case letters. The upper-case letter identifies the category the feature is part of. Most categories have a unique letter which is the final (upper-case) letter of all its feature names. The single exception is "labeling"; it is the only category which uses numbers in feature names.

Several related features are sometimes named and described as variations of a single base feature. (E.g., adjacent communication has variations both with and without diagonal connections, wrap-around edges, and local communication.) In such cases, the base feature is named and described. Then each of a set of modifiers of that base feature is named and described. Rules are given describing the legal combinations of modifiers. Finally, each legal variation obtainable from the modifiers and combining rules is named.

The name of a variation always begins with the name of the base feature, minus the final letter. This is followed by the letters for all its modifiers, in the order the modifiers are described in the taxonomy. The final letter of the base feature completes the name of the derived feature.

In a few cases, there is no base feature because at least one modifier is required by all variations. Where this is true, a pseudo-base feature is given which has an asterisk (\*) in its name. The asterisk must be replaced by one or more modifiers to create a legal feature name. For example, the global reduction pseudo-base feature g\*R has modifiers f, o, x, m, s, and p. These represent the features gfR, goR, gxR, gmR, gsR, and gpR.

#### 3.2.2 Communication

Interprocessor communication is a very important characteristic of SIMD architectures. It is the area of SIMD architecture which exhibits the most diversity. The primary determinant of an architecture's communication capabilities is the network used to connect the processors. A cartesian grid with one or two dimensions is most common, but complete graphs and other networks have also been proposed and used. The "labeling" and "communication" feature categories define the basic interprocessor communication network.

These categories make no pretense of describing all the possible communication networks that could be used in SIMD architectures. There is an infinite number of such networks, and a tremendous body of literature describing them. (Two good surveys are [WuFeng84, Siegel85].) This taxonomy only attempts to describe interconnection networks which have been used or proposed as part of a SIMD architecture. Obviously, more features will be added to the "labeling" and "communication" categories as new SIMD architectures use additional interconnection networks.

In some architectures, each PE is able to independently choose with which one of several (or many) other PEs it will communicate. This raises the possibility that some PE will be

#### Communication

Labeling (number, N)

- **1** 1-D cartesian coordinate.

- 2 2-D cartesian coordinate.

- ... Any fixed-dimension cartesian coordinate.

- N N-D cartesian coordinate.

- p2 3-tuple: level number and 2-D cartesian coordinate.

#### Communication (C)

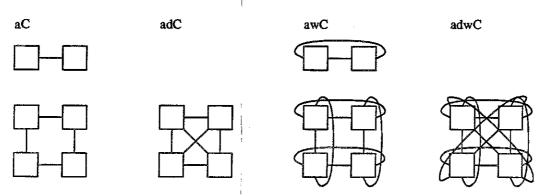

- aC Adjacent communication.

- d Diagonal.

- w Wrap.

- l Local.

- mC Pyramid of 2-D grids, adjacent communication.

- c Count.

- cC Cube Connected Cycles communication.

- pC Preselected set of permutations.

- gC Global communication.

#### Collision Resolution, Write (W)

- sW Select.

- IW Logically combine (and, or, xor).

- aW Add, or take maximum or minimum.

- **mW** Multiply.

#### Collision Resolution, Fetch (F)

- sF Select.

- rF Replicate.

#### Piped Communication (P)

- P Pipe.

- u Unrestricted pipe.

- c Copy pipe.

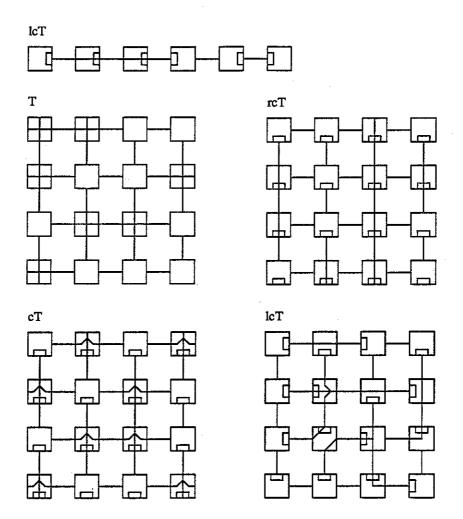

#### Cut-Through Communication (T)

- **T** Cut-through communication.

- r Restrict the switch.

- **1** Program switch locally.

- c Connect through switch.

- o "Or" together multiple values.

Table 3.1: Communication Features of SIMD Architectures. Summary of the communication group of features described in section 3.2.2, shown by category.

#### Local Addressing

#### Local Addressing (L)

- 1L Limited local addressing.

- uL Unlimited local addressing.

- c Local addressing during communication.

#### **Reducing and Scanning**

- f First.

- o Or, and.

- x Xor.

- m Max, Min, f.

- s Sum (add), m, x, o.

- **p** Product (multiply), s.

#### Reduce (R)

d\*R Reduce along one dimension.

m\*R Reduce along multiple dimensions.

$g^*R$  Global reduction.

#### Scan (S)

d\*S Scan along a dimension.

g\*S Global scan.

#### Parallel I/O

Input (I)

I Parallel input.

#### Output (0)

dO Parallel output, write-only (display).

O Parallel ouput.

#### PE to Host I/O

Get (G)

- rG Restricted get.

- G Get.

Table 3.2: Other Features of SIMD Architectures. Summary of non-communication features described in sections 3.2.3-3.2.6, shown by group and category.

#### 3.2. TAXONOMY OF SIMD ARCHITECTURES

selected as the communication partner of more than one other PE. How such communication collisions are resolved is determined by the "write" and "fetch" feature categories.

"Piped communication" extends ordinary grid communication by allowing PEs to communicate with PEs which are a fixed distance and direction away, but the distance is greater than one.