©1992 Suresh Rajgopal ALL RIGHTS RESERVED SURESH RAJGOPAL. Spatial Entropy – A Unified Attribute to Model Dynamic Communication in VLSI Circuits (Under the direction of Kye S. Hedlund and Akhilesh Tyagi)

### Abstract

This dissertation addresses the problem of capturing the dynamic communication in VLSI circuits. There are several CAD problems where attributes that combine behavior and structure are needed, or when function behavior is too complex and is best captured through some attribute in the implementation. Examples include, timing analysis, logic synthesis, dynamic power estimation, and variable ordering for binary decision diagrams (BDDs). In such a situation, using static attributes computed from the structure of the implementation is not always helpful. Firstly, they do not provide sufficient usage information, and secondly they tend to exhibit variances with implementations which is not desirable while capturing function behavior.

The contribution of this research is a new circuit attribute called *spatial entropy*. It models the dynamic communication effort in the circuit by unifying the static structure and the dynamic data usage. Quantitatively, spatial entropy measures the switching energy in a physical (CMOS) implementation. A minimum spatial entropy implementation is a minimum energy implementation. For the purposes of this dissertation we restrict our scope to combinational circuits. We propose a simple procedure to estimate spatial entropy in a gate level circuit. It is characterized in extensive detail and we describe why it is difficult to compute spatial entropy accurately. We show how it can also be defined at other levels of abstraction.

We illustrate applications of spatial entropy in BDD variable ordering, a problem that has traditionally relied on static attribute based solutions. We also show empirically that spatial entropy can track function behavior through implementations, by using it to measure gate-count complexity in boolean functions.

### Acknowledgments

I would like to take this opportunity to express my sincere gratitude towards my advisor Kye Hedlund and co-advisor Akhilesh Tyagi. This research would have been impossible without their advice, encouragement and guidance. I would like to thank them for the time that they have spent with me and the hours of discussions that we have had. Their comments and suggestions have gone a long way in helping me produce a comprehensive dissertation. They have taught me the essence of patience in research and the need to present ideas clearly and simply. Doing research under them has been exciting and challenging.

I am indebted to my committee member Doug Reeves whose advice and comments helped me keep this research in perspective. I gratefully acknowledge his patience, encouragement and willingness to help. I would also like to thank Don Stanat and David Plaisted for serving on my committee and for their suggestions and encouragement. I appreciate the assistance of Sujit Dey (of NEC Research Labs, Princeton) and Kris Kozminski of the OASIS group at MCNC during this research.

I am grateful to Yuki Watanabe for his support throughout my stay at UNC. I would also like to thank Peter Reintjes of DASIX/Intergraph for his help and encouragement during my graduate career, and my office mates at UNC, Jim Symon and Don Stone for making the department a better place to live/work in.

Finally, I would like to thank my wife Uju for her endless patience and support. Her strength and encouragement have been invaluable during hard times.

# Contents

| 1 | Inti | oduction                             | 1  |

|---|------|--------------------------------------|----|

|   | 1.1  | Overview                             | 2  |

|   | 1.2  | Motivation                           | 5  |

|   | 1.3  | Thesis                               | 7  |

|   | 1.4  | Research Contributions               | 9  |

|   | 1.5  |                                      | 12 |

| 2 | Rel  | ated Work 1                          | 4  |

|   | 2.1  | Static and Dynamic Attributes        | 14 |

|   | 2.2  |                                      | 17 |

|   | 2.3  |                                      | 18 |

|   |      |                                      | 18 |

|   |      |                                      | 20 |

|   |      |                                      | 21 |

| 3 | Spa  | tial Entropy - A Circuit Attribute 2 | 23 |

|   | 3.1  |                                      | 24 |

|   | 3.2  |                                      | 28 |

|   | 3.3  | 1 17 1                               | 32 |

|   | 3.4  |                                      | 35 |

|   | 3.5  | 1 10                                 | 40 |

|   |      |                                      | 40 |

|   |      |                                      | 41 |

|   |      |                                      | 15 |

| 4 | Spa  | tial Entropy Based BDD Ordering 5    | 66 |

| • | 4.1  |                                      | 56 |

|          |     | 4.1.1 Binary Decision Diagrams                      | 57  |

|----------|-----|-----------------------------------------------------|-----|

|          |     | 4.1.2 The Variable Ordering Problem                 | 59  |

|          |     | 4.1.3 Motivation                                    | 62  |

|          | 4.2 | Variable Ordering using Spatial Entropy             | 64  |

|          | 4.3 | Experiment: Objectives and Criteria                 | 71  |

|          |     | 4.3.1 Assumptions and Limitations                   | 71  |

|          |     | 4.3.2 Data Set                                      | 78  |

|          | 4.4 | Experiment Outline                                  | 82  |

|          |     | 4.4.1 Software Construction and Variables Measured  | 82  |

|          | 4.5 | Results and Observations                            | 84  |

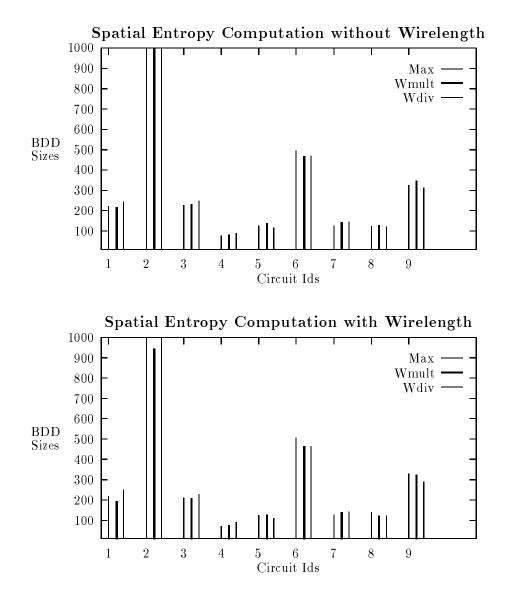

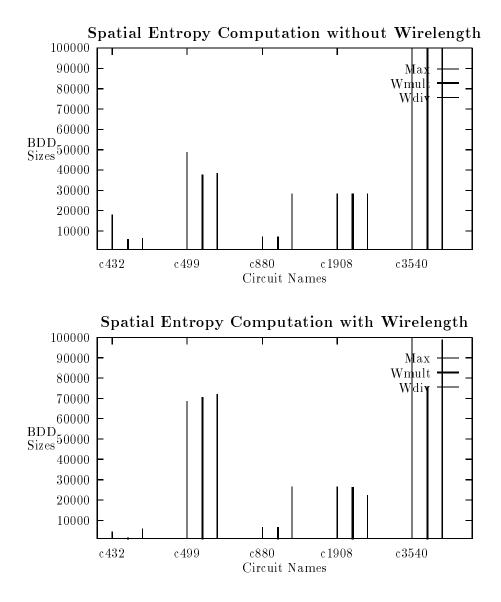

|          |     | 4.5.1 Spatial Entropy and BDD Sizes                 | 84  |

|          |     | 4.5.2 Spatial Entropy Approximations and BDD Sizes  | 91  |

|          |     | 4.5.3 Spatial Entropy Vector Combination Strategies | 107 |

|          | 4.6 | Conclusions                                         | 112 |

| <b>5</b> | Spa | tial Entropy as a Measure of Area-Complexity        | 115 |

| °.       | 5.1 | Motivation                                          | 116 |

|          | 5.2 | Background                                          | 118 |

|          | 0.1 | 5.2.1 Definitions                                   | 118 |

|          | 5.3 | Information Content                                 | 121 |

|          |     | 5.3.1 $k$ -decomposition and Two-level Minimization | 124 |

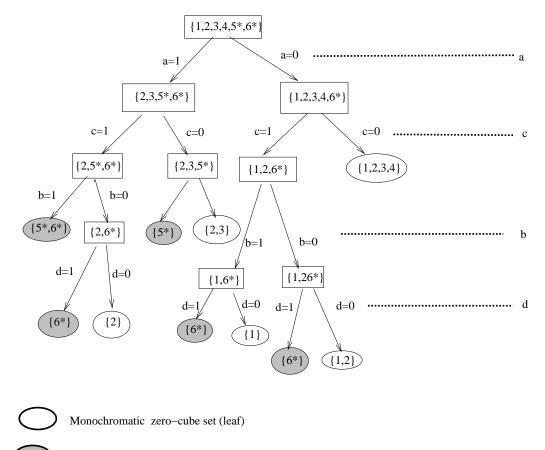

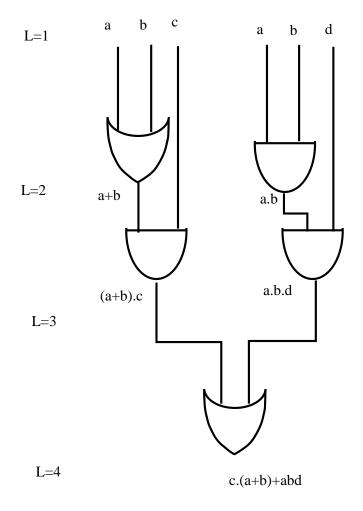

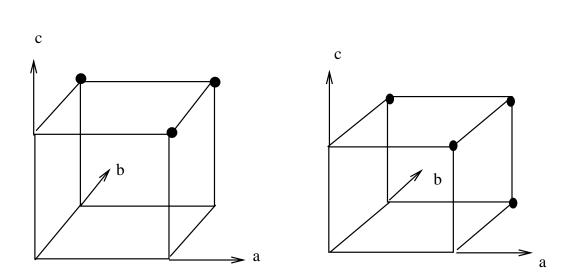

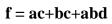

|          | 5.4 | Decision Tree                                       | 132 |

|          | 5.5 | Spatial Entropy and Information Content             | 149 |

|          | 5.6 | Experiment                                          | 155 |

|          |     | 5.6.1 Assumptions                                   | 156 |

|          |     | 5.6.2 Data Set $\ldots$                             | 158 |

|          | 5.7 | Experiment Outline                                  | 158 |

|          | 5.8 | Results and Observations                            | 164 |

|          |     | 5.8.1 Results                                       | 164 |

|          |     | 5.8.2 Observations                                  | 164 |

|          | 5.9 | Conclusions                                         | 176 |

| 6        | Cor | nclusions                                           | 179 |

|          | 6.1 | Summary                                             | 179 |

|          | 6.2 | Future Research Directions                          | 182 |

|          | Bib | liography                                           | 184 |

|          | ~   |                                                     |     |

# List of Tables

| 4.1  | ISCAS 85 Benchmark Circuit Characteristics                                         | 79 |

|------|------------------------------------------------------------------------------------|----|

| 4.2  | Multi-level Circuit Characteristics from Logic Synthesis 91                        |    |

|      | Benchmarks                                                                         | 80 |

| 4.3  | Two-level Circuit Characteristics of Logic Synthesis 91 Bench-                     |    |

|      | marks                                                                              | 80 |

| 4.4  | OASIS generated Structured Circuit Characteristics                                 | 81 |

| 4.5  | Comparative BDD sizes for Logic Synthesis 91 Benchmarks .                          | 86 |

| 4.6  | Comparative Statistics for Logic Synthesis 91 Benchmarks                           | 86 |

| 4.7  | BDD sizes for Logic Synthesis 91 Benchmarks relative to asy190                     | 88 |

| 4.8  | Comparative BDD sizes for ISCAS 85 Benchmarks                                      | 89 |

| 4.9  | Spatial entropy based ordering vs static-attribute based ap-                       |    |

|      | proaches                                                                           | 91 |

| 4.10 | Normalized Mean and Standard Deviation of sizes for IS-                            |    |

|      | CAS85 Benchmarks                                                                   | 92 |

| 4.11 | BDD Sizes for OASIS-generated circuits                                             | 93 |

| 4.12 | Mean and Standard Deviation of sizes for OASIS-generated                           |    |

|      | circuits                                                                           | 93 |

| 4.13 | Percentage improvement for OASIS circuits with wire length                         | 94 |

| 4.14 | Effect of wire length and the SIS scripts on the Logic Synthesis                   |    |

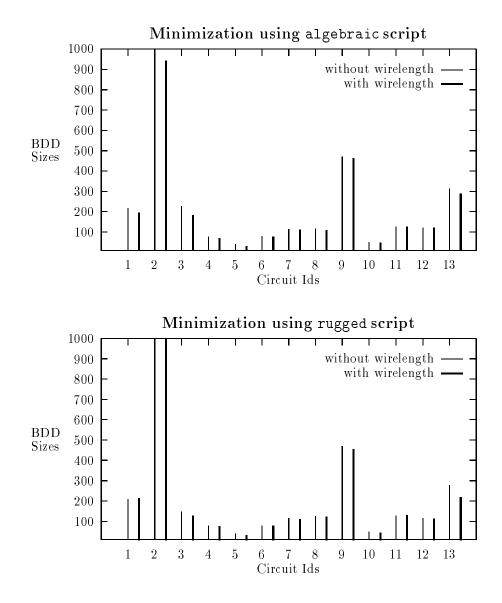

|      | Benchmarks                                                                         | 97 |

| 4.15 | $\overline{ V }$ and $\sigma$ of sizes for Logic Synthesis 91 circuits (with mini- |    |

|      | mization and w/l approximations)                                                   | 98 |

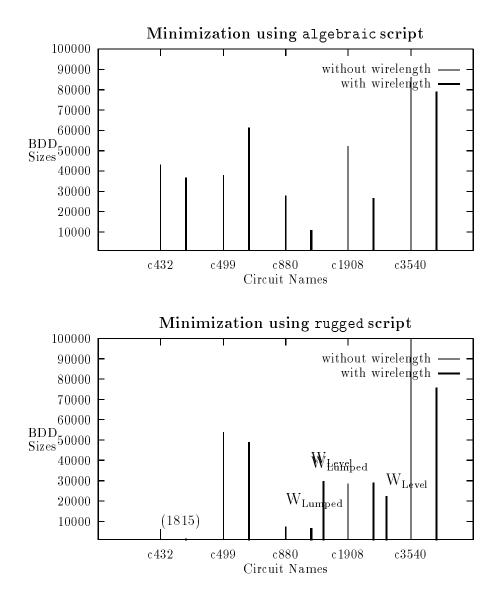

| 4.16 | Effect of wire length and the SIS scripts on the ISCAS 85                          |    |

|      | Benchmarks                                                                         | 98 |

| 4.17 | Mean & Standard Deviation of sizes for ISCAS85 circuits (for                       |    |

|      | wire length and minimization approximations) 1                                     | 01 |

| 4.18 | Reconvergent Fanout Information for Logic Synthesis 91                  |     |

|------|-------------------------------------------------------------------------|-----|

|      | Benchmarks                                                              | 106 |

| 4.19 | Comparision of $\vec{S}$ combination strategies for Logic Synthesis     |     |

|      | 91 Benchmarks                                                           | 108 |

| 4.20 | Comparision of $\vec{S}$ combination strategies for ISCAS 85 Bench-     |     |

|      | marks                                                                   | 109 |

| 5.1  | 4,5 and 6 input randomly generated functions                            | 159 |

| 5.2  | 7,8 and 9 input randomly generated functions                            | 160 |

| 5.3  | Two-level Functions from the Logic Synthesis 91 Benchmarks              | 161 |

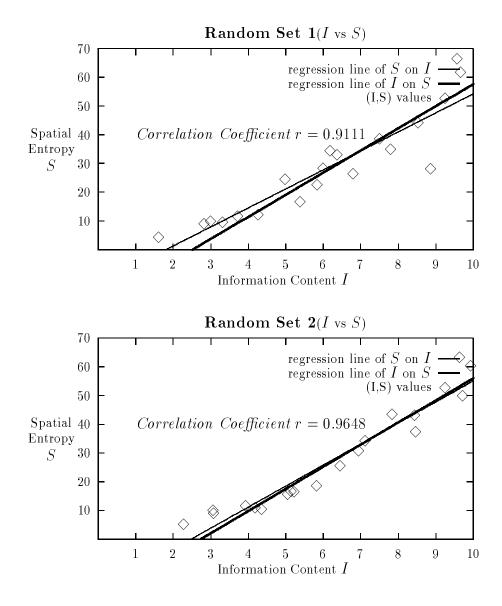

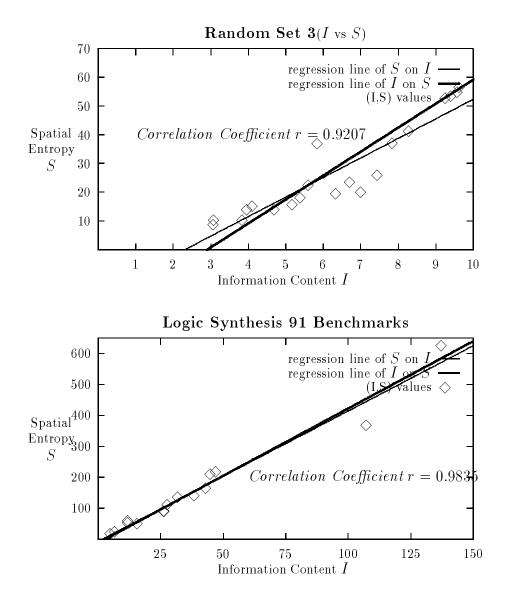

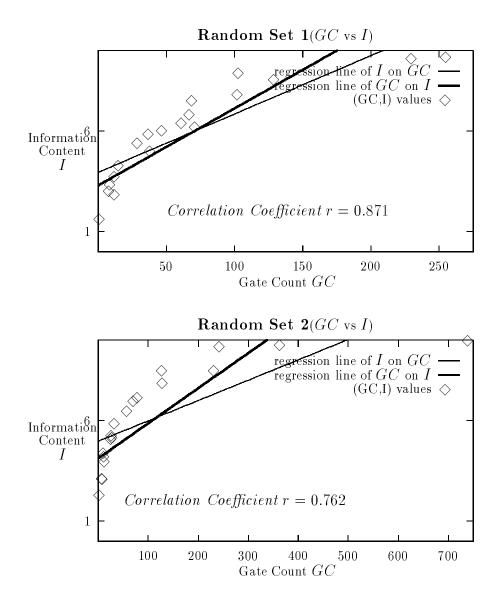

| 5.4  | $S, I(f, D_k)$ and $GC$ for random circuits (Set 1)                     | 165 |

| 5.5  | $S, I(f, D_k)$ , and $GC$ for random circuits (Set 2)                   | 166 |

| 5.6  | $S, I(f, D_k)$ and $GC$ for random circuits (Set 3)                     | 167 |

| 5.7  | Spatial Entropy and Information Content for Logic Synthesis             |     |

|      | 91 benchmarks                                                           | 168 |

| 5.8  | Mean and Variance of Spatial Entropy $(S)$ and Information              |     |

|      | Content $(I)$                                                           | 168 |

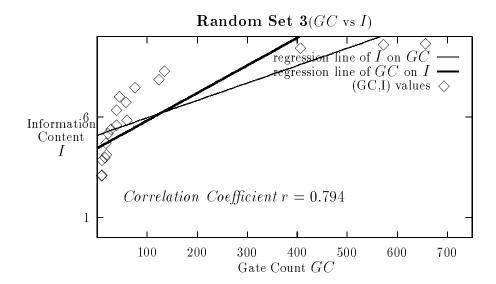

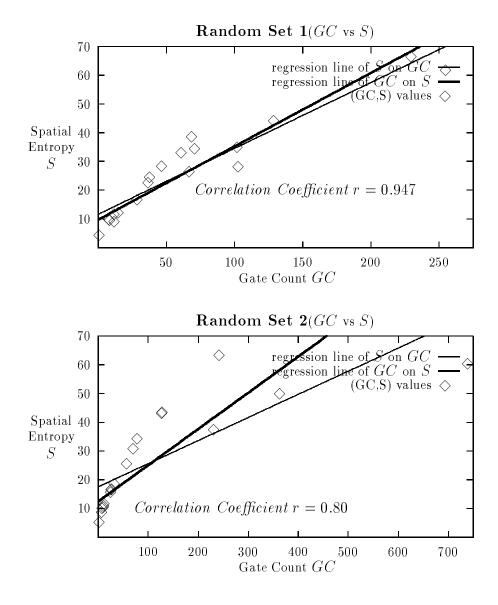

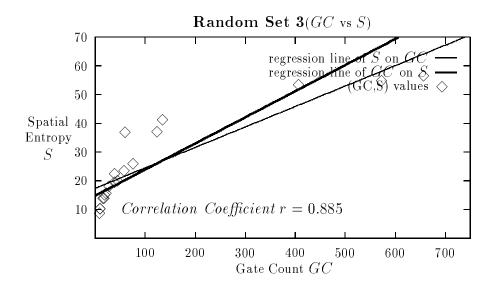

| 5.9  | Correlation Coefficients for $(S \text{ vs } I)$                        | 169 |

| 5.10 |                                                                         | 172 |

| 5.11 | Correlation Coefficients for 3 data sets (Gate Count vs S) $\therefore$ | 174 |

|      |                                                                         |     |

# List of Figures

| 3.1  | An Example Circuit and its Digraph Model                                                            | 25  |

|------|-----------------------------------------------------------------------------------------------------|-----|

| 3.2  | The Entropy Function $H_w$                                                                          | 27  |

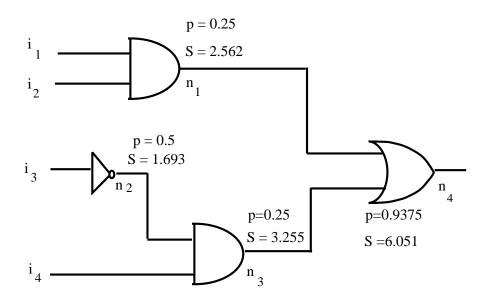

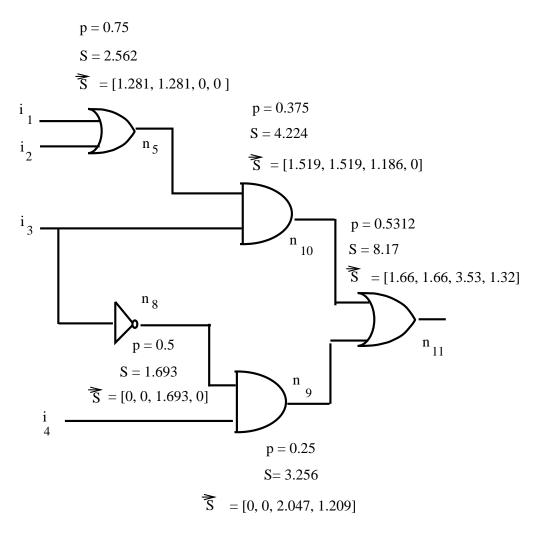

| 3.3  | Spatial Entropy Computation for a Simple Circuit                                                    | 31  |

| 3.4  | Spatial Entropy Vector Computation                                                                  | 36  |

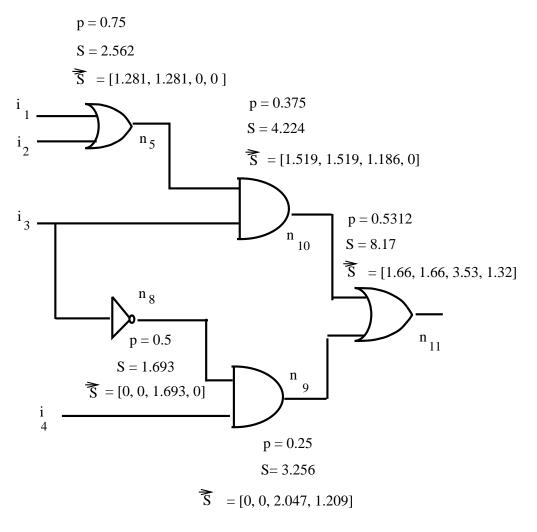

| 3.5  | Example Spatial Entropy Calculation                                                                 | 38  |

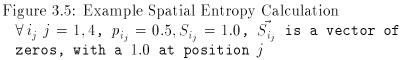

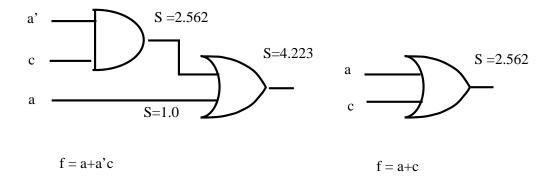

| 3.6  | Effect of Minimization on Spatial Entropy                                                           | 41  |

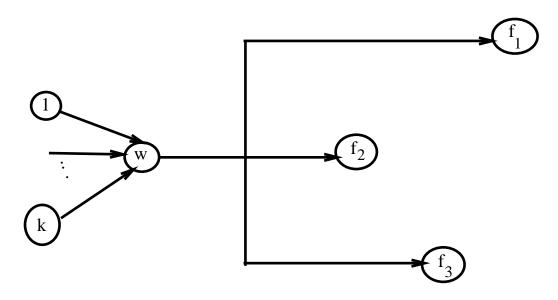

| 3.7  | A Node $w$ with Multiple Fanouts $\ldots \ldots \ldots \ldots \ldots \ldots$                        | 43  |

| 3.8  | Reconvergent Fanout - An Example                                                                    | 46  |

| 3.9  | A Circuit with a Supergate $SG(12)$                                                                 | 49  |

| 3.10 | The Supergate $SG(12)$ denoted as one Large Gate Node $\therefore$                                  | 52  |

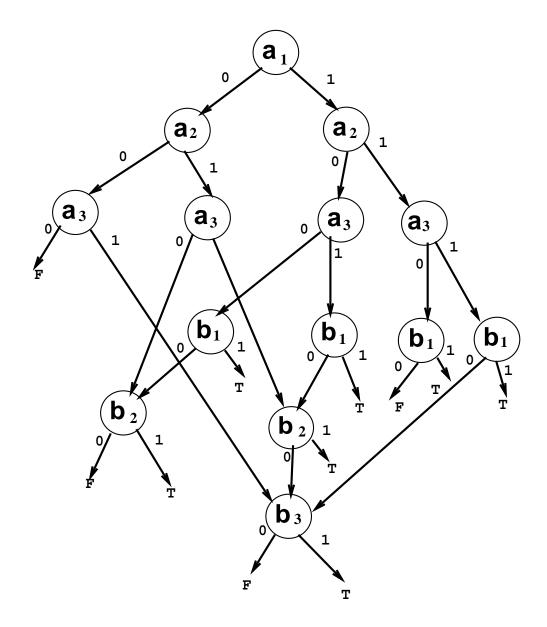

| 4.1  | OBDD of $f = a_1.b_1 + a_2.b_2 + a_3.b_3$ with ordering                                             |     |

|      | $\{a_1, b_1, a_2, b_2, a_3, b_3\}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 58  |

| 4.2  | OBDD of f with ordering $\{a_1, a_2, a_3, b_1, b_2, b_3\}$                                          | 60  |

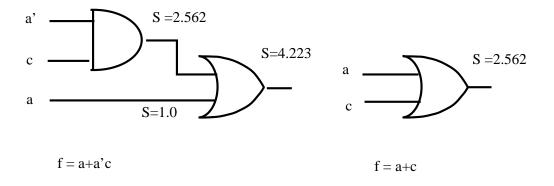

| 4.3  | Example Spatial Entropy Calculation                                                                 | 66  |

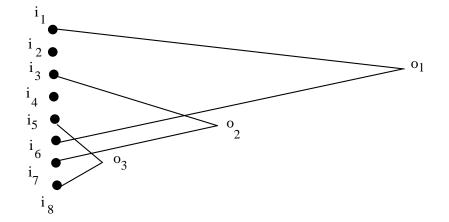

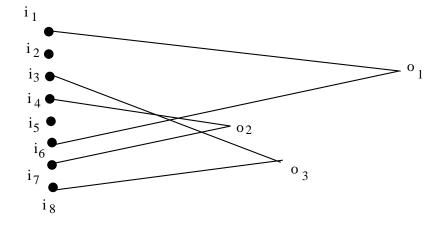

| 4.4  | Spatial Entropy Distribution for a 3-output function (Maxi-                                         |     |

|      | mum)                                                                                                | 68  |

| 4.5  | Spatial Entropy Distribution for a 3-output function                                                |     |

|      | (Weighted Multiply)                                                                                 | 69  |

| 4.6  | Two implementations of the same function with differing Spa-                                        |     |

|      | tial Entropy                                                                                        | 72  |

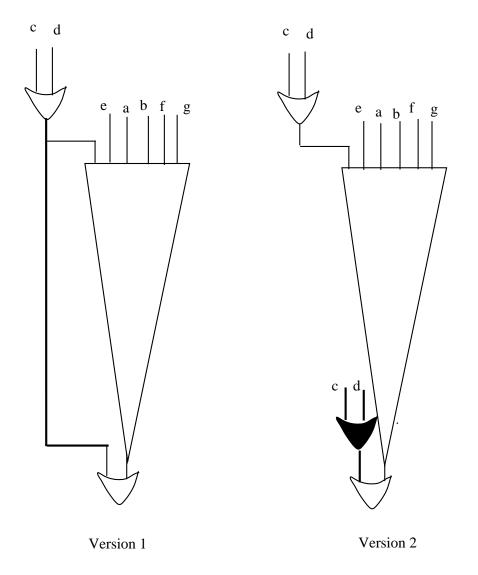

| 4.7  | The tradeoff between redundancy and wire length                                                     | 74  |

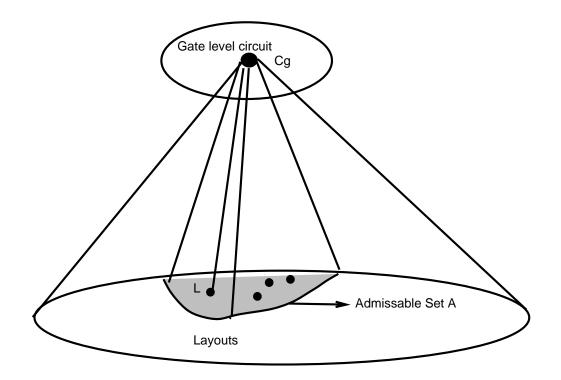

| 4.8  | Mapping of Gate Level Circuits at the Layout Level                                                  | 75  |

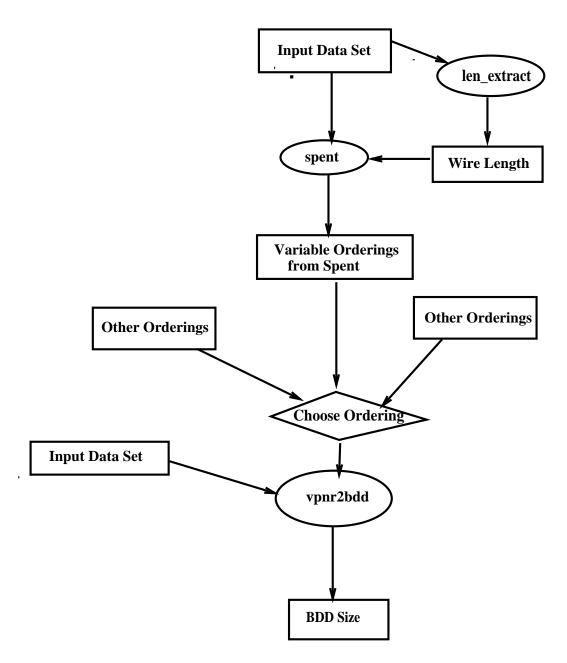

| 4.9  | Experimental Setup                                                                                  | 83  |

| 4.10 | Effect of Minimization Scripts on the Logic Synthesis Bench-                                        |     |

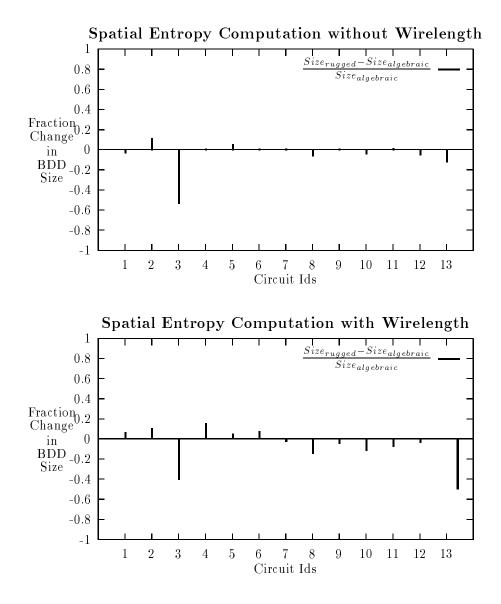

|      | marks                                                                                               | 99  |

|      | Effect of Minimization Scripts on the ISCAS 85 Benchmarks                                           | 100 |

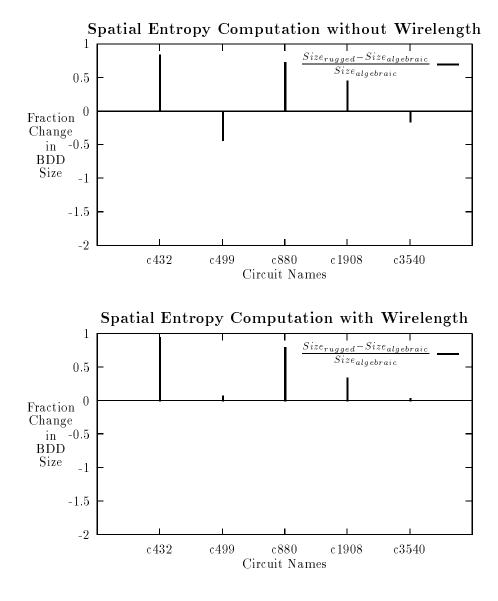

| 4.12 | Effect of Wire Length on the Logic Synthesis Benchmarks                                             | 103 |

|      |                                                                                                     |     |

|         | 104                                           |

|---------|-----------------------------------------------|

| s       | 110                                           |

|         |                                               |

|         |                                               |

|         | 120                                           |

|         | 122                                           |

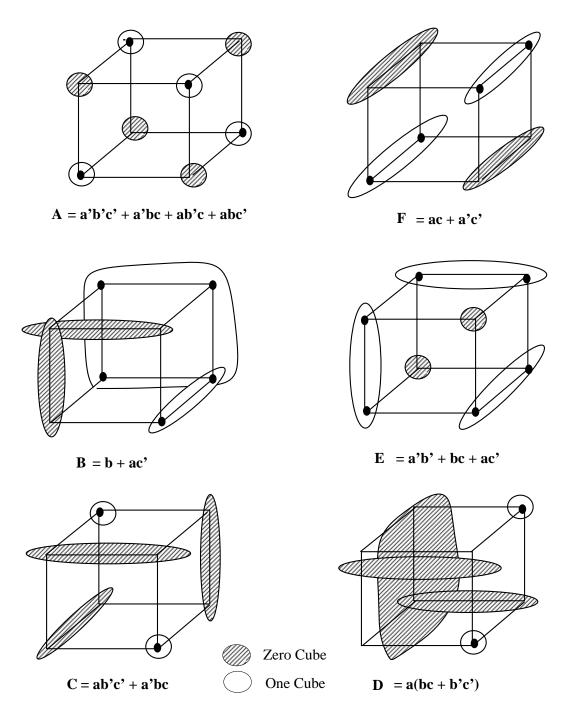

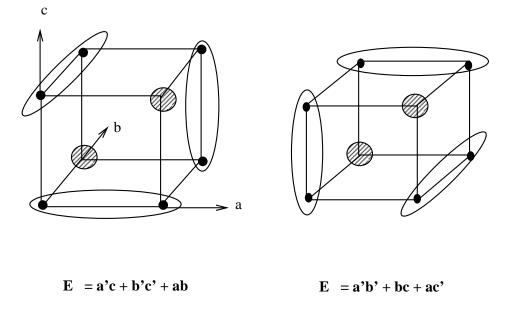

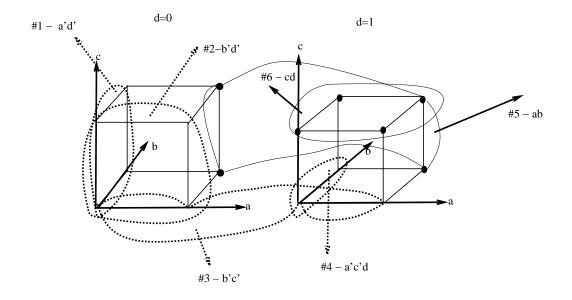

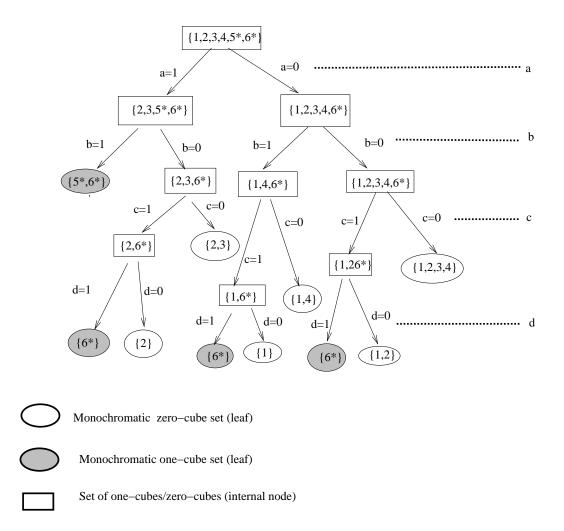

| nctions | 125                                           |

|         | 127                                           |

|         | 133                                           |

|         | 135                                           |

|         | 136                                           |

|         | 140                                           |

|         |                                               |

| ıre 5.1 | 0 145                                         |

|         | 146                                           |

|         | 147                                           |

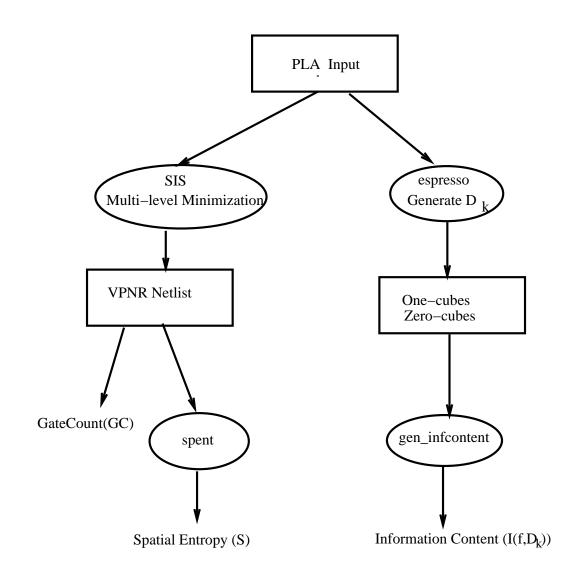

|         | 163                                           |

|         |                                               |

|         |                                               |

|         | 173                                           |

|         |                                               |

|         |                                               |

|         |                                               |

| 1       | s<br><br><br><br><br><br><br><br><br><br><br> |

## Chapter 1

### Introduction

The increasing complexity of VLSI circuit design has continually motivated research in VLSI Design Automation and Computer-Aided-Design(CAD) tools for VLSI. The task of these CAD tools is to help automate and speed up the design process. Unfortunately almost all the problems that these tools attempt to solve are NP-complete. As a result many tools and their underlying algorithms can only achieve approximate solutions via heuristics. The quality of these solutions is often dictated by the information the algorithm can extract from the circuit, in the form of attributes. These circuit attributes can be broadly classified into *static* attributes and *dynamic* attributes. Static attributes are usually computed by examining the topology or static structure of the circuit. For example, the gate count attribute used in logic synthesis is a static attribute. Dynamic attributes on the other hand are computed by applying input data to the circuit. They capture circuit behavior or dynamic usage, in contrast to static attributes that capture circuit structure. Examples of dynamic attributes include 1-probability, observability, and controllability, used in test generation algorithms. This dissertation illustrates the use of a unified attribute that captures dynamic circuit usage and static circuit structure. As a physical attribute it provides a quantitative measure of switching energy in the circuit.

Static attributes, by themselves, do not always provide sufficient information for algorithms to make good decisions. Since they are computed by statically examining the circuit structure they are unable to estimate how various parts of the circuit get used over different input combinations. In addition, these attributes often use information from one implementation to capture the behavior of a function over all implementations. This over-reliance on the static structure can result in significant variations in the value of the attribute over different implementations. While this may seem desirable for some purposes, it is not helpful when the attribute is trying to capture a property of the function common to all implementations. In contrast to this, an attribute that can capture usage over all the input assignments is likely to show less variation over different implementations. This is because this usage is common to all implementations of a function. When an attribute can combine this dynamic usage information along with the static structure (in an implementation), it can answer questions about the function and the implementation.

We have quantitatively defined and characterized a circuit attribute called spatial entropy that can capture static structure and dynamic behavior in a circuit. We propose an efficient method to compute this attribute in a given circuit. We comprehensively analyze the attribute, describe the difficulties in computing it, the factors affecting its accuracy, and the effects of various approximations. In CMOS circuit implementations spatial entropy yields a measure of switching energy in the circuit by capturing the switching activity during dynamic power consumption. We illustrate its use in BDD variable ordering, a problem that has traditionally relied on static attribute based solutions. We also show that it can be used to capture function behavior through implementations by measuring of gate-count complexity in boolean functions. In this chapter we begin with an overview followed by an introduction to the problem and the motivation behind it. Then we state our thesis outlining its scope and assumptions. Finally, major contributions of the dissertation are outlined along with a description of the rest of the chapters.

#### 1.1 Overview

VLSI circuit design is the process of transforming a high-level behavioral description into mask geometry that is mapped onto silicon. Due to the complexity of the design process, this task is typically performed by refining the initial behavioral description over several levels of abstraction. At each level of abstraction the circuit is described with increasing detail. This hierarchy of levels corresponds to phases in the design process: *architectural level, reg-*

ister transfer or boolean function level, logic gate level, and physical level or layout level.

The objective of research in CAD for VLSI is to develop tools to help automate the design tasks performed at the various levels of abstraction. A partial list of research problems in CAD includes: high-level synthesis - compiling behavioral HDL descriptions into RTL structures, logic minimization, and *logic synthesis* - minimizing two-level and multi-level boolean function descriptions to generate factored forms of the function, netlist optimization and technology mapping - mapping the factored boolean descriptions into gates belonging to a technology while performing area/time optimizations to the gate level netlist, *timing* and *critical path analysis* - estimating delay in circuit, simulation - propagating binary vectors through logic gates and transistors to verify function and timing, verification - using formal or symbolic techniques to verify function and timing across abstraction levels, test generation, and testability analysis - generating test vectors for the circuit and estimating its testability, *placement*, *layout*, and *routing* - placing the netlist of gates on a two-dimensional plane and connecting the nets with constraints of minimum area and delay.

Several of the research areas cited above use static circuit attributes to derive solutions. A static attribute is a structural attribute that is derived from a static examination of the circuit topology. It does not require the circuit to be exercised with data. For example, consider logic minimization and logic synthesis. The attribute used to guide two-level and multi-level logic minimization [BRSVW87] is *minimum literal count* (or *gate count*) that can be obtained by static examination of the boolean function description or the circuit topology. The phases of technology mapping [LBK88] and netlist optimization [TSB91] also use a static attribute (gate depth) for critical path removal and delay reduction. Timing analyzers [Ous83] work similarly. Placement, layout and routing [LP88] tools also use static attributes such as layout area, active area, net length, wire length and number of vias. In variable ordering for binary decision diagrams (BDDs), the level or depth of a node in a circuit has been used as a static attribute in various heuristics to generate orderings [BRM91].

All these CAD tasks are similar in that they are solved using static attributes defined at a given level of abstraction. These attributes do provide useful information about circuit structure and structural connectivity, and they are fairly easy to compute; but they have their drawbacks. They lack dynamic usage information, that is, information about how the various parts of the circuit get used over the different input combinations; and this is essential to solve some problems. For instance, the dynamic power consumption in a circuit is a function of the amount of switching that takes place in the circuit as the nodes change states  $(1 \rightarrow 0, 0 \rightarrow 1)$ , by charging and discharging capacticances. This is difficult to capture when the circuit is not exercised over different input combinations.

It is also difficult to capture function behavior with a static attribute. The number of input combinations that influence a node is usually a measure of the minterms (or cubes) associated with that node, and it is unlikely that a static attribute can capture sufficient information about the  $2^n$  minterms of a given function. A static attribute is computed on the circuit topology, and as a result its value is often influenced by the implementation itself. Two different implementations of the same function may often exhibit significant variances in their static attribute measures. When discriminating amongst implementations this may be beneficial. But this becomes a drawback when the attribute is trying to capture a fundamental characteristic of the function that is expected to remain invariant over different implementations of the remain invariant over different implementations of the static attribute are not desirable.

There are some areas of CAD like simulation (gate-level, switch-level, and fault), test generation and testability analysis, where the approach is inherently dynamic and the circuit is exercised for many input assignments. They use dynamic attributes like simulation vectors, signal probabilities, controllabilities, observabilities, and testability. But most of the other CAD tasks that require structure manipulation have restricted themselves to solutions based on static attributes. They have done so primarily because of efficiency considerations and because information from the static circuit structure is essential to solving several of these problems. Dynamic attribute computation requires the circuit to be exercised for several input assignments, and this usually requires more (time and space) resources than static attribute computation.

We believe that an attribute that can capture dynamic usage over various parts of the circuit along with static circuit structure can be useful in providing more information about the function *and* the implementation. We motivate the need for such an attribute in the next section.

### 1.2 Motivation

Why is such an attribute needed? Almost all problems in CAD are NPcomplete [LP88]. It is computationally intractable to find an exact optimal solution for all but the smallest problems. The problem of two-level and multi-level logical minimization is NP-complete [BHMSV84, Law64]. Placement and layout tools face an NP-complete problem in trying to embed a non-planar graph on a plane with minimum arc crossing [GJ79]. Complete gate level or transistor level simulation over all the input assignments takes exponential time. The best known deterministic algorithm to arrive at an optimal variable ordering for a BDD is  $O(3^n)$  [FS90]. This means that efficient solutions to all these problems are heuristics or approximate strategies that use information derived from the circuit to achieve desired criteria.

CAD problems that have relied on static attributes to achieve these solutions do not always capture sufficient information about the circuit to be able to make informed decisions. Typically, static attributes try to capture information about the behavior of a function from one particular implementation of the function. Since the attributes are derived from the static structure of the implementation they may fail to provide accurate information about the function as a whole. Consider timing analysis. The static sensitization process used to identify critical paths can erroneously identify false critical paths in the implementation that in reality may never be able to propagate a signal under any input combination. Variable ordering for BDDs is another area that relies on some (still unknown) fundamental attribute of the function for its solution. The use of static node depths or node levels (in an implementation) to discriminate between inputs and generate orderings is an attempt to capture function behavior from an implementation. But this may not always be accurate since an implementation represents only one of several possible interpretations of the given boolean function. Our hypothesis is that an attribute that can capture usage over various input combinations along with static circuit structure will be able to provide more information to help algorithms like these make better decisions.

Information about the structure and behavior of an implementation is also very helpful when computing (or estimating) the energy consumption in a circuit. With increasing circuit performance, energy and power consumption are becoming serious concerns for a designer. They are important metrics of circuit performance. The *switching energy* for a device [MC79] is equal to the power consumed by the device (at maximum clock frequency) multiplied by the device delay. In CMOS implementations, the switching power  $P_{sw}$ at a node is a direct function of the clock frequency and the charging and discharging of circuit capacitances at a node,  $P_{sw} \propto C_{sw}V^2 f_{clk}$ . In order to measure this dynamic power consumption the switching activity over all the nodes in the circuit needs to be estimated. This requires dynamic usage information. The delay in a circuit is a function of the switching capacitance  $C_{sw}$  determined by the logic and the wires in the circuit. The time taken for the gate to charge or discharge the switching capacitance determines the delay. Estimating this requires structure and connectivity information of the logic and wires. Switching energy of a circuit is thus a complex function of not just the static structure and connectivity of the implementation, but also the dynamic behavior of the function being implemented. A single attribute that can unify these characteristics will be able to provide a quantitative estimate or measure of the energy consumption in a circuit.

Dynamic usage not only refers to the different combinations that the inputs can take, but also to the manner in which these combinations can cause data to combine and communicate through the circuit. Static structure on the other hand requires information about the gates, their arrangement, and the wires that connect the gates. What makes it difficult to define an attribute that can unify these two features? An important factor is the different levels of abstraction that distort the estimates needed to capture dynamic usage and static structure. The boolean function level estimates circuit usage in terms of cubes and minterms while the logic level might estimate it in terms of the logic gates. This is further complicated by the fact that information at one level of abstraction may be totally (or partially) absent at another. For instance distance estimates are absent at the boolean function level. Some level or depth information is present at the the logic gate level, but wire length information is absent. Usage estimates change again at the layout level when wire lengths are also included.

Another factor that makes it difficult to define such an attribute is the different levels of abstraction that distort the flow of information across the levels. This makes it difficult to unify the costs of the logic gates and the wiring together. Logic cost is estimated by attributes such as gate count, literal count, and cell area estimates, while wiring cost is provided by attributes such as wiring area, net length, number of nets, *etc.*. These costs span across different levels of abstraction (gate and layout) making it difficult to unify

them.

The problems get more complicated for random logic than for regular logic. This is because the design-space in regular logic (like datapath circuits) is fairly well structured and can be explored in a methodical fashion. Circuit usage over various inputs is also quite regular. Hence, asymptotic area-time bounds can be derived for such circuits, *e.g.* adders, shifters, and multipliers. This helps simplify the task of modeling circuit usage and wiring. On the other hand the design space for random logic is very discontinuous and lacks structure. This makes it difficult to talk about dynamic usage or wiring complexity without tracking the logic and the wires together.

Finally there is also the fundamental problem that capturing dynamic usage of a circuit over all input combinations requires an exponential number of combinations to exercise the circuit.

In this dissertation we propose a new circuit attribute called *spatial entropy* that is capable of capturing the dynamic data movement and usage in a circuit along with the static circuit structure. In the next section we provide some background information and then state our thesis and describe its scope along with our goals and assumptions.

### 1.3 Thesis

The concept of spatial entropy is not new. It was first introduced by Carver Mead [MC79] to capture the communication activity in any physical computing system. He distinguishes between *logical entropy* and *spatial entropy* in the following way: while logical entropy is a measure of the effort needed to transform data from one form to another (computation), spatial entropy is a measure of the effort needed to transmit data from one place to another (communications).

Our thesis is that "spatial entropy can be quantitatively defined and characterized as a dynamic circuit attribute, and it can be applied to CAD problems that have relied on static-attribute based solutions.".

We defend this statement in three phases - definition, analysis, and application. In the first phase, our goal is to introduce the spatial entropy concept to the circuit domain. We define spatial entropy intuitively as the *dynamic communication effort* in a circuit. This intuitive definition is then followed by a quantitative definition of spatial entropy as a circuit attribute computable at every node in a circuit. This is then used to compute spatial entropy values over all nodes in the circuit. We describe its relation to a physical circuit attribute - switching energy. The objective here is to be able to compute and compare spatial entropy values for different circuits and obtain measures of their switching energies. This will help answer questions like: what does it mean for one circuit to have greater spatial entropy than another? What is the reason that a given circuit has high or low spatial entropy?

In the second phase we propose to analyze and further characterize the spatial entropy attribute. Our goal here is to study the problems faced in computing this attribute so that we can answer questions such as: How is spatial entropy best computed? How accurate is the computed value? What are the factors that affect this and how can they be controlled?

As a further characterization we plan to show that the definition of spatial entropy at a node can be extended by describing it as an accumulation of spatial entropy contributions from primary inputs affecting that node. We define this quantitatively so that it can be computed efficiently. This will help compare and contrast the communication effort of a pair of nodes at a finer granularity - in terms of the contributions of the primary inputs to the two nodes.

Finally we illustrate the usefulness of spatial entropy as an attribute that can capture function behavior and as an attribute that provides a quantified measure of the switching energy in a circuit. We compare the spatial entropy based approach with approaches that use static attribute based solutions to capture circuit behavior. Since spatial entropy models dynamic usage we hope to show that it captures a characteristic of a function that is invariant over its different implementations. This way spatial entropy will be able to track function properties through implementations. Our objective is to show that we can compute the spatial entropies of the implementations of two different functions and then use these values to contrast the two functions themselves.

Along with the effectiveness of spatial entropy as an attribute in CAD we also intend to study empirically the effects of the various approximations on spatial entropy computation and their influence on the quality of the solution. We would like to be able to determine whether spatial entropy is indeed a useful circuit attribute for solving CAD problems. What kind of problems is it best suited for and how does the accuracy of its calculation affect the quality of the solution? The scope of circuit descriptions for this thesis is limited to combinational circuits. Circuit descriptions at the boolean function level and the gate level are acceptable. We assume a circuit model made up of the standard logic gate primitives: and, or, not, xor, nand, and nor. Transistors and lower-level structures are not treated. This thesis does not propose spatial entropy as a universal solution to CAD problems, at these levels of abstraction. What it does say is that there are several occasions where algorithms can benefit from information about dynamic usage in the function along with the static structure in the implementation. In such cases spatial entropy would be a useful attribute, and CAD tools that have traditionally used purely static attributes could benefit from this additional information on dynamic usage.

The next section discusses the major contributions of the dissertation, along with implications of this research.

### 1.4 Research Contributions

We briefly summarize the major contributions of this dissertation.

- 1. We have introduced the concept of spatial entropy to the VLSI domain as a circuit attribute.

- 2. We have defined it and characterized it as a measure of the switching energy (in CMOS implementations). An effective approach to compute it on VLSI circuits at different levels of abstractions is described.

- 3. We have illustrated its applicability in CAD.

- 4. We show that the spatial entropy of an implementation captures function behavior by modeling the dynamic communication effort needed to compute the function.

We have introduced spatial entropy as a circuit attribute that is capable of unifying the structure and behavior in a circuit. An intuitive definition has been refined to formulate a quantitative definition of spatial entropy as the *information-distance* product in the circuit. Information captures the dynamic switching of logic states at a node in the circuit. The distance that information has to travel is captured by the switching capacitance at the node. With this information-distance model spatial entropy measures the switching energy in a circuit implementation. A circuit with minimum spatial entropy is a minimum energy implementation that minimizes the dynamic power consumption and the delay over all the nodes in the circuit.

We have proposed a simple, efficient algorithm to compute spatial entropy for primitive gates and for an entire circuit. But it is difficult to compute spatial entropy accurately for a given implementation. Hence approximations that affect this accuracy have been identified and their implications were studied in detail, at different levels of abstraction. These effects were also studied empirically in the context of an application of spatial entropy, where we used spatial entropy to generate variable orders for binary decision diagrams (BDDs). We demonstrate that the spatial entropy based approach can generate variable orders competitive with existing static attribute based approaches, for the smaller benchmark circuits. But when the circuits get larger the effect of approximations made in computing the attribute become more significant leading to poor sizes. They have been outlined in detail with empirical results.

Simultaneously, we also explored a theoretical basis to connect spatial entropy and variable ordering. The BDD of a function depends on the characteristics of its minterms. If the spatial entropy of an implementation is indeed capable of generating good variable orders for the BDD of the underlying function then it must capture some characteristic of the function. But we observed that different implementations of the same function could differ significantly in their spatial entropy values due to different degrees of logic minimization in each implementation, *i.e.* minimality had a significant influence on spatial entropy.

So this posed the question: what is the best implementation to capture this function behavior and generate spatial entropy based variable orders and why? In a physical implementation spatial entropy is the switching energy expended by the circuit while computing the function. Over all implementations of a given function, the one with minimum spatial entropy has minimum switching energy and describes the minimum communication effort needed to compute the function. This minimum spatial entropy implementation is like a signature for the function since it provides a lower bound over all implementations of that function. But generating an implementation with minimum spatial entropy is difficult since it requires minimizing logic gates and wires, which the existing logic synthesis tools are not capable of doing. As an approximation to a minimal spatial entropy implementation we use a minimal gate count implementation. In order to study how spatial entropy on a minimal gate count implementation captures function behavior, we started by defining minimality and spatial entropy computation in cube space. This work also led to the second application of spatial entropy, its use as a gate-count complexity measure for boolean functions.

We first proposed an entropy based definition of the gate-count complexity of boolean functions called *information content*. Since the *complexity* of a function is a measure that provides a lower bound on some physical attribute over all implementations of that function this captures a fundamental characteristic of function behavior. We also show that the information content, which is defined over a minimal Karnaugh decomposition of the function. captures minimality of two-level function representations. This is because the minimal Karnaugh decomposition is equivalent to a minimized prime and irredundant two-level representation of the function. Minimality for multi-level function representations was then defined using a notation called decision tree to relate a function to its implementation. An implementation is constructed bottom up from a decision tree, and a minimal implementation corresponds to a minimal decision tree. Spatial entropy in cube space was then defined as the incremental contribution to the information content, over all nodes in an implementation derived from the decision tree. This definition of spatial entropy captures the communication between the minterms in the implementation.

We then empirically verified that spatial entropy of a minimal implementation does track function behavior in the form of the information content of the function. While it is computationally intractable to compute the cube space definition of spatial entropy, we showed that the gate-level spatial entropy computation procedure can be used as an approximation to it. We showed statistically that there is a strong correlation between the spatial entropy of a minimized implementation (as computed by the gate-level procedure) and the information content of the function. Our definition of cube space spatial entropy and information content was only defined for singleoutput completely specified functions. So we handled multi-output functions in our experiments by treating each of them as individual single-output functions.

The information content of the function is defined over a minimal Karnaugh decomposition and is thus an indicator of minimality in two-level functions. We showed that the information content also estimates the gatecount complexity of a multi-level implementation of the function, in terms of the logic gates required to implement it. An empirical correlation between the information content and the gate count (in a multi-level implementation) is shown for several single output functions.

The high degree of correlation between spatial entropy and information content shows us that spatial entropy can be used to measure the gate count of a multi-level implementation of the function. We also found a strong correlation between spatial entropy and gate count for our experimental data set. There is an explanation for this. Given that we limit our scope to only combinational circuits, the switching energy in these circuits is a function of the switching of states at the nodes and the delays at the nodes. In most combinational circuits this switching energy is equivalent to the circuit area since almost the entire circuit is switching as the circuit computes dynamically; since spatial entropy measures switching energy we find the high correlation between spatial entropy and circuit area. This correlation would probably be absent in sequential circuits where the switching energy is not a direct function of circuit area, or in other combinational circuits where only a fraction of the area is switched.

Spatial entropy is a unique attribute, since it is capable of capturing the structure in an implementation and the behavior of the function being implemented. One can use the structural aspect of spatial entropy to discriminate between two implementations of the *same* function, where an implementation with lesser spatial entropy has lesser switching energy. Since a minimum spatial entropy implementation acts as a signature of the underlying function, one can compute this for two *different* functions and compare the minimum switching energies of these two functions. The fact that spatial entropy can measure information content, a characteristic of the function that is invariant over different implementations, further lends credence to our hypothesis that spatial entropy, if computed accurately, can generate good variable orders for BDDs, on even the larger circuits. This is because BDDs too are a characteristic of the function definitions and not of its implementations.

### 1.5 Dissertation Outline

In the next chapter we describe work that is related to our research. This is discussed along three directions. We first describe traditional static and dynamic attributes in CAD and highlight the circuit properties that they capture. Then we discuss approaches that estimate complexity in terms of information flow or wiring area when data has to be communicated between various places in a circuit. Finally we discuss entropy based attributes in CAD.

In Chapter 3 we introduce the spatial entropy concept to the circuit domain. It is first defined intuitively, and then quantitatively as a dynamic circuit attribute that measures the switching energy in a circuit. We show that spatial entropy can be computed using existing circuit attributes, and we propose an algorithm to compute spatial entropy for primitive gates and for an entire circuit. In the remainder of this chapter we characterize the attribute thoroughly, explain why it is difficult to compute it accurately, and outline the approximations that affect its accuracy.

The subsequent chapters illustrate applications of spatial entropy. In Chapter 4, we begin by introducing the variable ordering problem for binary decision diagrams (BDDs). After a short survey of related research we describe our approach of using spatial entropy vectors to generate variable orders. The rest of the chapter describes our experiment to study spatial entropy based variable ordering empirically. The objectives are two-fold. First we study the effectiveness of spatial entropy in generating variable orders, and compare it with several existing approaches. Then we study the effect of the various factors and approximations and how they affect the accuracy of spatial entropy.

Chapter 5 draws on the conclusions in Chapter 4. It explains minimality and spatial entropy in cube space. It also illustrates empirically how spatial entropy can measure the area-complexity in boolean functions in terms of the multi-level gate implementations of these functions.

Finally we summarize conclusions and future directions in Chapter 6.

### Chapter 2

### **Related Work**

The spatial entropy attribute has three characteristics - its ability to unify static circuit structure and dynamic usage, its ability to capture function complexity, and its information theoretic basis. We discuss related work in this chapter by developing it along these three directions.

First we briefly describe traditional attributes that capture either static structure or dynamic usage and discuss how they have been used to solve CAD problems. Our purpose here is to illustrate circuit properties that are captured by these attributes in order to contrast them later to the properties captured by the spatial entropy attribute. In the second part of this chapter we discuss approaches that estimate the complexity involved when data has to communicate from various points in the circuit. The objective here is to illustrate how these approaches have been used to derive indicators such as information flow, wiring area *etc.* to estimate this complexity. This will help us contrast them with the use of spatial entropy to capture wiring complexity and boolean function complexity which we discuss in later chapters. Finally we describe other entropy based attributes that rely on an information theoretic definition (like spatial entropy), and outline their application to problems in CAD.

### 2.1 Static and Dynamic Attributes

We begin by briefly contrasting static and dynamic circuit attributes. *Static* attributes are computed by examining the circuit structure or topology. In

contrast *dynamic* attributes are computed by exercising a circuit representation such that the circuit computes over a distribution of input values. While static attributes capture circuit connectivity or structure, dynamic attributes capture usage of various parts of the circuit over a distribution of input data values. Static attributes can be usually computed quickly; dynamic attributes on the other hand can be expensive to compute. We now consider a subset of CAD problems and describe in turn, the role static and dynamic attributes play in solving them. We also highlight the circuit properties captured by these attributes.

Static attributes are typically used when information about the circuit connectivity or structure is essential to solving the problem. Consider the problem of timing analysis. The objective here is to identify the critical (or longest sensitizable) path in the circuit to estimate the worst-case delay. Since the actual delay along a path in the circuit depends on the propagation delay and the number of gates in the path, classical static timing analysis [Ous83] uses attributes like static gate depth and fanout along with propagation delay to arrive at an estimate of the worst-case delay. But this is not always a true estimate. This is because some paths in the circuit are generated with sub-paths that require input combinations that can never occur. These logically incompatible paths are called *false paths* and accumulating gate delays along such paths would be erroneous. On the other hand an exact estimate of the critical path delay in the circuit would require simulating the circuit over all possible inputs to examine the effects of all input combinations. Since this is expensive the static attributes are used to obtain a quick approximation of the actual delay in terms of gate connectivity and gate depth. A lot of the work in timing analysis now concentrates on eliminating false paths [BI86, MK89, DYG89, BMCM90, PCD89].

Logic minimization and logic synthesis is another area of CAD where solutions are guided by static circuit structure information. One of the objectives here is to map a two-level boolean function representation into a set of gates (from some library) that occupies minimum area [BHMSV84, BM82, BRSVW87, LKB87, LBK88]. Ideally one would like to achieve this objective of minimum area with respect to not just the gates in the circuit but also the wiring between them [Sau92]. But since the notion of wires is absent at the logic level of abstraction the objective is restricted to minimum gate area. The static circuit attribute of literal count becomes an approximation to the gate area. Hence algorithms in logic minimization and logic synthesis use minimum literal count as the area criterion. Literal count is not only used as a measure of performance of the algorithm, but it is also used to guide the algorithm during the minimization process. It assists in searching and selecting candidate factors for substitution while decomposing and factoring the boolean function.

Finally let us look at static attributes at the physical layout level. CAD tools in the area of placement and routing are faced with the goal of placing circuit components on a 2-dimensional plane and connecting nets between them such that area and delay of the resulting circuit layout is minimized [LP88]. Again static structure and connectivity information play an important role here. They are captured by attributes like wire length, component dimensions, user-defined or pre-routed obstructions *etc.*. These yield minimization criteria such as minimum total net length, minimum circuit area, minimum number of vias, routeability for all nets, prior routing of selected (power and ground) nets *etc.*. The algorithms are guided towards desired solutions by a suitably weighted version of these criteria.

Dynamic attributes are typically used when circuit behavior over all possible inputs needs to be captured to solve a problem. Simulation is one such instance. Regardless of the kind of simulation (function, gate, switch, circuit, fault), it is complete only when the circuit behavior for all possible inputs is studied. In such a case the input vectors that represent various input combinations are dynamic attributes that capture circuit usage as they propagate through the various nodes.

Testability analysis [BPH84, SDB84, JA84, LBdGG87] which is sometimes viewed as an alternative to fault simulation, is another problem that relies on a dynamic attribute. The objective here is to project the cost of testing by predicting the number of random test patterns needed to achieve high fault coverage. High fault coverage is usually defined by predicting a large percentage (95 - 98%) of faults in the circuit with a high probability (0.98 - 0.99). To solve this problem the probability of detecting a fault is expressed as a function of two probability based attributes: *observability* and *controllability*. Controllability is computed by assigning signal probabilities at the inputs to the circuit and propagating them forward through all the nodes in the circuit. Observability is computed similarly except that it is computed backwards from the output. These probability based attributes are dynamic because they capture circuit usage over different input combinations. In this particular instance they are being used to detect a given list of stuck-at faults (at nodes in the circuit) by looking at the value of the node over all possible input combinations. We now look at research in communication complexity.

### 2.2 Communication Complexity Prediction

With VLSI design being performed in sub-micron technology with smaller feature sizes there is a realization that the area-time and power performance of a circuit will be dominated less by the logic or the gates in the circuit and more by the *wires and the communication* between the logic. This has resulted in efforts to estimate communication complexity by the wiring area or information flow in a circuit.

In 1979 Thompson introduced a model [Tho79] for computing lower bounds on the complexity of VLSI implementations of functions. The complexity of the computation was measured in terms of bounds  $(AT^2, A^{\alpha}T^{\beta})$ on chip area and computation time. The model highlighted the difficulty of communicating information across the surface of a chip. Given any partition of the input set into two equal halves on two disjoint regions of the chip, these area-time bounds defined lower bounds on the communication complexity of the function.

The notion of communication complexity across a partition was introduced by Yao to provide lower bounds on the worst case information complexity of many functions [Yao79]. Yao's model assumed a particular partitioning of the input set into two equal halves (as against the VLSI complexity model that assumes any partition). This captured a local information flow across the partition. The communication complexity was defined as the number of bits of information that needed to cross the partition to correctly compute the function. These bits of information were computed by a two-way protocol that dictated how the bits would be exchanged by the two input halves. The maximum number of bits exchanged over all input values for computing the function f was defined as the communication complexity c(p) for a given protocol p. The worst-case complexity was then defined as the minimum two-way communication complexity over all protocols for that partition.

More recently Hwang, Owens and Irwin [HOI89, HOI92] have used communication complexity for multi-level logic synthesis. They have also provided ways to compute the communication complexity whose bounds were estimated in [Yao79]. In their approach the "decomposition and factoring" operations in multi-level logic minimization are performed by partitioning the boolean function f into three functions  $f_t, f_l, f_r$  such that

$$f(X) = f_t(f_l(X_l), f_r(X_r))$$

where  $X_l$  and  $X_r$  denote a disjoint partition of the input set  $X(X_l \cup X_r = X)$ . The partition is generated using heuristic partitioning techniques that try to minimize the communication complexity or the number of interconnections between the functions  $(f_t, f_l)$  and  $(f_t, f_r)$ . The communication complexity for a given partition, which acts as a cost function for their partitioning algorithm, is computed by computing the number of compatible classes [Ris82] of a given function. Two approaches were illustrated. The first approach uses a communication matrix while the second approach, which is more efficient, uses cubes and cube overlaps [BHMSV84].

Another partially related approach is discussed in [ASSP90]. Here wiring complexity in a synthesized circuit is minimized by controlling input dependency with lexicographic expressions of a boolean function. A lexicographic expression of a boolean function is a sum of product terms in which the input literals (that every product term depends upon) conform to an ordering called the reference order. This ordering is used to extract a set of lexicographically compatible kernels [BM82]. Kernel filtering computes the intersection of the extracted kernels to find shared parts amongst the functions. By tightly controlling this filtering process the logic cones can be prevented from intersecting with each other. The objective is to reduce the wiring between logic cones that manifests itself as wires in the layout.

We now discuss the application of entropy based attributes in CAD.

### 2.3 Entropy Based Attributes

#### 2.3.1 Background

We begin with some background on the concept of entropy. There are two popular definitions of entropy. *Information theory* [SW49] defines it as the measure of information content in a system. *Thermodynamic* [Sea53] defines it as the thermodynamic probability of the internal particles of a system while holding the external properties constant. We consider each definition in turn and show how they both view entropy as - " the measure of disorder in a system".

Consider a system with N possible output events. In information theory this is usually a communication system where the N events are messages to be communicated to a receiver. Suppose each event *i* has a certain probability of occurrence  $p_i$  with respect to its inputs. Then the information-theoretic definition of entropy is the measure of information produced when one event is chosen from this set N [SW49]. It is defined as

$$\sum_{i \in N} p_i \log \frac{1}{p_i}$$

When all the events are equally likely, *i.e.*  $p_i = \frac{1}{N}$ , the expression reduces to log N.

As an example consider a system where the messages are represented by a bit string of length n. The set of output events N is the set of all possible messages that can be represented by the *n*-bit string. If all bit combinations are assumed likely then the *n*-bit string can represent at most  $N = 2^n$  different messages. On the other hand suppose we insisted that only a single bit combination, that of all 1s in the string, is possible. Then only one message (N = 1) will be possible. In the former case the information content (entropy) of the bit-string is  $\log(2^n) = n$ , while in the latter case it is  $\log(1) = 0$ . Thus if greater number of bit combinations (or messages) are possible this implies greater disorder in the system. This in turn implies greater entropy or information content.

In the same vein a bit-string that is twice as long (of length 2n) will have an information content (or entropy) equal to 2n. This conforms to our intuitive notion that a message that is twice as long should be able to contain twice as much information.

In thermodynamics, entropy is defined as being proportional to the logarithm of the number of ways of arranging the particles in a system while maintaining external conditions constant. As an intuitive example [MC79], consider a system with two containers holding a total of 10 red and 10 blue molecules. If we do not distinguish between containers there is only one way in which the molecules can be arranged so that all the 10 blue ones are in one container, and all the 10 red ones in the other. On the other hand there are a large number of ways of arranging 5 of each color in each container. The second arrangement of molecules has much more disorder than the first, and therefore has much more entropy than the first. The actual definition [Sea53] of this entropy S is in terms of the *thermodynamic probability* of the internal particles in the system. It is defined as  $S = k \log W$ , where k is Boltzman's constant, and W is the thermodynamic probability.

Thus in both information theory and thermodynamics, entropy captures the measure of disorder in a system. The information-theoretic definition of entropy has found applications in a few areas of CAD. We begin by reviewing work in these areas.

#### 2.3.2 The Entropy function in CAD

One of the first applications of information theory was to use the informationtheoretic definition of entropy to predict boolean function complexity. The relationship between function complexity and entropy was first conjectured by Cook and Flynn [CF73]. The complexity of a boolean function is expressed by the cost of implementing the function as a combinational network. Cook and Flynn demonstrated empirically that the average cost behavior of a single output combinational network could be modeled by a formula that captured the entropy of the boolean function implemented by the network. It was defined as

$$H(f) = \frac{u}{2^n} \log_2 \frac{2^n}{u} + \frac{2^n - u}{2^n} \log_2 \frac{2^n}{2^n - u}$$

where n is the number of input variables and u is the number of ON-terms in the cube space. Subsequently Hellerman [Hel72] proposed a definition of computational work based on the entropy function. Suppose a function  $f: X \to Y$  performed some computation over a domain of inputs X and a range of outputs  $Y = \{y_1, \ldots, y_n\}$ . Then for  $X_i \subset X$  and  $X_i = f^{-1}(y_i)$ , the work done by the function was expressed as  $\sum_{i=1}^n |X_i| \log \frac{|X|}{|X_i|}$  where |X|denotes the number of elements in the set.

The relationship between the works of Hellerman and Cook & Flynn was later observed by Mase[Mas78]. He showed that the complexity of a boolean function can be expressed in terms of an entropy-based definition of (computational) work performed by the combinational network.

In 1977 Pippenger further refined this entropy definition to handle don't cares in the function [Pip77]. More recently in [CA90], the entropy formulation was generalized to multi-output functions, both completely specified

functions and partially specified ones. They also showed statistically that using the literal count as a measure of circuit area a linear relationship can be observed between entropy and average number of literals in a multi-level implementation.

Information theory has also found application as a testability measure. This was first proposed by Dussault [Dus78]. He presented observability and controllability measures based on information theory for gate level circuits. In [TA89], Thearling and Abraham extended this idea to estimate testability at the function level. They use a measure called the information transfer coefficient (ITC) [Koo87] to enable relative testability measures to be computed as against the absolute measures computed by Dussault [Dus78]. Agrawal [Agr81] has also applied information theory to test pattern generation. He shows that by choosing test patterns that maximize the information at the output the probability of fault detection can be maximized.

#### 2.3.3 Entropy as a basis for Computation

In [MC79], Carver Mead proposed the idea of computation based on entropy. This has formed the basis for our definition of spatial entropy in the circuit domain that we discuss in Chapter 3.

He begins by suggesting that computation can be viewed as a process that reduces the disorder (or entropy) in the solution space while arriving at a result. Every computation finds an answer by making decisions on a solution space. With each decision the usually huge initial solution space is cut down to some fraction of its former size. The number of decisions required to specify one correct answer in the solution space is the *entropy* of the computation, defined as  $\log \frac{|Total\_Solns|}{|Answer|}$ . This definition is analogous to the information-theoretic definition of entropy where the solution space is all possible messages with a given length and bit-string format. The correct answer is one such message and the entropy is the number of bits required to specify this correct answer.

The description of entropy outlined above captures algorithmic computation and Mead terms this as *logical entropy*. This is because it depends on the logical operations required to perform the computation. The objective of a computation is to reduce the logical entropy of the data to zero. The study of algorithm complexity analysis is the study of these logical operations modeled by logical entropy. Mead also proposes another form of entropy, called *spatial entropy*, that is usually seen in situations when the computation has to be mapped onto a domain where data travels over a physical distance. The contrast between the two forms of entropy is best captured by the following quote from [MC79] :

" In any physical system, the logical entropy treated by classical complexity theory is only part of the story. There is also a spatial entropy associated with a computation. Spatial entropy may be thought of as a measure of data being in the wrong place, just as logical entropy is a measure of data being in the wrong form. Data communications are used to remove spatial entropy, just as logical operations are used to remove logical entropy."

Entropy is the measure of disorder in a system. So spatial entropy is the measure of spatial disorder in a system. This spatial disorder (or spatial entropy) in a system captures a form of spatial distance between the inputs and the outputs in a system. The spatial entropy S of a system quantifies the spatial effort needed to bring the data at the input location to the output location. When a system computes, the data communications in the system are carrying data from the input to the output. This reduces the spatial distance between them, or removes spatial entropy in the system.

One scenario that illustrates spatial entropy is a communication network. Here messages or communication events are transmitted over communication pathways that remove spatial entropy by routing data between various spatially distributed source and destination sites. Another example is circuit computation. Here the input data travels through the wires in the circuit. These wires remove spatial entropy in the circuit by carrying the input data to the outputs. It is this latter model that is of interest to us. In the next chapter we characterize the spatial entropy concept in the circuit domain and define a quantitative measure that relates it to the switching energy in the circuit. We describe an algorithm that computes spatial entropy for a gatelevel circuit implementation, and study the factors affecting the accuracy of this computation.

### Chapter 3

# Spatial Entropy - A Circuit Attribute

In the previous chapter we introduced the concept of spatial entropy. In this chapter we illustrate how spatial entropy can be characterized as a dynamic attribute in the circuit domain. We define spatial entropy quantitatively, and show how it can be computed on primitive gates and over an entire circuit. We also explain how it measures the *switching energy* in a physical implementation. Computing the attribute accurately is unfortunately a difficult task, and there are different factors that affect its accuracy. In the latter part of this chapter we discuss these factors in detail and explain how they result in various approximations while computing the attribute.

We begin with an intuitive notion of circuit spatial entropy followed by a quantitative definition. In Section 3.2 the technique to compute spatial entropy for gate level primitives is described. This becomes the basis for an algorithm to compute circuit spatial entropy, which we outline in Section 3.3. Section 3.4 further characterizes the attribute by introducing spatial entropy vectors. In Section 3.5 we talk about the difficulties in computing this attribute accurately, and how these factors force approximations to be made during spatial entropy computation.

#### **3.1** Introduction and Definitions

Spatial entropy can be intuitively defined as the *communication effort* required to compute the circuit function. In a circuit both the logic gates and the wires contribute effort towards computing the circuit function. The gates compute boolean values or bits and the wires transmit these bits. Spatial entropy models the dynamic communication taking place in the circuit versus the static communication modeled by the wires. Over all the input combinations, it tries to capture the distribution of bits at the gate outputs, and the communication of these bits from one gate output to another. While the wires determine how far the bits have to travel, the gate types determine the distribution of boolean values that these bits take at the various nodes in the circuit. Together they determine the dynamic communication effort in the circuit. We use an information-theoretic definition to capture this effort through the circuit.

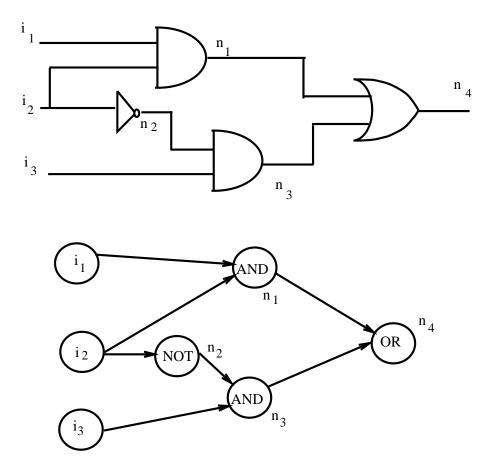

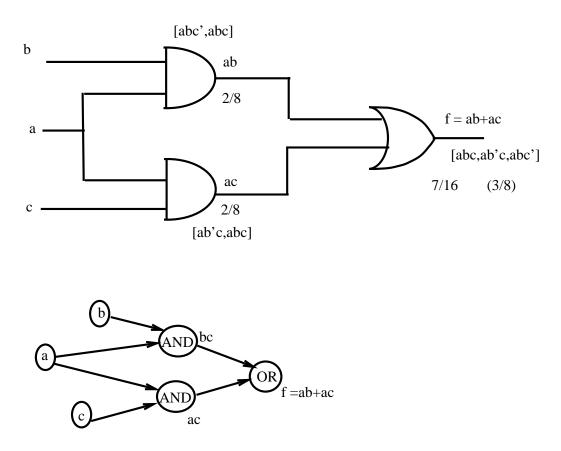

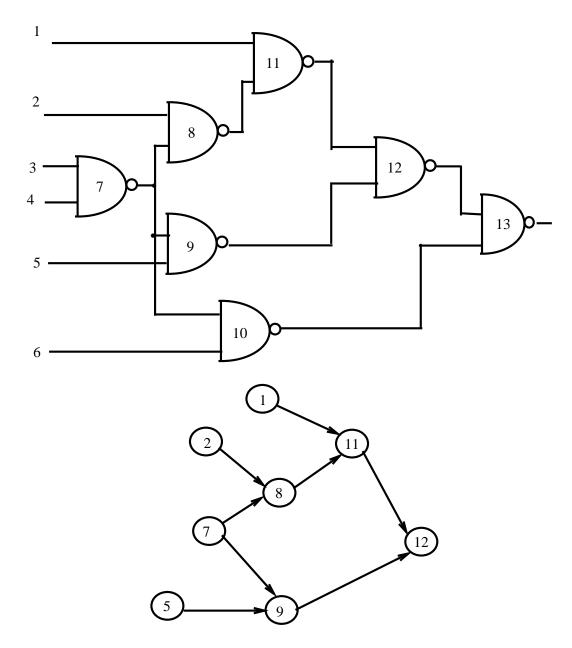

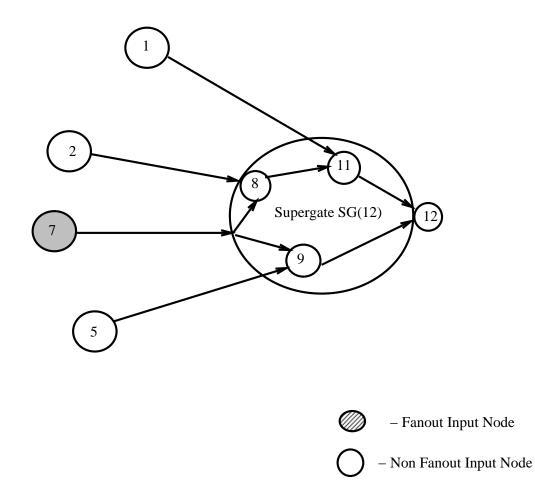

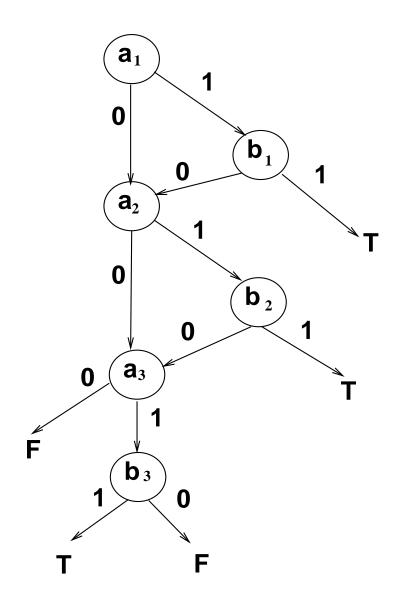

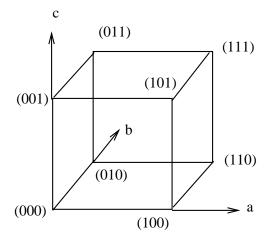

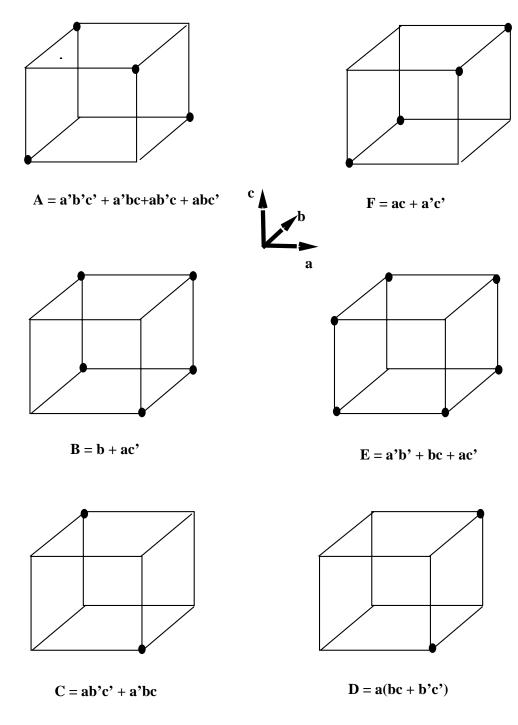

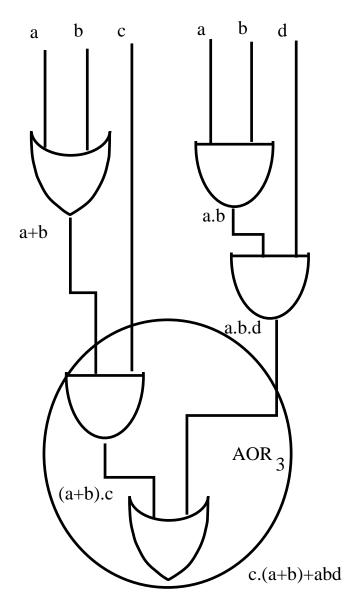

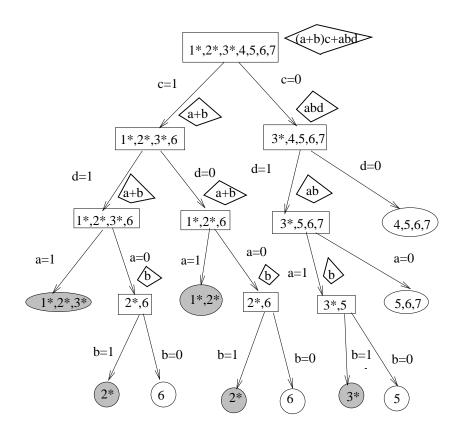

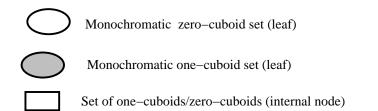

We start with a description of our circuit model. A circuit is represented as a directed weighted graph  $G = \langle V, E, L \rangle$ . Each primary input, primary output, and logic gate in the circuit is represented by a node  $v \in V$  in the graph. An edge  $(v, w) \in E$  represents a wire in the circuit. Each such edge has a length attribute  $l_{(v,w)} \in L$  that is the length of the wire.  $L: E \to \mathcal{R}$ , where  $\mathcal{R}$  is the set of real numbers. The direction of the edge, from v to w, represents the direction in which the bits travel in the wire. v is the source node and w is the destination node for the edge. The directed edges from vto other nodes are called *fanout* edges. v is the source node of these edges and the bits leave from v along these edges to go to destination fanout nodes. The directed edges that come into node v are called *fanin* edges. v is the destination node of these edges and the bits enter v along these edges from source fanin nodes. The primary input nodes have no fanin edges and the primary output nodes have no fanout edges. The number of fanin edges of a gate node is equal to the number of inputs to the gate. A *path* in the graph is a sequence of vertices from a source node to a destination node. The *support* set of a node v is the set of all primary inputs from which there is a path to node v. Figure 3.1 illustrates a simple circuit and its corresponding directed graph model. (The edge lengths are not shown).

We now refine the idea of dynamic communication effort by quantifying it with circuit attributes. To capture the distribution of boolean values at the node, we use the classical entropy function  $H(\{p_i\})$  from information theory

Figure 3.1: An Example Circuit and its Digraph Model

$[SW49] H(\{p_i\}) = \sum_{i=1}^{N} p_i \log(\frac{1}{p_i}). N \text{ represents the number of possible values} (or events) in a given system. Since there are only two values possible in a digital circuit we can model the distribution of boolean values computed at a node w by the binary entropy function <math>H(\{p_w^1, p_w^0\})$  at the node,

$$H(\{p_w^1, p_w^0\}) = p_w^0 \log(\frac{1}{p_w^0}) + p_w^1 \log(\frac{1}{p_w^1})$$

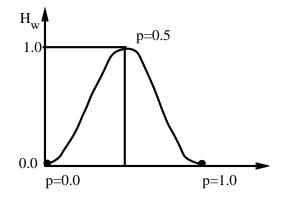

where  $p_w^1$  is the 1-probability of a node w, and  $p_w^0 = (1 - p_w^1)$  is the 0probability of the node. The probability of a node gives the distribution of 1 and 0 values computed by the node. This binary entropy function  $H(\{p_w^1, p_w^0\})$  denotes the *information* computed at the node over this probability distribution. We shall denote this function as  $H_w$ .

The function  $H_w$  quantifies the dynamic communication effort contributed by the node. Consider its plot shown in Figure 3.2. As we look at the extremities of this function we observe that the information  $H_w$  is a minimum when the 1-probability or 0-probability of a node is 1 or 0, while it is a maximum when  $p_w^0 = p_w^1 = 0.5$ . Assuming all inputs are equally likely, a 1-probability of 0.5 at a node w implies that for half the input values the node will have a value of 1 and for the other half the node will have a value of 0. This means that a gate modeled by this node will have to expend more effort in order to distinguish the ON-terms from the OFF-terms in order to compute the output value for a given input(s). On the other hand, a 1-probability of 1.0 implies that the node will have a value of 1 for all input values. This means that the gate does not have to expend any effort to compute the output since, given an input value, the gate automatically knows that it belongs to the ON-set. Thus the function  $H_w$  plotted in Figure 3.2 captures the effort expended by the gate in computing the boolean value at its output.

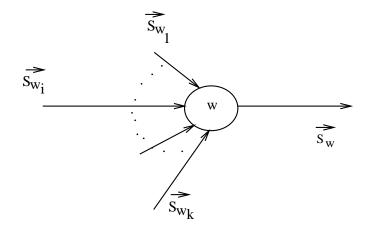

The distance traveled by the boolean values computed at a node is quantified by the length of a fanout edge from that node. The edge lengths in the graph quantify the wire lengths in the circuit in a straightforward manner. Long edge lengths imply long wires indicating more effort is expended in carrying the information from the gate. We now define the spatial entropy S for a circuit as follows.

**Definition 1** The spatial entropy S at the output node of a single output

Figure 3.2: The Entropy Function  $H_w$

circuit is the information-distance product over all the nodes in the circuit.

$$S = \sum_{v \in V} \sum_{w \in V} H_v * l_{(v,w)}$$

$H_v$  is the information computed at the node v over its input probability distribution, and  $l_{(v,w)}$  is the length of the fanout edge  $(v,w) \in E$ , from node v to node w.

The spatial entropy S of a multi-output circuit is expressed as  $S = \sum_{i=1}^{m} S_{o_i}$ , where m is the number of outputs and  $S_{o_i}$  is the spatial entropy at output  $o_i$ .

At each node v, the spatial entropy is computed by multiplying the information computed at v by the distance it has to travel along all the fanout edges from v. With this definition the intuitive notion of communication effort is captured by the total information flow in the circuit. The nodes compute the information while the edges communicate this information.