### ON THE DESIGN AND IMPLEMENTATION OF A CACHE-AWARE SOFT REAL-TIME SCHEDULER FOR MULTICORE PLATFORMS

#### John Michael Calandrino

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2009

Approved by:

James H. Anderson

Sanjoy Baruah

Scott Brandt

Kevin Jeffay

Ketan Mayer-Patel

Frank Mueller

© 2009 John Michael Calandrino ALL RIGHTS RESERVED

## ABSTRACT

JOHN MICHAEL CALANDRINO: On the Design and Implementation of a Cache-Aware Soft Real-Time Scheduler for Multicore Platforms (Under the direction of James H. Anderson)

Real-time systems are those for which timing constraints must be satisfied. In this dissertation, research on multiprocessor real-time systems is extended to support multicore platforms, which contain multiple processing cores on a single chip. Specifically, this dissertation focuses on designing a cache-aware real-time scheduler to reduce shared cache miss rates, and increase the level of shared cache reuse, on multicore platforms when timing constraints must be satisfied. This scheduler, implemented in Linux, employs: (1) a scheduling method for real-time workloads that satisfies timing constraints while making scheduling choices that reduce shared cache miss rates; and (2) a profiler that quantitatively approximates the cache impact of every task during its execution.

In experiments, it is shown that the proposed cache-aware scheduler can result in significantly reduced shared cache miss rates over other approaches. This is especially true when sufficient hardware support is provided, primarily in the form of cache-related performance monitoring features. It is also shown that scheduler-related overheads are comparable to other scheduling approaches, and therefore overheads would not be expected to offset any reduction in cache miss rate. Finally, in experiments involving a multimedia server workload, it was found that the use of the proposed cache-aware scheduler allowed the size of the workload to be increased.

Prior work in the area of cache-aware scheduling for multicore platforms has not addressed support for real-time workloads, and prior work in the area of real-time scheduling has not addressed shared caches on multicore platforms. For real-time workloads running on multicore platforms, a decrease in shared cache miss rates can result in a corresponding decrease in execution times, which may allow a larger real-time workload to be supported, or hardware

requirements (or costs) to be reduced. As multicore platforms are becoming ubiquitous in many domains, including those in which real-time constraints must be satisfied, cache-aware scheduling approaches such as that presented in this dissertation are of growing importance. If the chip manufacturing industry continues to adhere to the multicore paradigm (which is likely, given current projections), then such approaches should remain relevant as processors evolve.

To Liz, who will always be my constant.

# ACKNOWLEDGMENTS

Neither this dissertation nor my graduate school career would have been possible without the help of a lot of people. I would first like to thank my committee: James Anderson, Sanjoy Baruah, Scott Brandt, Kevin Jeffay, Ketan Mayer-Patel, and Frank Mueller, for their help and feedback along the way. I would especially like to thank Jim, who was also my advisor and committee chair, for transforming a graduate student that had a less-than-perfect experience at Cornell into one that can both "do research" and really enjoy it at the same time. I would also like to thank the former and current real-time graduate students at UNC that I have known for their contributions to my transformation: Aaron Block, Björn Brandenburg, Uma Devi, Hennadiy Leontyev, Cong Liu, and Glenn Elliott; I would thank those with whom I have co-authored papers a second time. The real-time community as a whole also deserves credit—they have made most of my conference experiences a lot of fun, and I have been excited to be part of their research community over the last few years. My collaborators at Intel also deserve a large amount of credit for shaping the direction of the research that is presented in this dissertation: Scott Hahn, Dan Baumberger, Tong Li, and Jessica Young. Their advice was invaluable, and without their help and assistance during both my internship in the summer of 2006 and the visits that followed, I think that this dissertation would have been less interesting. I would also like to thank the UNC Department of Computer Science as a whole, which in my opinion offers an unusually positive and friendly environment in which to be a graduate student in computer science. I have also had some great teachers during my time in the department, where I believe that I learned more about computer science during two years of taking courses at UNC than I had learned during my previous six years as a student.

There are also those outside of the field of computer science that deserve credit for this dissertation. I would like to thank everyone at the UNC Institute of Marine Sciences (IMS),

located on the North Carolina coast, where my wife was a graduate student. The people there were very supportive of me, especially during the summer of 2008, when I implemented a large portion of the cache-aware scheduler that is described in this dissertation while sitting at a desk at IMS. While I was at the coast, I essentially became an honorary IMS graduate student, thanks in part to my wife's roommates at the coast: Sandra Mesquita and Angie Coulliette. Finally, I would like to thank my wife, Liz, for (at least) the following: (1) an incredible amount of support; (2) tolerating someone that wanted to spend eleven years as a student; and (3) making sure that I always had plenty of homemade baked goods. The ongoing scavenger hunt that we have for National Park stamps made this dissertation possible in its own way as well.

Thanks again everyone, and enjoy the dissertation.

# TABLE OF CONTENTS

| LI | LIST OF TABLES  LIST OF FIGURES   |        |                                               |    |  |  |

|----|-----------------------------------|--------|-----------------------------------------------|----|--|--|

| LI |                                   |        |                                               |    |  |  |

| 1  | INTRODUCTION                      |        |                                               |    |  |  |

|    | 1.1                               | Real-7 | Γime Systems                                  | 2  |  |  |

|    | 1.2                               | Multio | core Architectures                            | 3  |  |  |

|    |                                   | 1.2.1  | Shared Caches                                 | 3  |  |  |

|    |                                   | 1.2.2  | Related Work                                  | 6  |  |  |

|    | 1.3                               | Applio | cation Domains                                | 8  |  |  |

|    |                                   | 1.3.1  | Multimedia Applications                       | 8  |  |  |

|    |                                   | 1.3.2  | Gaming and Real-Time Graphics                 | 9  |  |  |

|    |                                   | 1.3.3  | High-Performance Computing                    | 10 |  |  |

|    | 1.4                               | Thesis | s Statement                                   | 10 |  |  |

|    | 1.5                               | Contri | ibutions                                      | 11 |  |  |

|    |                                   | 1.5.1  | Cache-Aware Real-Time Scheduling Methods      | 11 |  |  |

|    |                                   | 1.5.2  | Online Cache Profiling of Real-Time Workloads | 12 |  |  |

|    |                                   | 1.5.3  | Implementation and Evaluation                 | 12 |  |  |

|    | 1.6                               | Organ  | nization                                      | 13 |  |  |

| 2  | PR                                | IOR W  | VORK                                          | 14 |  |  |

|    | 2.1 Real-Time Scheduling Overview |        | Γime Scheduling Overview                      | 14 |  |  |

|    |                                   | 2.1.1  | Recurrent Task Model                          | 14 |  |  |

|    |                                   | 2.1.2  | Hard vs. Soft Real-Time Systems               | 16 |  |  |

|    |                                   | 2.1.3  | Uniprocessor Scheduling                       | 19 |  |  |

|     | 2.1.4  | Multipre  | ocessor Scheduling                        | 20 |

|-----|--------|-----------|-------------------------------------------|----|

|     | 2.1.5  | Global S  | Scheduling                                | 22 |

|     | 2.1.6  | Tardines  | ss Bounds Under Global Scheduling         | 24 |

|     | 2.1.7  | Pfair Sc  | heduling                                  | 27 |

|     | 2.1.8  | Early-R   | eleasing                                  | 32 |

|     | 2.1.9  | Impact    | of Overheads                              | 32 |

| 2.2 | Cache  | -Aware N  | Ion-Real-Time Scheduling and Profiling    | 34 |

|     | 2.2.1  | Caches:   | An Introduction                           | 35 |

|     |        | 2.2.1.1   | The ABCs of Caches                        | 35 |

|     |        | 2.2.1.2   | Cache Misses                              | 36 |

|     |        | 2.2.1.3   | Physically and Virtually Addressed Caches | 39 |

|     | 2.2.2  | Assessin  | g the Cache Behavior of Tasks             | 40 |

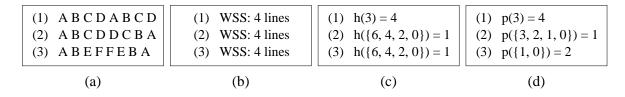

|     |        | 2.2.2.1   | Working Set Size                          | 41 |

|     |        | 2.2.2.2   | Reuse Distance                            | 41 |

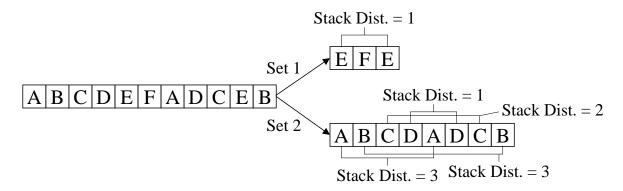

|     |        | 2.2.2.3   | Stack Distance                            | 43 |

|     |        | 2.2.2.4   | Comparison                                | 46 |

|     | 2.2.3  | Shared    | Cache Behavior: Task Co-Scheduling        | 47 |

|     |        | 2.2.3.1   | Combining Reuse Distance Histograms       | 47 |

|     |        | 2.2.3.2   | Redefining Reuse Distance                 | 49 |

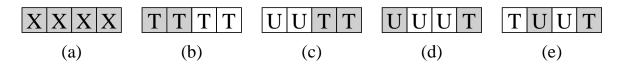

|     |        | 2.2.3.3   | Using Stack Distance Profiles             | 51 |

|     |        | 2.2.3.4   | Performance Counters                      | 53 |

| 2.3 | Real-7 | Time Ope  | erating Systems                           | 54 |

|     | 2.3.1  | LITMU     | $	ext{JS}^{	ext{RT}}$                     | 54 |

|     | 2.3.2  | RTLinux   | x                                         | 55 |

|     | 2.3.3  | Multipro  | ocessor RTOSs                             | 55 |

|     | 2.3.4  | Linux R   | teal-Time Preempt Patch                   | 56 |

| 2.4 | Real-7 | Time Sche | eduling on Multithreaded Platforms        | 56 |

| 2.5 | Concl  | usion     |                                           | 58 |

| 3 | $\mathbf{PR}$ | OBLEM STATEMENT                                             | <b>5</b> 9 |  |

|---|---------------|-------------------------------------------------------------|------------|--|

|   | 3.1           | The Problem: Cache-Aware Real-Time Co-Scheduling            | 59         |  |

|   |               | 3.1.1 Multithreaded Tasks                                   | 59         |  |

|   |               | 3.1.2 Problem Statement                                     | 63         |  |

|   |               | 3.1.3 NP-Hardness Proof for CARTCP                          | 63         |  |

|   | 3.2           | Early Approaches                                            | 65         |  |

|   |               | 3.2.1 Preventing Thrashing With Megatasks                   | 65         |  |

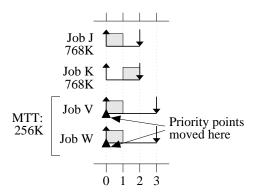

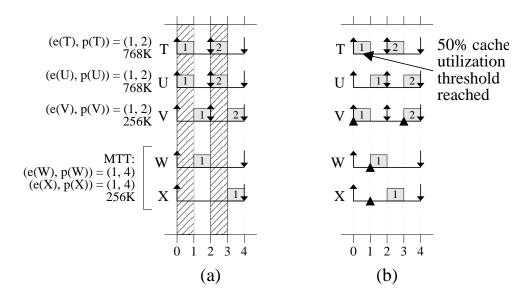

|   |               | 3.2.2 Encouraging MTT Co-Scheduling Through Early-Releasing | 72         |  |

|   |               | 3.2.3 Problems With Combining These Methods                 | 84         |  |

|   | 3.3           | Conclusion                                                  | 84         |  |

| 4 | CA            | CHE-AWARE REAL-TIME SCHEDULING                              | 85         |  |

|   | 4.1           | Influencing Co-Scheduling: Job Promotions                   | 85         |  |

|   | 4.2           | Promotion Heuristics                                        | 87         |  |

|   |               | 4.2.1 Common Rules                                          | 88         |  |

|   |               | 4.2.2 Policies                                              | 92         |  |

|   | 4.3           | Tardiness Bound                                             | 98         |  |

|   | 4.4           | Hiding Tardiness Through Early Releasing and Buffering      | 98         |  |

|   | 4.5           | Implemented Heuristic                                       | 101        |  |

|   | 4.6           | Conclusion                                                  | 104        |  |

| 5 | CA            | CHE PROFILING FOR REAL-TIME TASKS                           | L06        |  |

|   | 5.1           | Overview                                                    | 106        |  |

|   |               | 5.1.1 WSS as a Cache Behavior Metric                        | 107        |  |

|   |               | 5.1.2 Performance Counters                                  | 107        |  |

|   | 5.2           | Assumptions                                                 | 109        |  |

|   | 5.3           | Estimating MTT WSS                                          |            |  |

|   |               | 5.3.1 WSS Versus Cache Footprint                            | 111        |  |

|   |               | 5.3.2 Bootstrapping the Profiler                            | 112        |  |

|   |               | 5.3.3 Profiler Pseudo-code                                  | 115        |  |

|    | 5.4 | Conclu | usion                                        | 117 |

|----|-----|--------|----------------------------------------------|-----|

| 6  | EVA | ALUAT  | ΓΙΟΝ                                         | 118 |

|    | 6.1 | SESC-  | -Based Experiments                           | 118 |

|    |     | 6.1.1  | Example Task Sets                            | 120 |

|    |     | 6.1.2  | Randomly-Generated Task Sets                 | 122 |

|    |     | 6.1.3  | Video Encoding: A Case Study                 | 127 |

|    |     | 6.1.4  | Implementation Concerns                      | 129 |

|    | 6.2 | LITM   | IUS <sup>RT</sup> -Based Experiments         | 134 |

|    |     | 6.2.1  | Accuracy of WSS Estimates                    | 136 |

|    |     |        | 6.2.1.1 Machine A                            | 145 |

|    |     |        | 6.2.1.2 Machine B                            | 146 |

|    |     |        | 6.2.1.3 Machine C                            | 147 |

|    |     |        | 6.2.1.4 Summary                              | 149 |

|    |     | 6.2.2  | Performance Versus GEDF                      | 149 |

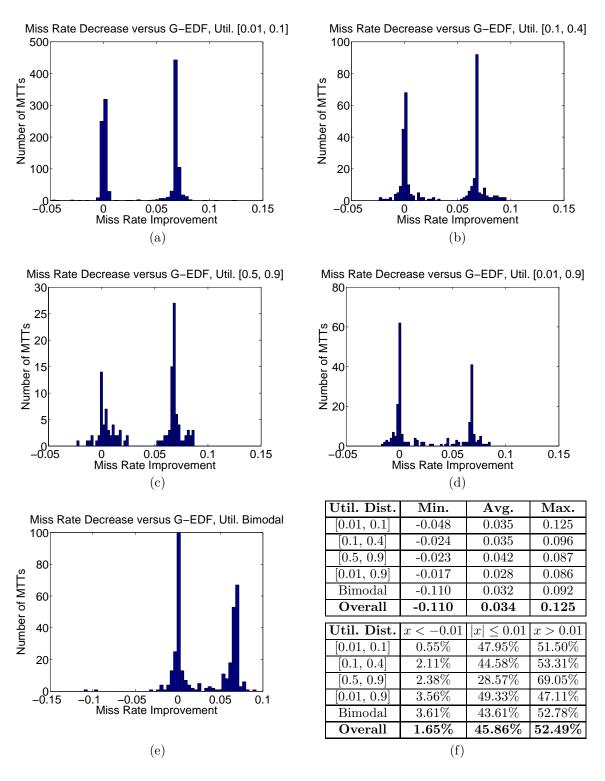

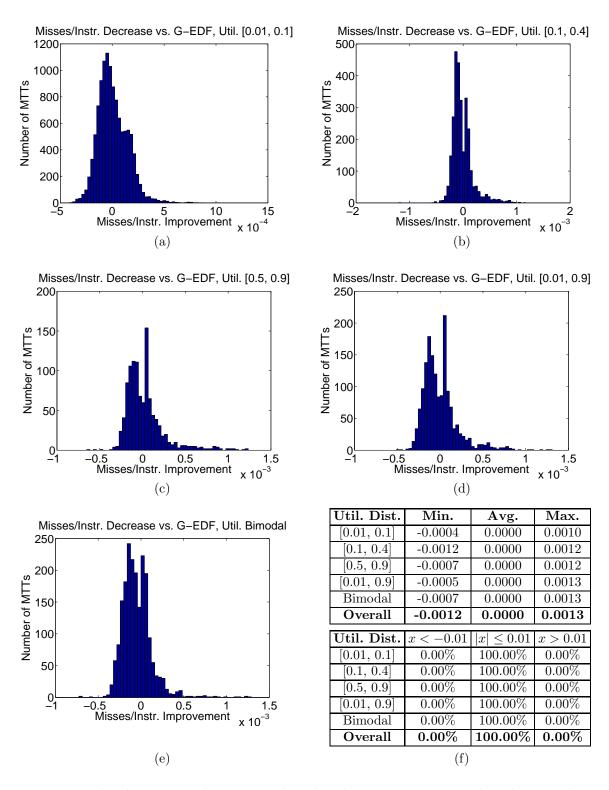

|    |     |        | 6.2.2.1 Average-Case Cache Miss Rate         | 150 |

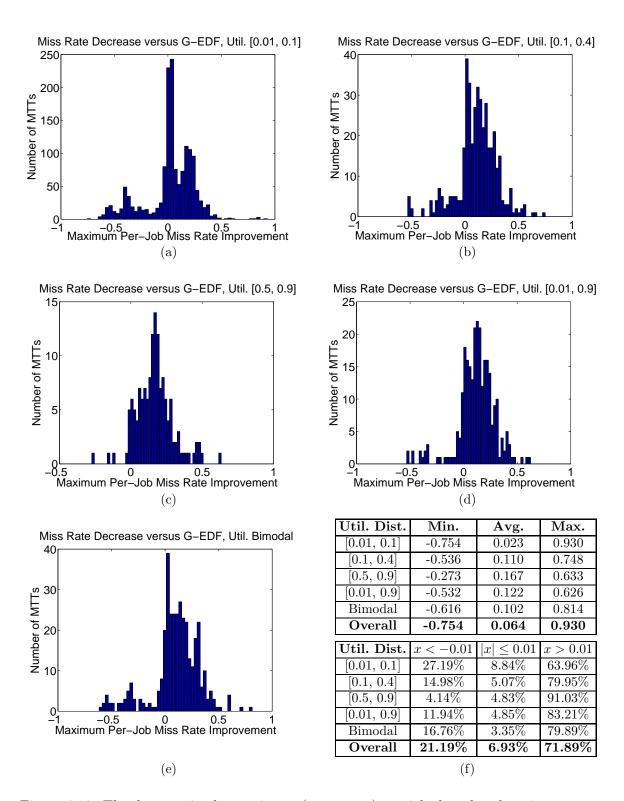

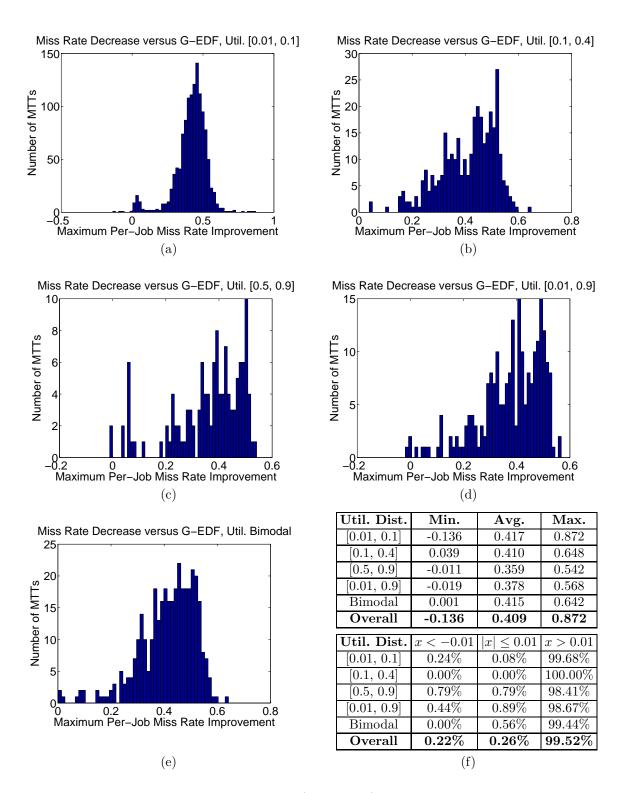

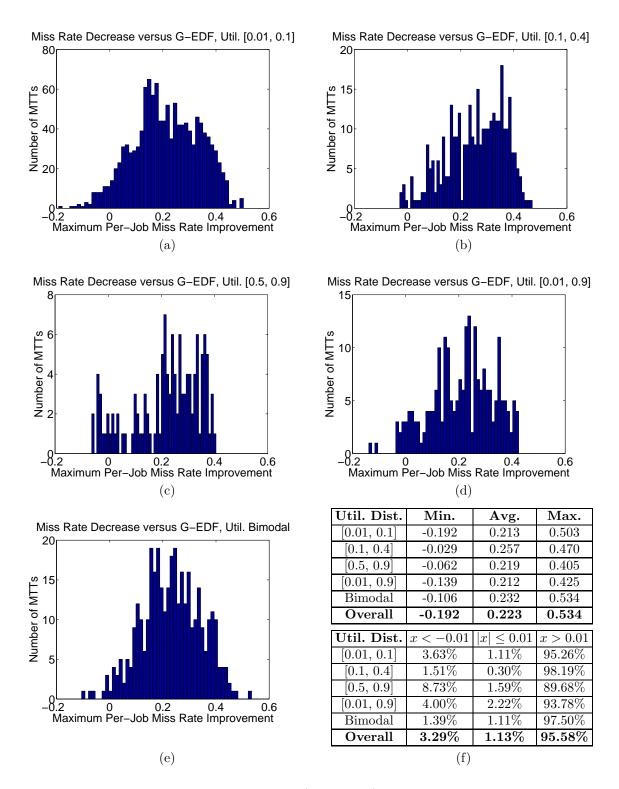

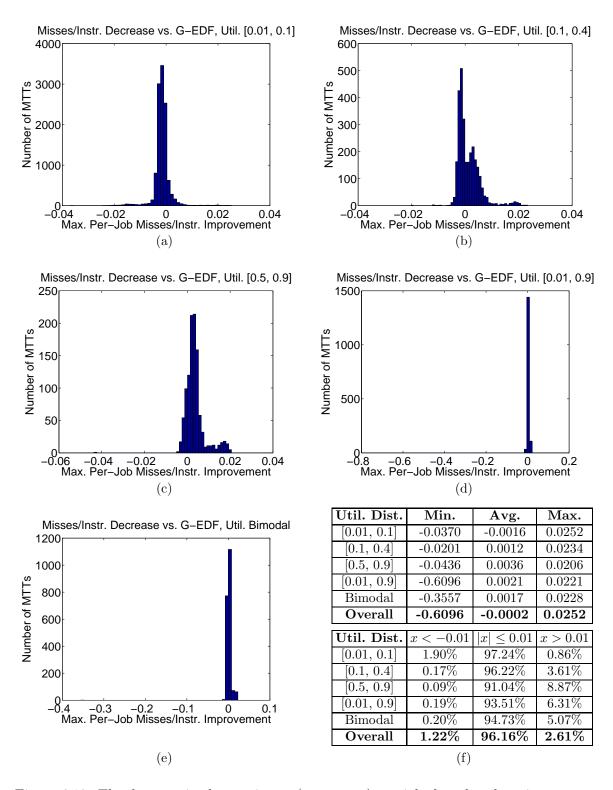

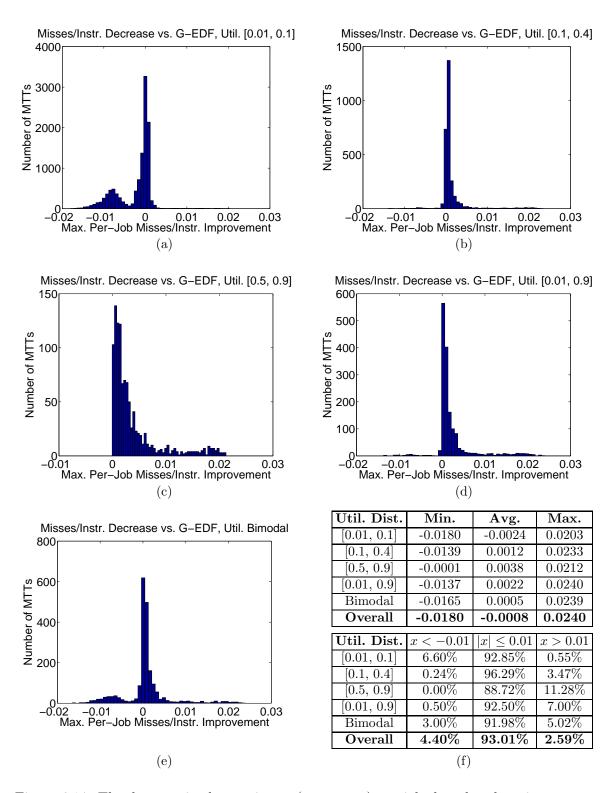

|    |     |        | 6.2.2.2 Worst-Case Cache Miss Rate           | 156 |

|    |     |        | 6.2.2.3 Deadline Tardiness                   | 163 |

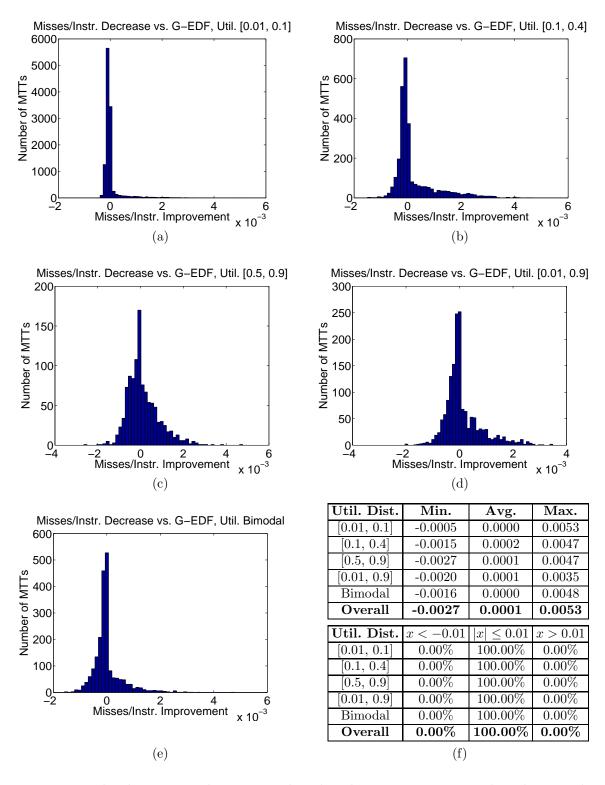

|    |     |        | 6.2.2.4 Scheduling Overhead                  | 164 |

|    |     | 6.2.3  | Multimedia Application Performance           | 165 |

|    | 6.3 | Conclu | usion                                        | 167 |

| 7  | COI | NCLU   | SION AND FUTURE WORK                         | 169 |

|    | 7.1 | Summ   | nary of Results                              | 169 |

|    | 7.2 | Other  | Contributions                                | 171 |

|    |     | 7.2.1  | Real-Time Scheduling on Asymmetric Platforms | 171 |

|    |     | 7.2.2  | The LinSched Linux Scheduler Simulator       | 172 |

|    | 7.3 | Feedba | ack to Chip Designers                        | 173 |

|    | 7.4 | Future | e Work                                       | 173 |

| ΒI | BLI | OGRA   | РНҮ                                          | 181 |

# LIST OF TABLES

| 2.1  | Categorization of cache misses for a reference pattern           | 38  |

|------|------------------------------------------------------------------|-----|

| 2.2  | Stack distance profiles for tasks $T$ and $U$                    | 52  |

| 3.1  | Properties of example task sets                                  | 70  |

| 3.2  | L2 cache miss rations for example task sets                      | 70  |

| 3.3  | Spread under $PD^2$ with and without the method in [3]           | 79  |

| 5.1  | The architectural performance events of Intel processors         | 107 |

| 5.2  | The performance events of the UltraSPARC T1 processor            | 108 |

| 6.1  | Shared cache performance for example task sets                   | 120 |

| 6.2  | The heuristics that performed best for random task sets          | 124 |

| 6.3  | Tardiness for GEDF and our heuristics                            | 125 |

| 6.4  | Evaluation of one of our heuristics for the 32-core architecture | 126 |

| 6.5  | Video quality levels and their corresponding MTTs                | 129 |

| 6.6  | Results for video-encoding MTTs                                  | 130 |

| 6.7  | The impact of avoiding difficult-to-implement policies           | 131 |

| 6.8  | Attributes of machines on which experiments were performed       | 135 |

| 6.9  | Deadline tardiness results                                       | 163 |

| 6.10 | Average and worst-case kernel overheads                          | 166 |

| 6.11 | Worst-case execution times for <i>mplayer</i> applications       | 166 |

# LIST OF FIGURES

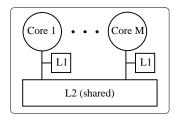

| 1.1  | An example multicore architecture                                                    | 4  |

|------|--------------------------------------------------------------------------------------|----|

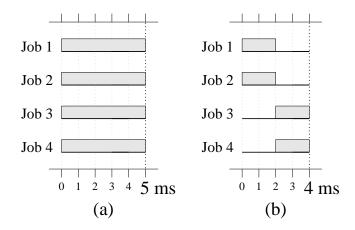

| 1.2  | The impact of co-scheduling on shared cache thrashing                                | 5  |

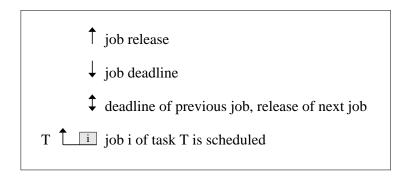

| 2.1  | Conventions used in example schedules throughout this dissertation                   | 15 |

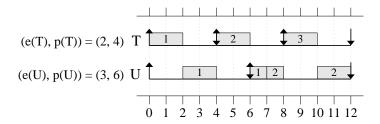

| 2.2  | An example schedule for a periodic task system                                       | 15 |

| 2.3  | Comparison of percentage-based and $(m,k)$ -firm guarantees                          | 18 |

| 2.4  | An EDF schedule for the task set in Figure 2.2                                       | 20 |

| 2.5  | An example of how bin-packing affects schedulability                                 | 21 |

| 2.6  | Two-core GEDF and NP-GEDF schedules for the same task set                            | 23 |

| 2.7  | An example policy demonstrating the power of priority points                         | 26 |

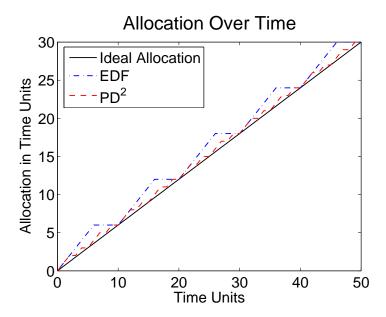

| 2.8  | Allocation over time for a single task under an ideal allocation, $EDF,$ and $PD^2.$ | 28 |

| 2.9  | Pfair window layout for a task with an execution cost of six and period of ten.      | 29 |

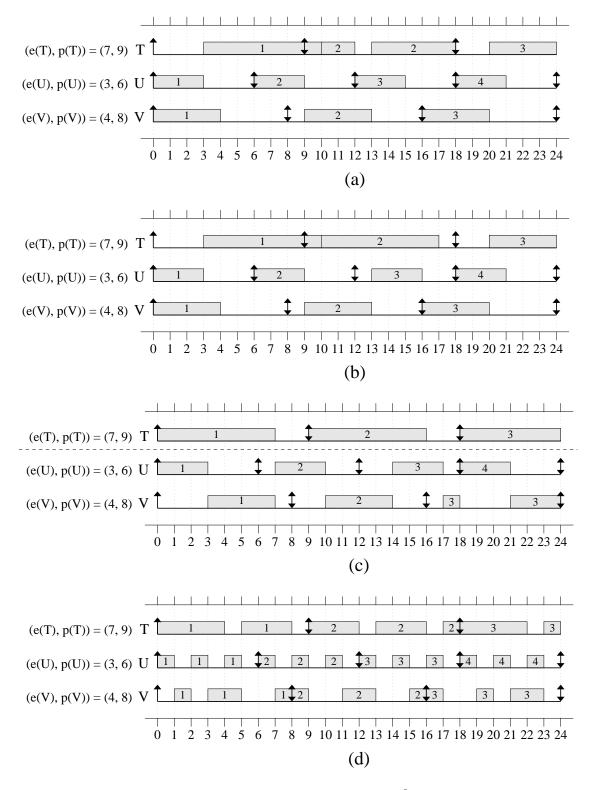

| 2.10 | Example schedules for different algorithms                                           | 31 |

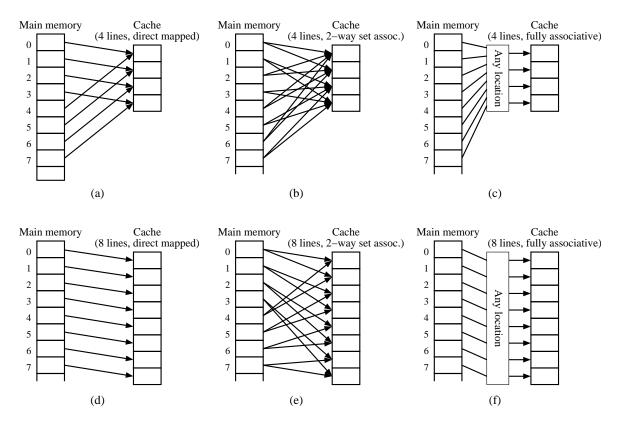

| 2.11 | Mappings to cache locations based on cache attributes                                | 37 |

| 2.12 | Stack distances for a given reference pattern                                        | 44 |

| 2.13 | Comparison of different metrics for representing the cache impact of tasks           | 47 |

| 2.14 | An example of how cache decay controls the amount of cache used by each task.        | 50 |

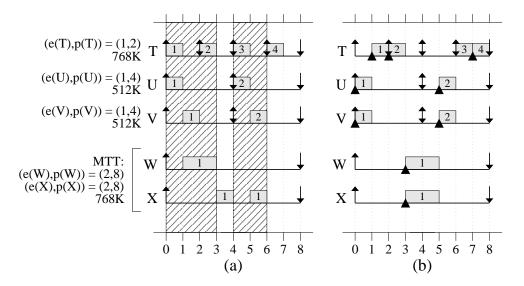

| 3.1  | The impact of forcing versus influencing MTT co-scheduling                           | 61 |

| 3.2  | An example of how megatasks can prevent cache thrashing                              | 67 |

| 3.3  | An example of how deadline misses can occur when using megatasks                     | 67 |

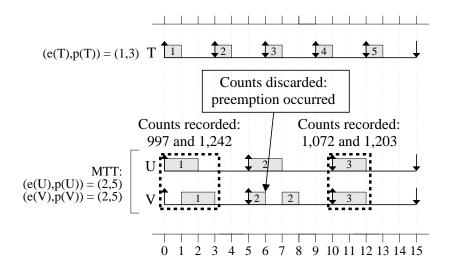

| 3.4  | Two-core $PD^2$ schedules with early-releasing                                       | 74 |

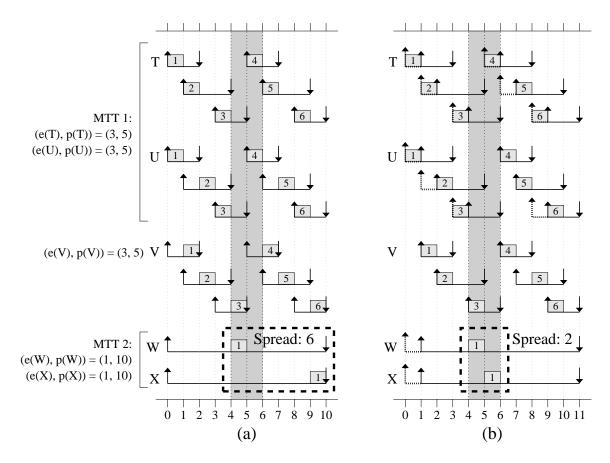

| 3.5  | An example of how our scheduling rules reduce spread                                 | 77 |

| 3.6  | An example demonstrating the maximum execution time of a task under $GEDF.$          | 78 |

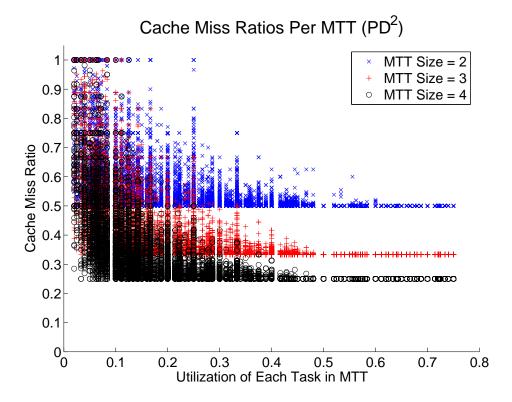

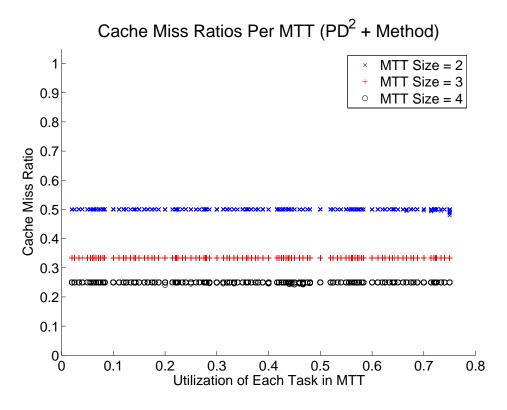

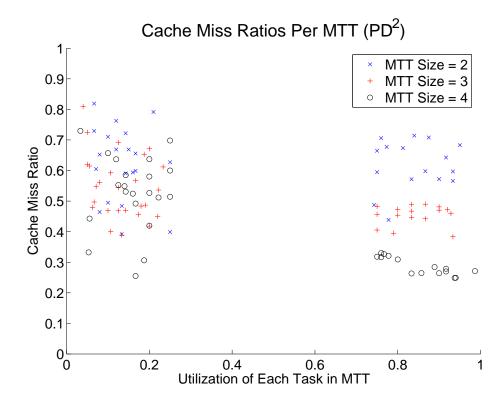

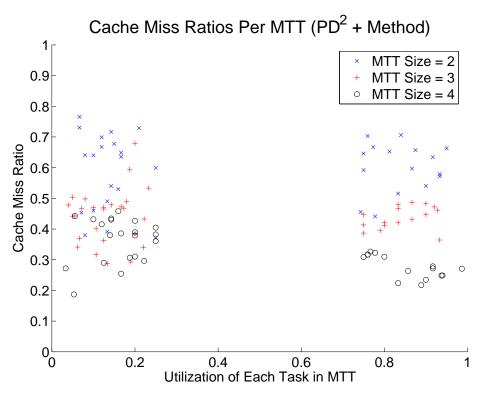

| 3.7  | Cache miss ratios for $PD^2$ with and without the method in [3] (simple model).      | 81 |

| 3.8  | Cache miss ratios for $PD^2$ with and without the method in [3] (SESC model).        | 83 |

| 4.1  | An example of where promoting jobs can reduce cache miss rates                       | 86 |

| 4.2  | Pseudo-code for all heuristics, invoked at every quantum boundary                | 90    |

|------|----------------------------------------------------------------------------------|-------|

| 4.3  | Two-core schedules for a set of five tasks                                       | 91    |

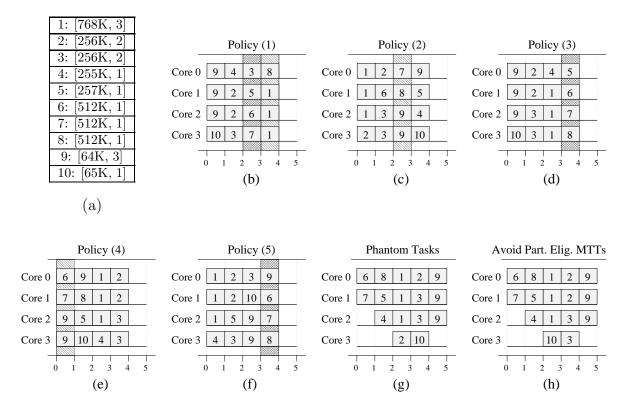

| 4.4  | Four-core schedules demonstrating a variety of cache-aware policies              | 95    |

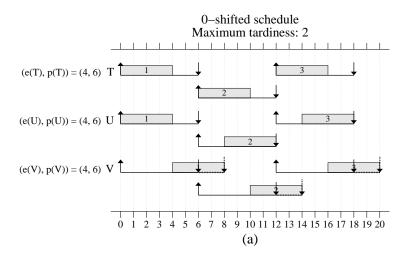

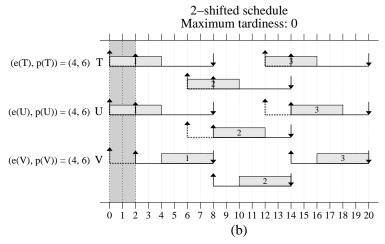

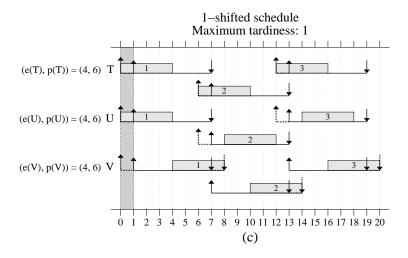

| 4.5  | Two-core schedules demonstrating how tardiness can be hidden                     | 100   |

| 4.6  | Two-core schedules for a set of five tasks under best-performing heuristic. $$ . | 102   |

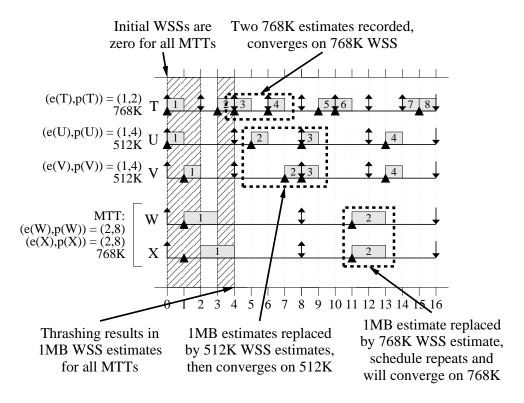

| 5.1  | Two-core example schedule demonstrating how the profiler collects information.   | . 111 |

| 5.2  | Two-core example schedule generated when our profiler is used                    | 113   |

| 5.3  | Pseudo-code for the cache profiler                                               | 116   |

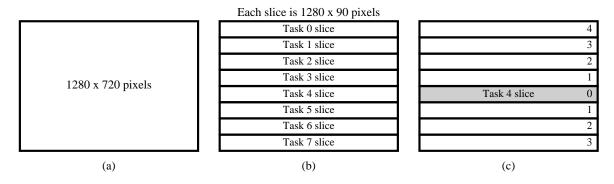

| 6.1  | The memory reference pattern for multithreaded motion estimation                 | 128   |

| 6.2  | Pseudo-code for each MTT                                                         | 139   |

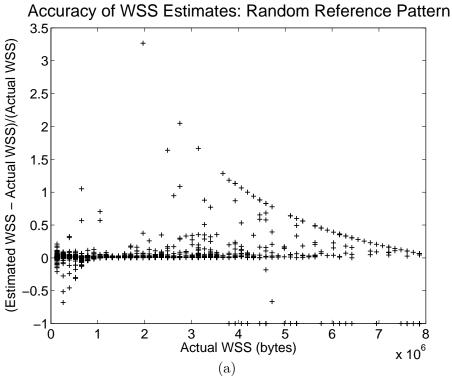

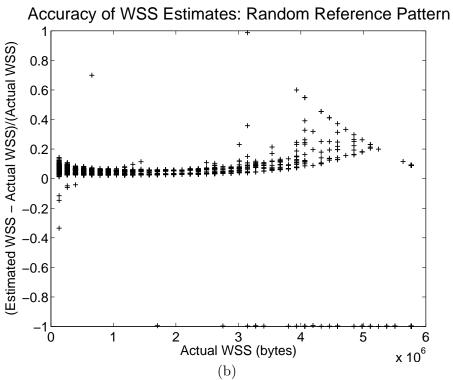

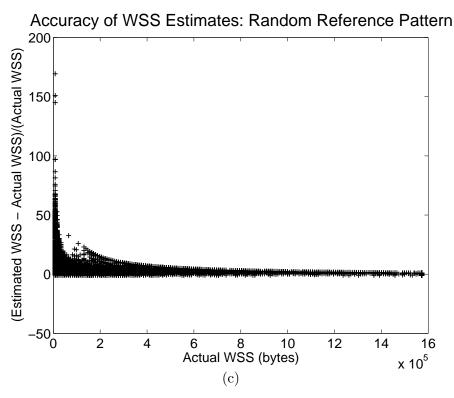

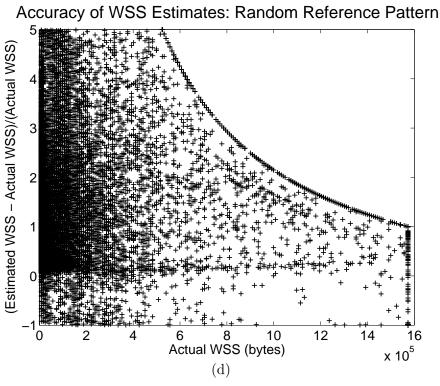

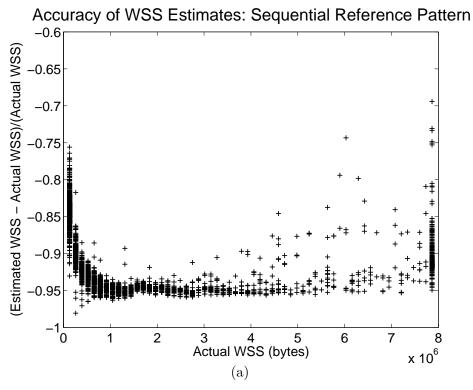

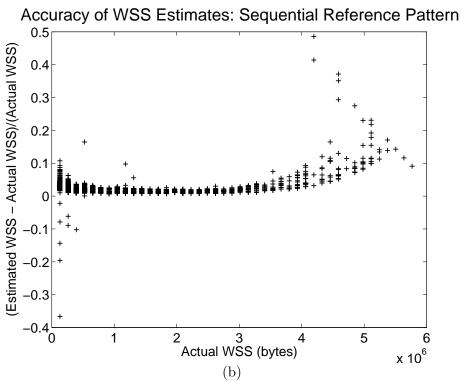

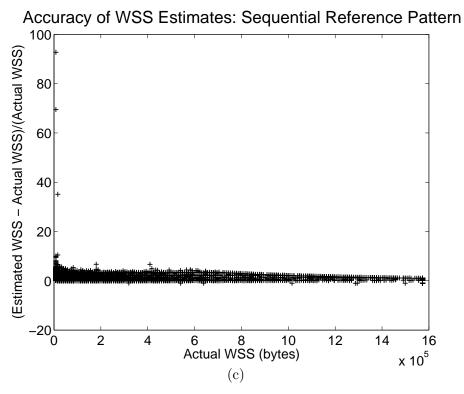

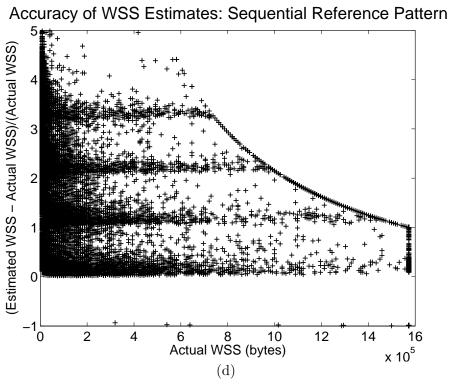

| 6.3  | Profiler accuracy as a function of MTT WSS (random pattern)                      | 141   |

| 6.4  | Profiler accuracy as a function of MTT WSS (sequential pattern)                  | 143   |

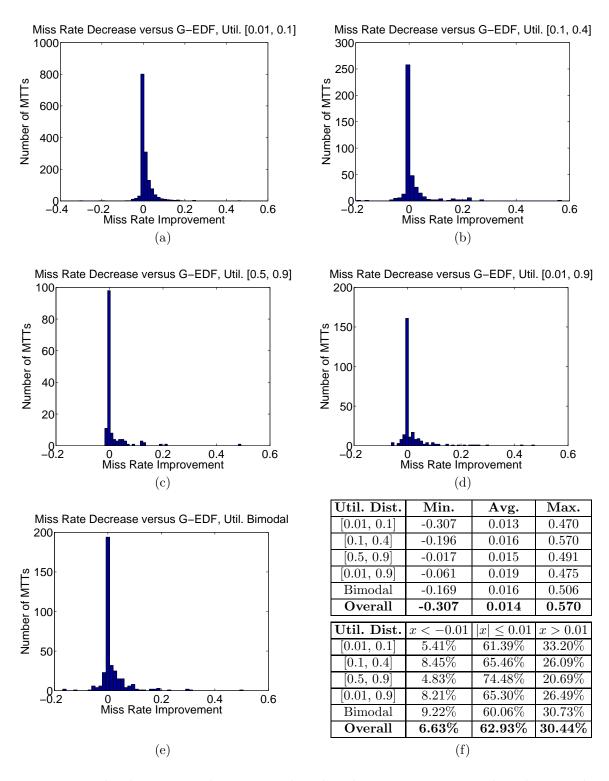

| 6.5  | Decrease in the average cache miss rate (machine A)                              | 151   |

| 6.6  | Decrease in the average cache miss rate (machine B, random pattern)              | 152   |

| 6.7  | Decrease in the average cache miss rate (machine B, sequential pattern)          | 153   |

| 6.8  | Decrease in the average cache miss rate (machine C, random pattern)              | 154   |

| 6.9  | Decrease in the average cache miss rate (machine C, sequential pattern)          | 155   |

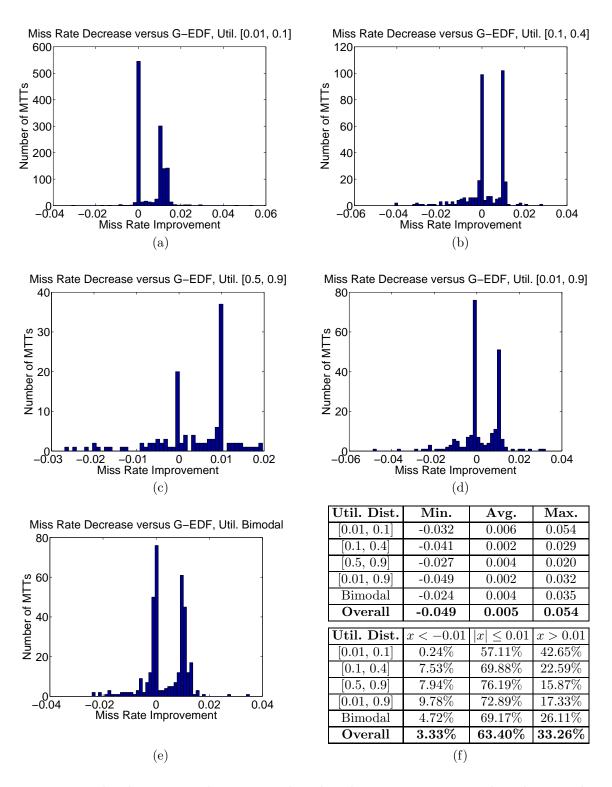

| 6.10 | Decrease in the worst-case cache miss rate (machine A)                           | 157   |

| 6.11 | Decrease in the worst-case cache miss rate (machine B, random pattern)           | 158   |

| 6.12 | Decrease in the worst-case cache miss rate (machine B, sequential pattern)       | 159   |

| 6.13 | Decrease in the worst-case cache miss rate (machine C, random pattern)           | 160   |

| 6.14 | Decrease in the worst-case cache miss rate (machine C, sequential pattern)       | 161   |

#### CHAPTER 1

## INTRODUCTION

Real-time systems are those for which timing constraints must be satisfied. The goal of this dissertation is to extend research on multiprocessor real-time systems to support multicore platforms, or platforms containing multiple processing cores on a single chip. This research is important as multicore platforms are quickly becoming ubiquitous in the desktop, server, and embedded domains—including in settings where real-time constraints must be satisfied. In this dissertation, our focus is on reducing the miss rates of shared caches, and increasing the level of reuse for these caches, within such platforms while ensuring the timing constraints of a real-time workload. In multicore platforms, reducing shared cache miss rates can result in decreased execution times, which may allow a larger real-time workload to be supported or hardware requirements (or costs) to be reduced. To this end, we developed a cache-aware real-time scheduler for Linux that employs: (1) a scheduling method for real-time workloads that satisfies timing constraints while making scheduling choices that reduce shared cache miss rates; and (2) a profiler that quantitatively approximates the cache impact of every task during its execution. The design and implementation of this scheduler is described herein. Note that the scheduling overheads that are associated with our implementation are of critical importance—otherwise, such overheads could offset any reduction in cache miss rates.

Prior to the research in this dissertation, no cache-aware real-time scheduling algorithm had been proposed that addresses these practical concerns—prior work on scheduling in the presence of shared caches on multicore platforms had not addressed support for real-time workloads, and prior work in the area of real-time scheduling had not addressed shared caches on multicore platforms. It is at the intersection of these two research areas that this dissertation makes its primary contribution.

In the sections that follow, we first provide an introduction to real-time systems. We then motivate the need for cache-aware real-time scheduling with an introduction to multicore architectures. This is followed with a discussion of target applications. We then state the thesis and contributions of this dissertation. Finally, we conclude by outlining how the remainder of this dissertation is organized.

## 1.1 Real-Time Systems

Real-time systems include a notion of temporal correctness in addition to logical correctness. That is, we not only want such systems to perform correct operations, but to perform them at the correct times. In other words, timing constraints must be ensured. For example, a video application might need to decode and display a video frame every 33 ms, in order for playback to look "smooth" to an end user when a (roughly) 30 frame-per-second frame rate is desired.

Most real-time workloads contain tasks that require computation time at recurring intervals. For example, the workload of the aforementioned video application could be represented as a sequence of consecutive 33 ms intervals, where a certain amount of computation time is required during each such interval. Such timing constraints would result in a natural division of the workload into recurring *jobs*, each with its own *deadline*. The scheduler must ensure that jobs are allocated sufficient processing capacity so that their timing constraints are met.

In recent years, interest in techniques for effectively scheduling real-time workloads on multiprocessor systems has been increasing for several reasons. First, recent research on this topic has led to the development of new scheduling approaches and analytical results that remove some of the theoretical constraints imposed by prior work. This research includes Pfair scheduling and the notion of bounded tardiness as an acceptable type of real-time guarantee; these concepts will be elaborated upon in Chapter 2. Second, multimedia applications, perhaps the most ubiquitous class of real-time applications, are increasing in complexity, and it may soon be impossible to achieve acceptable performance from such applications without explicitly providing real-time support within general-purpose operating systems. Third, as mentioned earlier, chip makers have been shifting to multicore processor designs.

More recently, a desire has been expressed to provide better real-time support within general-purpose operating systems such as Linux. These efforts have involved supporting recurrent task models natively within Linux, rather than attempting to emulate this support using the Portable Operating System Interface for Unix (POSIX) real-time extensions [68], which provide no support for recurrent workloads. Native support for recurrent task models would be especially useful for many applications that naturally exhibit such a pattern of execution, or that require a proportionate share of the available processing resources.

Given this convergence of events, the time is now ripe to extend prior work on techniques for scheduling real-time workloads on multiprocessors, particularly in ways that will benefit multicore platforms. The specific challenges associated with such platforms that are of concern to us in this dissertation are outlined next.

#### 1.2 Multicore Architectures

In multicore architectures, multiple processing cores are placed on the same chip. Most major chip manufacturers have adopted these architectures due to the thermal- and power-related limitations of single-core designs [50, 53]. Dual-core chips are now commonplace, and numerous four- and eight-core options exist. Further, per-chip core counts are expected to increase substantially in the coming years [53]. For example, Intel has claimed that it will release 80-core chips as early as 2013 [1]. Additionally, Azul, a company that creates machines for handling transaction-oriented workloads, currently offers the 54-core Vega 3 processor, which is used in systems with 864 total cores [7]. The shift to multicore technologies is a watershed event, as it fundamentally changes the "standard" computing platform in many settings to be a multiprocessor.

#### 1.2.1 Shared Caches

On most current multicore platforms, different cores share on-chip caches. Without effective management by the scheduler, such caches can become performance bottlenecks if cache thrashing is allowed to take place. Thrashing occurs when the demand for space in the shared cache (e.g., the amount of cache desired by all tasks scheduled at that time) outpaces the

Figure 1.1: Multicore architecture with a private L1 cache per core, and an L2 cache shared by all M cores.

cache size—as a result, tasks that are executing at that time experience high cache miss rates since their data is frequently evicted from the cache before it can be reused. In the case of a lower-level cache (i.e., a cache that is closer to main memory), this can result in high average memory reference times, due to a need to frequently access main memory, which is much slower than the cache. This, in turn, results in a severe overall degradation in system performance. For these reasons, the issue of efficient cache usage on multicore platforms is considered by chip makers to be one of the most important problems with which they are currently grappling. By effectively addressing this issue, the parallelism within these systems can be better exploited.

In this dissertation, we address this issue in the context of real-time systems implemented on a multicore platform where all cores are symmetric and share the lowest-level cache (i.e., the level of cache that is most distant from the cores, and closest to main memory), as shown in Figure 1.1. This architecture is fairly common—the Sun UltraSPARC T1 and T2 processors have a lowest-level L2 cache shared by eight cores, and the recently-released Intel Core i7 chip contains a lowest-level L3 cache shared by four cores (in this case, each core contains private L1 and L2 caches).

In prior work pertaining to non-real-time systems, Fedorova et al. [32] showed that shared cache miss rates affect overall system performance to a much greater extent than the performance of many other processor components. For example, for the chip shown in Figure 1.1, shared L2 misses would be expected to affect performance considerably more than private L1 misses or pipeline conflicts. This is precisely due to the severe performance degradation that would be expected when miss rates are high or thrashing occurs with respect to the lower-level caches, as noted earlier. At any given time, the miss rate of a shared cache at

Figure 1.2: The impact of co-scheduling on shared cache thrashing and response times.

time t is strongly determined by the set of applications co-scheduled at that time: a set of applications is said to be *co-scheduled* at some time t if they are scheduled concurrently at time t. Fedorova et al. showed that shared cache miss rates can be reduced, and system performance improved, by discouraging a set of applications from being co-scheduled when doing so would cause thrashing in the L2 cache.

Example (Figure 1.2). To demonstrate the impact of co-scheduling on shared cache thrashing, consider the example in Figure 1.2, where four jobs need to be scheduled on a four-core platform, and all four cores share a cache. Each job requires 2 ms of execution time when no cache thrashing occurs, or 5 ms of execution time if the cache is thrashed. Further, assume that at most two jobs can be co-scheduled without thrashing the cache. If all four jobs are co-scheduled, each on a different core, then thrashing occurs, and all jobs complete after 5 ms (inset (a)). However, if only two jobs are co-scheduled, then two jobs execute concurrently, followed by the other two jobs, resulting in all jobs completing after 4 ms (inset (b)). This example demonstrates that there are cases where we can achieve better system performance by reducing parallelism, if doing so avoids cache thrashing, instead of maximizing parallelism at all costs. An additional implication is that a cache management policy that is cognizant of these issues is likely to have a significant impact on system performance.

The problems addressed in this dissertation were initially motivated by the work of Fedorova et al.—we want to show that, in real-time systems, co-scheduling can be influenced in ways that reduce shared cache miss rates while ensuring real-time constraints. It is our

focus on real-time constraints that distinguishes our work from that of Fedorova *et al*. To the best of our knowledge, we are the first to consider mechanisms for influencing co-scheduling choices when analysis *validating* real-time constraints is required.

Additionally, our methods take this work one step further by *encouraging* the co-scheduling of applications when it would *reduce* shared cache miss rates, typically because the applications (or the individual tasks associated with such applications) reference the same data in memory. The benefit of encouraging co-scheduling in these cases is that it increases opportunities for data in the cache to be reused.

The general problem of influencing co-scheduling in these ways while respecting real-time constraints is NP-hard in the strong sense. (This is unlikely to be a surprise to the reader, as many multi-dimensional scheduling problems are similarly difficult.) In Chapter 3, we present a formal statement of this co-scheduling problem, and prove that it is NP-hard in the strong sense, by a transformation from 3-PARTITION.

#### 1.2.2 Related Work

Substantial additional prior work exists that is related to this co-scheduling problem, especially in the non-real-time domain. We briefly present only a few examples here—a larger body of work is considered in Chapter 2.

Batat and Feitelson [10] found that memory requirements should be taken into account during the co-scheduling of a multithreaded application—specifically, that it is more efficient to delay the execution of some threads when memory requirements cannot be met than to execute all threads concurrently, even if this results in a loss of processing capacity. This study (which did not consider real-time requirements) is particularly interesting considering that we take a similar approach to co-scheduling, which we elaborate upon further later in this dissertation.

In work on parallel computing, Peng et al. [55] found that the memory-reference patterns of threads can lead to co-scheduling choices that are either constructive or disruptive. Constructive choices, such as co-scheduling applications that share data, decrease shared cache miss rates, while disruptive choices increase miss rates. Scenarios should be avoided where

the benefits of parallelization are offset by disruptive co-scheduling choices—in our case, those that lead to shared cache thrashing or high shared cache miss rates. To this end, the authors of [55] conducted a study to determine the memory reference patterns for multimedia and artificial intelligence applications. The results of this study can assist in making better co-scheduling decisions involving these large application classes.

Cache fairness. In another paper by Fedorova et al. [33] (with significant overlap with the authors of [32]), a cache-aware scheduling approach is proposed that encourages cache fairness, or fair allocation of a shared cache among threads. Quality-of-service requirements, such as those related to thread completion times, are considered only experimentally, and are primarily motivated by cache fairness; no real-time analysis is presented. Other research in the area of cache fairness includes work of Kim et al. [42], who quantified cache fairness using several different metrics, and presented a cache-partitioning scheme that uniformly distributes the impact of cache contention among co-scheduled threads.

Symbiosis-aware scheduling. Additional related work that lacks real-time analysis includes work on *symbiosis-aware scheduling* [40, 60, 52] in (non-multicore) systems where multiple hardware threads contend for shared resources within the same single-core chip. In symbiosis-aware scheduling, the goal typically is to maximize the overall "symbiosis factor," which indicates how well various thread groupings perform when co-scheduled, where performance is primarily determined by per-thread execution times.

Worst-case execution time analysis. Work also exists that is related to shared-cache-aware real-time worst-case execution time (WCET) analysis, where an upper bound on the execution time of a single job of a task is derived (e.g., in [57, 54]). Such work may be considered to be more in line with the goals of this dissertation; however, this work only tangentially addresses cache-aware real-time scheduling, and does not address the issue of efficiently profiling the cache behavior of real-time tasks during execution.

## 1.3 Application Domains

In this section, we describe several application domains that may benefit from the cache-aware real-time scheduling support described in this dissertation.

#### 1.3.1 Multimedia Applications

Multimedia applications are the most obvious beneficiary of this work. Such applications comprise one of the most ubiquitous types of real-time workloads, especially within general-purpose operating systems such as Linux, and are very likely to run on multicore platforms for that reason. Given the current multicore trend, these applications will need to become multithreaded as the demanded video quality increases, and there will exist a need to correctly coordinate the timing of these threads.

Video encoding applications have real-time constraints and are both compute- and memory-intensive. Most video encoding requires a search as part of motion estimation. Within a multimedia server that encodes live media streams (each encoded by a separate application that corresponds to a one or more real-time tasks), a reduction in cache miss rates may allow more memory to be referenced and a more extensive search to be conducted in the same amount of execution time, thus improving video quality. Alternately, our cache-aware scheduler may reduce thrashing and result in lower execution-time requirements. This, in turn, would allow a greater selection of media streams, or a greater number of clients, to be supported without upgrading hardware.

One envisioned application of larger multicore platforms is to act as *multi-purpose home* appliances, where the computing requirements of a household are pooled into a single powerful general-purpose machine [38]. The cost savings of such an approach could be substantial. Such computing requirements may include:

• Supporting a wide variety of multimedia applications (e.g., streaming from multiple live and stored video sources to displays throughout the home, recording video for playback later, or supporting videoconferencing sessions). Video sources could include live broadcast television, on-demand services, or the Internet.

- Periodically monitoring various conditions of the home, such as temperature, and responding appropriately.

- Providing general-purpose computing capability as it is needed, perhaps through one or more user terminals that would emulate the functionality of a desktop system.

Naturally, the multimedia demands on such an appliance could be considerable, requiring a large number of high-quality (e.g., HDTV) video encoding and decoding applications to be concurrently supported. In such an environment, providing real-time guarantees for such applications would be a more direct way of supporting their computing needs, potentially resulting in more efficient use of the underlying general-purpose hardware. This, in turn, could make multi-purpose home appliances more viable, or increase their capabilities. Ultimately, reductions in cache miss rates could directly translate into an improved experience for the end users of the services provided by such appliances.

#### 1.3.2 Gaming and Real-Time Graphics

Real-time graphics applications are typically assisted by graphics processing units (GPUs). Due to the nature of GPU hardware and graphics processing, such applications tend to be inherently parallel (*i.e.*, multithreaded) and memory-intensive. These applications also have real-time requirements (hence their name, and the need for GPU assistance), and are likely to run alongside other applications on the same platform. By reducing the execution-time requirements for such applications through the use of our cache-aware scheduler (which could be used to manage any similar "cache-like" memory within GPUs), the processor-intensive applications typically associated with real-time graphics and gaming could be made viable on less-powerful platforms.

Two additional trends are of note. First, applications with similar characteristics to those commonly supported for real-time graphics may also see a performance benefit as interest in treating GPUs as co-processors for general computation continues to increase [34]. Second, if the core counts of CPUs increase as projected, and cores become simpler or more specialized, then the research within this dissertation might enable high-quality real-time graphics to be supported without the need for a specialized GPU or other hardware. Similarly, the cost of

specially-designed hardware (e.g., within video game consoles) could be reduced, as a smaller cache or less processing capacity may be acceptable when the provided resources are better utilized. Overall, the benefit would be cost reduction, whether those costs are purely monetary or related to chip area or energy.

#### 1.3.3 High-Performance Computing

High-performance computing applications typically involve splitting large tasks into manageable pieces that can be handled by individual processors. As one might expect, such tasks are compute- and memory-intensive. When running a single high-performance computing application on multiple processors, it is often beneficial if all processors have made approximately the same amount of progress at any point in time, due to the need to periodically synchronize processors. If every high-performance computing application were represented as one or more real-time tasks, then a real-time scheduler that attempts to make constructive co-scheduling choices could assist with the synchronization requirements of the application. This might allow such an application to finish earlier, or could allow multiple such applications to be supported, since an application may no longer require exclusive access to the processors that it is assigned.

#### 1.4 Thesis Statement

The major limitation of prior approaches for multiprocessor real-time scheduling is that they are they are cache-agnostic; this can result in ineffective use of shared caches, either due to cache thrashing, missed opportunities for cache reuse, or an unnecessary loss of cache affinity (e.g., due to preemptions). The result is that task execution-time requirements may need to be higher than if the cache were effectively used. We attempt to address this limitation in this dissertation. The thesis statement to be supported is the following.

Multiprocessor real-time scheduling algorithms can more efficiently utilize multicore platforms when scheduling techniques are used that reduce shared cache miss rates. Such techniques can result in decreased execution times for real-time tasks, thereby allowing a larger real-time workload to be supported using the same hardware, or enabling costs (related to hardware, energy, or chip area) to be reduced.

#### 1.5 Contributions

In this section, we present an overview of the contributions of this dissertation.

#### 1.5.1 Cache-Aware Real-Time Scheduling Methods

The first major contribution of this dissertation is the creation of cache-aware scheduling heuristics that influence co-scheduling choices so that cache miss rates are reduced. As part of this contribution, we introduce the multithreaded task (MTT) abstraction. MTTs were first introduced in prior work leading to this dissertation [3] as a first step towards representing concurrency within task models that typically handle only the sequential execution of tasks (e.g., the periodic and sporadic task models that are introduced in Chapter 2 and used throughout this dissertation). In MTTs, multiple (sequential) real-time tasks work together to perform the same operation. MTTs arise naturally in many settings. For example, multiple tasks might perform different functions on the same video frame, or the same function on overlapping portions of the same frame, with a common period implied by the desired frame rate (Section 1.3 provided additional examples). The benefits of co-scheduling tasks within the same MTT are taken into account in the design of our cache-aware scheduler.

It is projected that as per-chip core counts increase, the processing power of individual cores is likely to remain the same (or even decrease if cores become simpler) [53]. As a result, exploiting parallelism will be essential to achieving performance gains. This fact suggests the need to investigate abstractions for parallel execution in real-time systems (and most other sub-disciplines of computer science), and it is for this reason that MTTs are an important contribution of this dissertation.

In our cache-aware scheduler, co-scheduling is *encouraged* for tasks within the same MTT, and *discouraged* for tasks (within different MTTs) when it would cause shared cache thrashing. Note that devising methods to support co-scheduling while ensuring real-time constraints is quite difficult; as stated earlier, the problem of influencing co-scheduling in these ways *while*

ensuring real-time constraints is NP-hard in the strong sense. As this dissertation progresses, we will find that designing even a sub-optimal approach that imposes few constraints on the types of task sets that can be supported is difficult. Further, an additional constraint on any scheduling heuristic that we choose to implement within a real operating system is the scheduling overheads associated with the heuristic—this issue is also addressed herein.

#### 1.5.2 Online Cache Profiling of Real-Time Workloads

The second major contribution of this dissertation is an automatic cache profiler that determines the cache behavior of real-time tasks during execution, and supplies this information to the employed scheduling heuristic. The metric of interest to us is *MTT per-job working set size* (WSS), which for the purposes of this dissertation is the size of the per-job cache footprint of an MTT. The size of this footprint is estimated online using hardware performance counters. By profiling the cache behavior of tasks during their execution, the need to profile tasks offline before execution is eliminated. This would make profiling less of an inconvenience or impossibility for certain types of workloads.

In prior work, Knauerhase et al. [43] investigated the use of performance counters to reduce cache miss rates and improve system performance for throughput-oriented tasks. Additionally, in the real-time domain, Pellizzoni et al. [54] used performance counters to record per-task cache misses during execution; however, the results were used for WCET analysis rather than to evaluate the cache behavior of tasks for the purposes of online scheduling, as is the case in this dissertation.

#### 1.5.3 Implementation and Evaluation

As a "proof of concept" that our scheduler and profiler are viable in practice, we implemented our cache-aware scheduler within Linux. This scheduler includes both a scheduling heuristic (as described in Section 1.5.1) and our cache profiler (as described in Section 1.5.2). This implementation is empirically evaluated on several multicore platforms under both synthetic and multimedia workloads. Demonstrating the practicality of such a scheduler within a general-purpose operating system is crucial, as many users would prefer to run certain real-

time applications (e.g., video players) in Windows or Linux (environments that may be more familiar and comfortable) instead of a specialized real-time operating system. We show that our scheduler often achieves a substantial reduction in shared cache miss rates over other multiprocessor real-time scheduling approaches, and since overheads are low, this translates into better overall system performance.

Our experimental evaluation, presented in Chapter 6, was conducted under both Linux and a hardware (processor and memory) architecture simulator. The use of an architecture simulator allowed us to get detailed results on the performance of our scheduling heuristics in a controlled environment, and to experiment with systems that are not commonly available today, to assess if our heuristics are likely to continue to have a performance impact as multicore architectures evolve. An initial evaluation of heuristics within the simulator, combined with some practical aspects of implementing these heuristics, guided our selection of which scheduling heuristic to use within Linux.

The presented evaluation suggests that eliminating thrashing and reducing miss rates in shared caches should be first-class concerns when designing real-time scheduling algorithms for multicore platforms with shared caches. As interest in providing real-time support within general-purpose operating systems (e.g., Linux) increases, and multicore platforms become increasingly ubiquitous within many of the hardware domains on which such operating systems run, a state-of-the-art real-time scheduler will have to address the needs of multicore platforms to remain relevant.

## 1.6 Organization

The rest of this dissertation is organized as follows. In Chapter 2, we review relevant prior work on real-time systems and cache-aware scheduling. In Chapter 3, we formally state the problem that this dissertation seeks to address, prove its intractability, and discuss early attempts at a solution. In Chapters 4 and 5, we describe the design and implementation of our cache-aware scheduling heuristics and cache profiler, respectively. In Chapter 6, we present an experimental evaluation of our scheduler under both an architecture simulator and Linux. Finally, we conclude in Chapter 7.

#### CHAPTER 2

## PRIOR WORK

In this chapter, we review prior work that is related to this dissertation. We begin with an overview of real-time scheduling, including multiprocessor scheduling. This is followed by research on the scheduling and cache profiling of non-real-time tasks in the presence of shared caches, which are common on multicore platforms. We then address other relevant real-time systems research, including work on real-time operating systems and real-time scheduling in the presence of hardware multithreading.

## 2.1 Real-Time Scheduling Overview

In this section, we present work related to real-time scheduling. We begin with an overview of concepts in real-time systems, and then discuss the additional challenges presented by multiprocessor scheduling.

#### 2.1.1 Recurrent Task Model

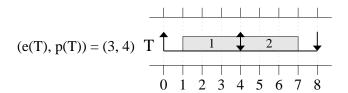

As indicated in Chapter 1, most real-time workloads require computation time at recurring intervals. Within the real-time research community, one of the simplest and most common ways of specifying recurrent workloads is the *periodic task model*, which was introduced by Liu and Layland [46]. In this model, the scheduling of a system of tasks  $\tau$  is considered. Each task  $T \in \tau$  is specified by a worst-case per-job execution cost e(T) and period p(T). The utilization of a task T is its execution cost divided by its period, or u(T) = e(T)/p(T). Tasks release jobs  $T_1, T_2, \ldots$ , at the start of each period beginning at time zero—the release time of job  $T_i$  is denoted as  $r(T_i)$ . Such a released job  $T_i$  is considered to be eligible at time t if all jobs  $T_1$  through  $T_{i-1}$  have completed by time t, and  $T_i$  has not completed execution at time

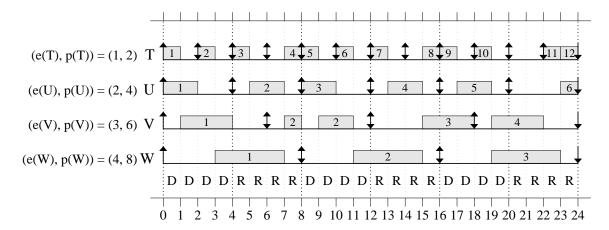

Figure 2.1: Conventions used in example schedules throughout this dissertation.

Figure 2.2: An example schedule for a periodic task system.

t. The absolute deadline  $d(T_i)$  of a job  $T_i$  is  $r(T_i) + D(T)$ , where D(T) is the relative deadline of T. If job  $T_i$  completes its execution after time  $d(T_i)$ , then it is tardy. Throughout this dissertation, we assume that deadlines are implicit, that is, D(T) = p(T). Assuming implicit deadlines, the absolute deadline of a job  $T_i$  coincides with the release time of job  $T_{i+1}$ , or  $d(T_i) = r(T_{i+1})$ . As such, we do not explicitly specify relative deadlines for any task system considered in this dissertation, and we refer to the absolute deadline of a job as simply its deadline.

In this dissertation, schedules are shown for a wide variety of scheduling policies and task sets. Figure 2.1 describes several conventions that are used for these schedules unless otherwise noted. Unless otherwise noted, all schedules in this dissertation assume zero scheduling-related overheads. We also assume that all task sets are *synchronous*, meaning that all tasks in a task set release their first job at the same time.

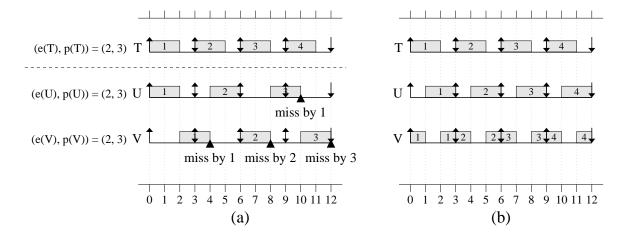

**Example (Figure 2.2).** Consider the example in Figure 2.2, which consists of two periodic real-time tasks (with implicit deadlines) scheduled on a single processor. The release time and deadline of each job  $T_i$  is  $(i-1) \cdot p(T)$  and  $i \cdot p(T)$ , respectively. Note that job releases and deadlines are typically combined, since the release time of job  $T_{i+1}$  coincides with the deadline

of job  $T_i$ . In this example, task T is statically prioritized over task U. The schedule shown is for a single *hyperperiod* of the task set, whose length is the least common multiple of all task periods. For a given task set, the schedule associated with that task set will repeat across each hyperperiod, as long as all deadlines are met (or the last job of every task released during the hyperperiod meets its deadline). All jobs meet their deadlines in this example except for  $U_1$ , which misses its deadline by one time unit.

A natural extension of the periodic task model, proposed by Mok [49], is the *sporadic* task model. In this model, p(T) specifies the *minimum* separation between job releases of T, rather than the *exact* separation as is the case in the periodic task model. This means that  $d(T_i)$  may not be equal to  $r(T_{i+1})$ , but it must be the case that  $d(T_i) \leq r(T_{i+1})$ . For example, in Figure 2.2, under the sporadic task model,  $T_2$  could be released at time 5 instead of time 4, but could *not* be released at time 3. Once a job is released, its period still exactly determines its deadline if implicit deadlines are assumed, just as in the periodic task model; that is, for any  $T_i$ ,  $d(T_i) = r(T_i) + p(T)$ . Although we present the sporadic task model here for the sake of completeness, throughout the remainder of this chapter and dissertation, the periodic task model is assumed unless stated otherwise.

#### 2.1.2 Hard vs. Soft Real-Time Systems

Broadly, real-time systems can be divided into two categories: hard and soft. In hard real-time systems, missing a deadline is catastrophic; in such systems, all deadlines must be met. Examples of hard real-time systems exist in safety-critical domains including transportation, aviation, and defense. In soft real-time systems, deadline misses can be tolerated in some cases. Further, in hard real-time systems, worst-case execution costs must be carefully determined, whereas in soft real-time systems, such costs can be determined less precisely (e.g., by) executing a large number of jobs of a task and using the maximum observed execution time as the worst-case execution cost). Examples of soft real-time systems include multimedia applications for which buffering may be employed or an occasional missed frame is permissible, certain types of real-time transactions (e.g., those that react to changes in the stock market), and applications for which guaranteeing a <math>share of the system over time is of greater

importance than meeting explicit deadlines.

While the primary objective of a real-time scheduling algorithm is to ensure timing constraints, recent results by Leontyev and Anderson [44] and Devi and Anderson [30] imply that soft real-time constraints provide sufficient flexibility to consider secondary objectives. In this dissertation, reducing miss rates in *shared caches* that are present in multicore platforms is the secondary objective. As explained in Chapter 1, such caches are a key bottleneck that must be addressed within scheduling approaches to achieve good overall system performance.

Several different notions of soft real-time guarantees exist. We now provide an overview of three different types of soft real-time guarantees.

Percentage of deadlines met. This type of soft real-time guarantee concerns the percentage of deadlines met by each task in a given sampling window, and is a function of the miss ratio, which is the number of deadline misses divided by the number of jobs in that same sampling window. This type of guarantee was considered by Lu et al. [47] and by Jain et al. [40]. In [47], feedback control mechanisms are employed to achieve a desired miss ratio for each task or an entire task system, whereas in [40], scheduling in the presence of hardware multithreading is considered, where a task set is considered "schedulable" if at most 5% of the deadlines of any task are missed.

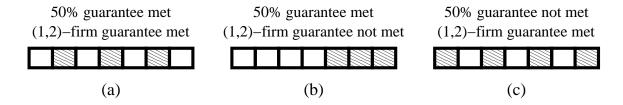

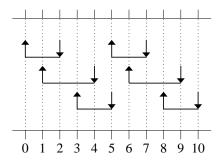

(m,k)-firm guarantees. Alternatively, rather than being concerned with a percentage, we can make a guarantee related to the number of jobs m that must meet their deadlines within any window of k consecutive jobs. This type of guarantee was first introduced by Hamadoui and Ramanathan [36] as an (m,k)-firm guarantee. Such a guarantee tends to be stronger than a simple percentage-based guarantee, since the guarantee must hold for any window of k jobs rather than just the sampling window, but exceptions do exist. The differences between these two types of guarantees are better shown in Figure 2.3. In insets (a) and (b), the percentage-based guarantee of 50% is met; however, a (1,2)-firm guarantee is not met in inset (b). In fact, even a seemingly weaker (1,3)-firm guarantee is not met. Interestingly, inset (c) presents a case where the (1,2)-firm guarantee is met without meeting the 50% guarantee; however, this is due to the size and position of the sampling window. If the (1,2)-firm guarantee continued

Figure 2.3: Comparison of percentage-based and (m, k)-firm soft real-time guarantees for seven consecutive jobs of the same task, where each job is indicated by a box. A hatched box indicates a deadline miss for the corresponding job.

to be met, then increasing the size of the sampling window by one job, or shifting it left or right by one job, would result in the 50% guarantee being met as well.

Bounded tardiness. The final notion of soft real-time computing considered in this dissertation is bounded tardiness. With this notion, soft real-time guarantees are met if the amount by which deadlines are missed, known as tardiness, is bounded. For some scheduling algorithms, tardiness may be bounded by some amount B, meaning that for a task T, any job  $T_i$  must complete execution no later than time  $d(T_i) + B$ , where B is a tardiness bound. As an example, in the schedule shown in Figure 2.2, hard real-time constraints cannot be met, since deadlines are missed. Since tardiness is at most one time unit, and therefore bounded, we can meet soft real-time constraints if this bound is suitable. Often, this bound is different for different tasks; if a bound on the entire system is desired, then a maximum value over all tasks can be computed. The first major research effort to determine such bounds for a real-time scheduling algorithm was by Srinivasan and Anderson [62]. This effort was later improved upon by Devi and Anderson [29], whose work paved the way for additional studies that provide tardiness bounds for broad classes of scheduling approaches [30, 44]. Further discussion of this work is best preceded by an overview of multiprocessor and global scheduling, which are provided in Sections 2.1.4 and 2.1.5.

**Comparison.** In this dissertation, bounded tardiness is the notion of soft real-time computing that we consider, since it has a number of advantages over the other notions of soft real-time guarantees. First, the work on bounded tardiness cited earlier allows us to conclude that a wide variety of scheduling approaches *automatically* provide bounded tardiness.

As a result, significant scheduling flexibility exists to influence co-scheduling decisions in an attempt to reduce cache miss rates. Second, bounded tardiness may be more compatible than other notions of soft real-time constraints for applications that can employ buffering, for example, multimedia applications. (An explanation of exactly how buffering can be employed to "hide" tardiness in such applications will be provided in Chapter 4.) Finally, when seeking to guarantee a share of the system to a task over time, rather than meet every deadline, a bound on tardiness is more natural than percentage-based or (m, k)-firm guarantees—as long as tardiness is bounded so that the desired share is maintained over time, the proportion of deadlines missed is unimportant. For these reasons, in the chapters that follow, bounded tardiness is the only notion of soft real-time guarantee that we consider. Henceforth, when discussing soft real-time constraints or guarantees, we mean bounded tardiness unless otherwise noted.

It is worth nothing that, since we implement our cache-aware scheduler within Linux, a number of sources of non-determinism exist (related to running a real operating system on real hardware) that are beyond our control. In such an environment, we interpret "soft real-time" to mean that deadline tardiness on average remains bounded, even if some tasks occasionally misbehave due to effects beyond our control. There are now many advocates of using Linux to support this notion of soft real-time execution. We will revisit this issue when presenting scheduling overheads in Chapter 6.

#### 2.1.3 Uniprocessor Scheduling

In the schedule in Figure 2.2, a uniprocessor is assumed. This schedule is an example of static-priority scheduling, in which tasks are statically assigned priorities and scheduled in priority order. Often, such policies are simple to implement, but result in system under-utilization, especially when hard real-time guarantees are desired. In particular, a task set may be feasible, but is not schedulable. A task set is feasible when a schedule exists that would allow all timing constraints to be met. For hard real-time systems, this means meeting all deadlines, while for soft real-time systems, this (in our case) means ensuring bounded tardiness. A feasible task set is schedulable under a particular scheduling algorithm when it

Figure 2.4: An EDF schedule for the task set in Figure 2.2.

is possible to meet the same timing constraints when that algorithm is used. For example, the task set in Figure 2.2 is feasible for hard real-time systems, but not schedulable using static-priority scheduling.

Alternately, we could allow task priorities to change during scheduling, otherwise known as dynamic-priority scheduling. One such scheduling algorithm is earliest-deadline-first (EDF), where jobs are scheduled in increasing order of their deadlines. Under EDF, all jobs will meet their deadlines as long as the system is not over-utilized—that is, the total utilization of all tasks is at most one [46]. In other words, any task set that is feasible for hard real-time systems on a uniprocessor is schedulable under EDF, since all deadlines will be met. This implies that, for uniprocessors, EDF is an optimal scheduling algorithm.

**Example (Figure 2.4).** Figure 2.4 depicts an EDF schedule for the same task set shown in Figure 2.2. Note that, in this example, all deadlines are met; in particular,  $U_1$  has higher priority than  $T_2$  at time 4, which allows its deadline to be met. Since the total utilization of all tasks is at most one, such a result is guaranteed.

#### 2.1.4 Multiprocessor Scheduling

Multiprocessor scheduling algorithms employ either a partitioned or global scheduling approach (or hybrids of the two). Under partitioned scheduling, tasks are statically assigned to processors, and tasks are scheduled on each processor using uniprocessor scheduling policies. An example of such an approach is partitioned EDF (PEDF), wherein the partitioned tasks are scheduled on each processor using EDF.

The advantages of a partitioned approach are practical in nature. First, most uniprocessor scheduling policies can be easily converted into multiprocessor scheduling policies by

Figure 2.5: An example of how bin-packing affects schedulability under partitioning.

employing partitioning, which makes multiprocessor scheduling (superficially) no harder than uniprocessor scheduling. Second, scheduling overheads associated with such approaches are generally low: scheduling decisions only concern a single processor and a fraction of the tasks in the task set, contention for shared data structures such as run queues is minimal or non-existent, and migrations (which can result in a loss of cache affinity and an increase in cache coherency traffic) cannot occur. (The impact of these overheads will be discussed in greater detail later in Section 2.1.9.)

Partitioning does have some disadvantages, however. First, and most importantly, the management of a globally-shared resource such as a shared cache can become quite difficult under partitioning—this is precisely because each processor is scheduled independently, which was previously argued to be an advantage. Second, partitioning requires solving a bin-packing problem: on an M-processor system, each task with a size equal to its utilization must be placed into one of M bins of size one. The bin in which a task is placed indicates the processor to which it is assigned. There are many feasible task systems for which a bin packing does not exist.

**Example (Figure 2.5).** A simple example is shown in Figure 2.5, and concerns partitioning three tasks onto a two-core platform. For this and future examples, a dotted line as shown in inset (a) indicates how the tasks are partitioned onto cores. Since each task has a utilization of 2/3, each core can accommodate only one task without being overloaded. As a result, a bin

packing does not exist, resulting in one overloaded core and unbounded tardiness, as can be seen in the schedule in inset (a), where PEDF is employed. Therefore, no real-time guarantees can be made; yet, the task set is feasible if one task is allowed to migrate between the two cores, executing half of the time on each, as seen in inset (b).  $\Box$

In the worst case, bin packing is impossible for certain task sets that require only slightly more than 50% of the available processing resources—that is, their total utilization is slightly greater than M/2. Thus, partitioning approaches can result in inferior schedulability, especially when overheads are negligible and soft real-time schedulability is the primary concern. For these reasons, we give global scheduling approaches more consideration. These approaches are described next.

#### 2.1.5 Global Scheduling

In global scheduling algorithms, all processors select jobs to schedule from a single run queue. As a result, jobs may migrate among processors, and contention for shared data structures is likely. Our cache-aware scheduler, in which co-scheduling decisions are influenced to reduce shared cache miss rates, is an example of a global scheduling algorithm.

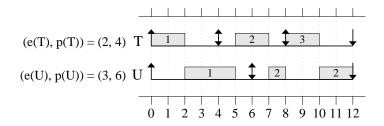

In this dissertation, we are primarily concerned with two global scheduling policies in addition to our own: preemptive global EDF (GEDF) and non-preemptive global EDF (NP-GEDF). Under both GEDF and NP-GEDF, jobs are scheduled in order of increasing deadlines, with ties broken arbitrarily (e.g., by task identifier). The difference between GEDF and NP-GEDF is that newly-released jobs can preempt scheduled jobs under GEDF, while under NP-GEDF, a scheduled job runs to completion without preemption.

**Example (Figure 2.6).** Consider Figure 2.6, which depicts two-core GEDF and NP-GEDF schedules for the same task set. At time 3, job  $V_1$  is preempted in inset (a), while it continues to execute without being preempted in inset (b). As a result, the schedules deviate significantly from that time onwards.  $V_2$  and  $V_3$  are also preempted in inset (a), resulting in similar differences in the two schedules.

Prior work has shown that a hybrid scheduling approach known as *clustered* EDF (CEDF), first proposed in [19], typically results in better schedulability for soft real-time systems than

Figure 2.6: Two-core schedules under (a) GEDF and (b) NP-GEDF for the same task set.

other approaches [15, 22]. Under CEDF, tasks are statically assigned to clusters of cores (preferably clusters that share a cache), and tasks are scheduled on each cluster using GEDF. For platforms with multiple lowest-level shared caches (e.g., a machine with two quad-core chips, where each chip contains a single shared lowest-level cache), these caches could be managed independently using a similar approach, where our cache-aware scheduler (described in Chapters 4 and 5) is used within each cluster instead of GEDF. It is for these reasons that in Chapter 6, GEDF is used as a baseline for evaluating the performance of our cache-aware scheduler. We also introduce NP-GEDF in this dissertation as an example of a non-preemptive policy, since our cache-aware scheduler attempts to emulate such a policy when feasible by encouraging (but not forcing) the non-preemptive execution of jobs.

Note that, in Figure 2.6, deadlines are missed under both approaches. Neither GEDF nor NP-GEDF is optimal; that is, for each algorithm, feasible task sets exist that will result in missed deadlines when scheduled using that algorithm. However, deadline tardiness under both GEDF and NP-GEDF is bounded [30] for all feasible task sets. Thus, we could consider

such algorithms to be optimal when *soft* real-time constraints are desired. The tardiness bounds associated with GEDF and NP-GEDF are introduced next.

### 2.1.6 Tardiness Bounds Under Global Scheduling

We now provide a more detailed discussion of work related to bounded tardiness under global scheduling algorithms. Srinivasan and Anderson [62] undertook the first major effort to determine tardiness bounds for a global multiprocessor real-time scheduling algorithm—in this case, the earliest-pseudo-deadline-first algorithm, a type of Pfair algorithm (Pfair scheduling is introduced in Section 2.1.7). Devi and Anderson [29] extended the work of [62] by disproving the tardiness bound of one that was claimed in that work. Devi and Anderson followed this work with tardiness bounds for GEDF and NP-GEDF [30], and Leontyev and Anderson extended that work by providing a generalized tardiness-bound result for global multiprocessor scheduling algorithms [44]; these bounds are stated next.

The tardiness for a task  $T \in \tau$  scheduled using GEDF is x + e(T), where x is defined as follows (with minor changes from [30] to maintain consistency with our notation specified earlier).

$$x = \frac{\mathcal{E}_x - \min_{U \in \tau}(e(U))}{M - \mathcal{U}_x}$$

(2.1)

In (2.1),  $\mathcal{E}_x$  is the sum of the  $\Lambda$  highest execution costs over all tasks in  $\tau$ , and  $\mathcal{U}_x$  is the sum of the  $\Lambda - 1$  highest utilizations over all tasks in  $\tau$ , where  $\Lambda$  is defined as follows.

$$\Lambda = \left[ \sum_{U \in \tau} u(U) \right] - 1 \tag{2.2}$$

The tardiness for a task  $T \in \tau$  scheduled using NP-GEDF is y + e(T), where y is similar to x and defined as follows.

$$y = \frac{\mathcal{E}_y + \mathcal{B}_y - \min_{U \in \tau}(e(U))}{M - \mathcal{U}_y}$$

(2.3)

In (2.3),  $\mathcal{E}_y$  is the sum of the  $\Lambda + 1$  highest execution costs over all tasks in  $\tau$ ,  $\mathcal{B}_y$  is the sum of the  $M - \Lambda - 1$  highest execution costs over all tasks in  $\tau$  (a term required to fully

account for non-preemptive execution), and  $\mathcal{U}_y$  is the sum of the  $\Lambda$  highest utilizations over all tasks in  $\tau$ , where  $\Lambda$  is again defined as in (2.2).

Observe that deadlines are missed by at most one time unit in both schedules shown in Figure 2.6. Using the above formulas to calculate the tardiness bounds under each approach, we would get  $\Lambda = \lceil 2/3 + 2/3 + 4/7 \rceil - 1 = 1$ ,  $\mathcal{E}_x = 4$ ,  $\mathcal{U}_x = 0$ ,  $\mathcal{E}_y = 4 + 2 = 6$ ,  $\mathcal{B}_y = 0$ ,  $\mathcal{U}_y = 2/3$ , x = (4-2)/2 = 1, and y = (6-2)/(2-2/3) = 3. The largest execution cost for any task in Figure 2.6 is 4; thus, the resulting tardiness bounds are 5 under GEDF and 7 under NP-GEDF. Typically, it is the case that observed tardiness bounds are considerably lower than any analytical bound; however, analytical bounds are necessary in order to make soft real-time guarantees.

As noted earlier, Leontyev and Anderson [44] extended the tardiness-bound proofs in [30] to apply to a wide variety of global scheduling algorithms. In this work, a priority point is assigned to each eligible job, with earlier priority points denoting a higher priority (job preemptions may occur). For example, under GEDF, the priority point of each job is its deadline. If the priority point of every job is within a window bounded by its release time and deadline, then job priorities are window-constrained. It is shown in [44] that under any global scheduling algorithm with window-constrained priorities, deadline tardiness is bounded provided that the system is not over-utilized, even if the priority point of a job moves arbitrarily within its window. (Such a guarantee is not possible under partitioned scheduling.)

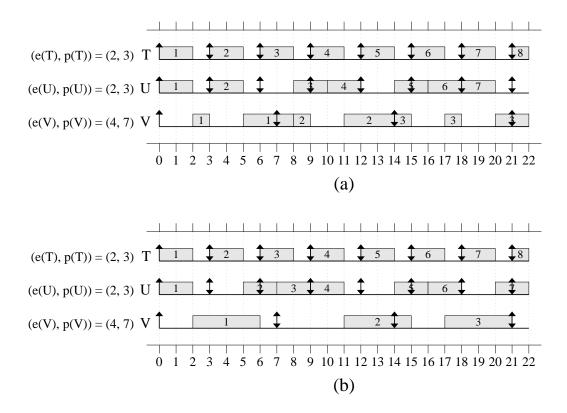

**Example (Figure 2.7).** To demonstrate the use of priority points, consider Figure 2.7, which depicts a two-core schedule for the task set shown assuming the EVEN-ODD policy, created specifically for this example. In the EVEN-ODD policy, the priority point of a job at any time t is its release time if  $\lfloor t/4 \rfloor$  is odd and its deadline if  $\lfloor t/4 \rfloor$  is even. As we can see in Figure 2.7, this policy results in deadline misses for jobs  $T_{11}$  and  $U_6$ . However, even though job priorities frequently change, such priorities are window-constrained, and the task set does not over-utilize the system; thus, tardiness is bounded.

As the reader might expect from the above example, many dynamic-priority multiprocessor real-time scheduling policies are window-constrained and therefore have bounded tardi-

Figure 2.7: A two-core schedule under policy EVEN-ODD, where the power of priority points is demonstrated by allowing tardiness to be bounded in spite of frequent job priority changes. A "D" (respectively, "R") indicates that jobs are prioritized by deadline (respectively, release time) during that time interval.

ness. This includes the cache-aware scheduling heuristics that are described in Chapter 4, where the priority point of a job is moved to the current time to influence co-scheduling decisions, also known as a job *promotion*.

The tardiness bound for a scheduling algorithm with window-constrained priorities is similar in nature to those specified for GEDF and NP-GEDF. The tardiness for a task  $T \in \tau$  scheduled using a window-constrained algorithm is z + e(T), where z is defined as follows (as before, with minor changes from [44] to maintain consistency with our notation).

$$z = \frac{\mathcal{E}_z + A(T)}{M - \mathcal{U}_z} \tag{2.4}$$

In (2.4),  $\mathcal{E}_z$  is the sum of the M-1 highest execution costs over all tasks in  $\tau$ , and  $\mathcal{U}_z$  is the sum of the M-1 highest utilizations over all tasks in  $\tau$ . A(T) is defined as follows.

$$A(T) = (M-1) \cdot \rho - e(T) + \sum_{U \in \tau \setminus T} \left( \left\lceil \frac{\psi(T) + \phi(U)}{p(U)} \right\rceil + 1 \right) \cdot e(U)$$

(2.5)

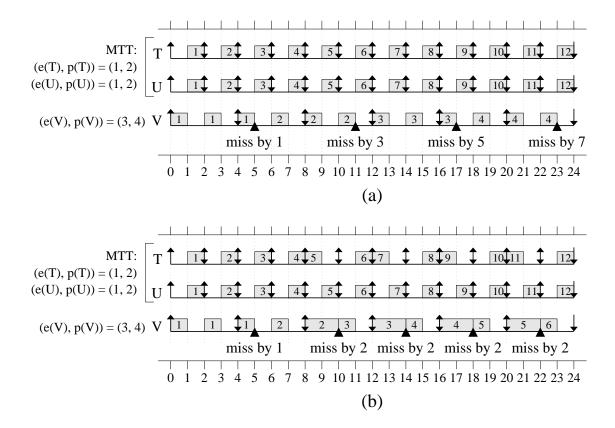

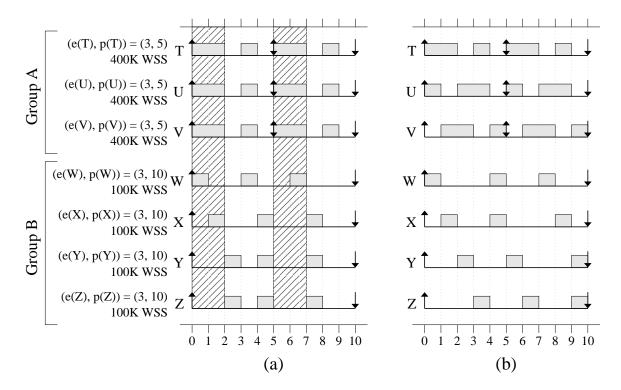

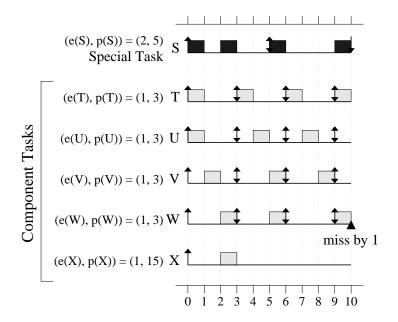

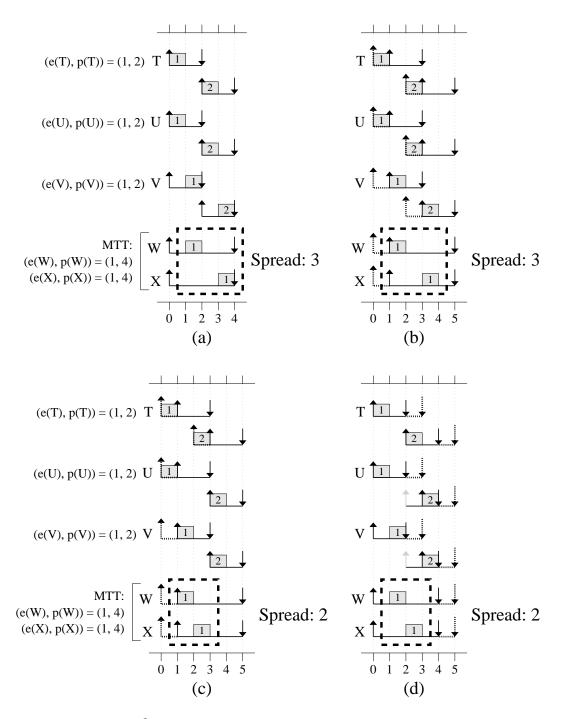

$\phi(T)$  (respectively,  $\psi(T)$ ) indicates the amount by which the priority point of a job of T can be before its release time (respectively, after its deadline), and  $\rho = \max_{T \in \tau} (\phi(T)) + \max_{T \in \tau} (\psi(T))$ .