### Analyzing the Behavior of Loop Nests in the Memory Hierarchy: Methods, Tools, and Applications

|      | by     |

|------|--------|

| Erin | Parker |

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

$\begin{array}{c} {\rm Chapel\ Hill} \\ 2004 \end{array}$

| Approved by:                   |  |  |  |

|--------------------------------|--|--|--|

|                                |  |  |  |

| Siddhartha Chatterjee, Advisor |  |  |  |

| Alvin Lebeck, Reader           |  |  |  |

|                                |  |  |  |

| Frank Mueller, Reader          |  |  |  |

| Jan Prins, Reader              |  |  |  |

| Jack Snoeyink, Reader          |  |  |  |

| David Plaisted                 |  |  |  |

#### ABSTRACT

ERIN PARKER: Analyzing the Behavior of Loop Nests in the Memory Hierarchy: Methods, Tools, and Applications.

(Under the direction of Siddhartha Chatterjee.)

Processor speeds are improving at a much faster rate than the speeds of accessing main memory. As a result, data access time dominates the execution times of many programs. Understanding the behavior of programs executing in a memory hierarchy is therefore an important part of improving program performance. This dissertation describes an analytical framework for understanding the behavior of loop-oriented programs executing in a memory hierarchy. The framework has three components: 1) an alternative classification of cache misses that makes it possible to obtain the exact cache behavior of a sequence of program fragments by combining the cache behavior of the individual fragments; 2) the use of Presburger arithmetic to model data access patterns and describe events such as cache misses; and 3) algorithms exploiting the connection among Presburger arithmetic, automata theory, and graph theory to produce exact cache miss counts.

The analytical framework presented in this dissertation goes beyond existing analytical frameworks for modeling cache behavior: it handles set-associative caches, data cache and translation lookaside buffer (TLB) misses, imperfect loop nests, and nonlinear array layouts in an exact manner. Experiments show both the framework's value in the exploration of new memory system designs and its usefulness in guiding code and data transformations for improved program performance.

## ACKNOWLEDGMENTS

I thank my thesis advisor Sid Chatterjee for his unwavering guidance and support. Without his encouragement, the work of this dissertation would not have been possible. In particular, his persistence and attention even after leaving Chapel Hill in 2001 are greatly appreciated.

I thank my committee members Alvy Lebeck, Frank Mueller, Dave Plaisted, Jan Prins, and Jack Snoeyink for their advice and for being so generous with their time.

I thank the entire UNC Department of Computer Science for making Sitterson Hall such an enjoyable place to work and learn. Especially, I thank the administrative and technical staff of the computer science department, whose assistance has been invaluable. I thank my UNC classmates and friends for making the last five years a lot of fun. Tom B, Shelby, Dave, Zac, Kimberly, and Josh, your friendship has made it all worthwhile.

I thank the Department of Energy's High-Performance Computer Science Fellowship program, which has sponsored me for the last four years.

Finally, I thank my family for their amazing support and understanding. I could not do without the limitless love and encouragement of my father Walt, mother Barbara, sister Adrienne, sister Amy, and husband Tom. These people deserve more than just their names on this page. I hope that in real life, I can do enough to thank them.

# TABLE OF CONTENTS

| L  | ST ( | OF TABLES                             | xi         |

|----|------|---------------------------------------|------------|

| LI | ST ( | OF FIGURES                            | xiii       |

| 1  | Intr | roduction                             | 1          |

|    | 1.1  | Motivation                            | 1          |

|    | 1.2  | Determining Cache Behavior            | 5          |

|    | 1.3  | Thesis Contributions                  | 8          |

|    | 1.4  | Limitations                           | 9          |

|    | 1.5  | Organization                          | 10         |

| 2  | Ter  | minology and Notation                 | 13         |

|    | 2.1  | Cache Basics                          | 13         |

|    |      | 2.1.1 Static Cache Structure          | 13         |

|    |      | 2.1.2 Dynamic Cache Behavior          | 18         |

|    |      | 2.1.3 A Special Cache—the TLB         | 19         |

|    | 2.2  | Modeling Loop Nests                   | 20         |

|    | 2.3  | Modeling Array References             | 22         |

|    | 2.4  | Presburger Arithmetic                 | 24         |

|    | 2.5  | Automata Theory                       | 26         |

|    | 2.6  | Summary                               | 27         |

| 3  | AN   | New Classification of Cache Misses    | <b>2</b> 9 |

|    | 3.1  | Composability                         | 29         |

|    | 3.2  | Interior-Boundary Miss Classification | 30         |

|    | 3.3  | Cache State                           | 32         |

|    | 3.4  | Summary                               | 35         |

| 4  | Ana  | alyzing Cache Behavior                | 37         |

|    | 4.1  | Program Execution Model               | 38         |

|    | 4.2  | Neighborhoods and Witnesses           | 39         |

|   | 4.3 | Expressing Witnesses in Presburger Arithmetic           | 41 |

|---|-----|---------------------------------------------------------|----|

|   |     | 4.3.1 Formulas Describing Program and Memory Structure  | 41 |

|   |     | 4.3.2 Formulas Describing Cache Behavior                | 43 |

|   | 4.4 | Deciding Cache Event Outcomes                           | 48 |

|   |     | 4.4.1 Interior Miss                                     | 48 |

|   |     | 4.4.2 Replacement Miss                                  | 49 |

|   |     | 4.4.3 Potential Boundary Miss                           | 49 |

|   |     | 4.4.4 Cache State                                       | 50 |

|   | 4.5 | Summary                                                 | 51 |

| 5 | Cou | inting Cache Misses 5                                   | 52 |

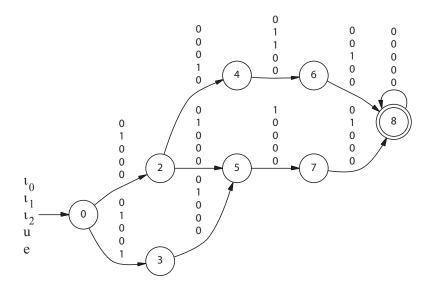

|   | 5.1 | Representing Formulas as DFAs                           | 54 |

|   |     | 5.1.1 Encoding Free Variable Values                     | 54 |

|   |     | 5.1.2 Example DFA                                       | 55 |

|   |     | 5.1.3 Procedure for Constructing DFAs                   | 57 |

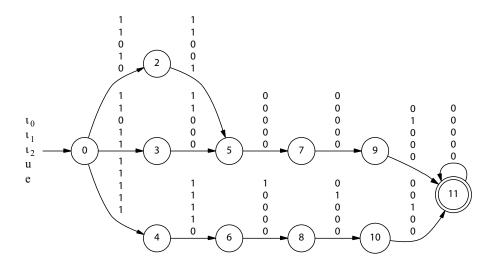

|   | 5.2 | Counting and Enumerating Accepting DFA Paths            | 58 |

|   |     | 5.2.1 Treating the DFA as a Graph                       | 58 |

|   |     | 5.2.2 DFA Path Length                                   | 59 |

|   |     | 5.2.3 Counting Accepting Paths                          | 61 |

|   |     | 5.2.4 Enumerating Accepting Paths                       | 63 |

|   | 5.3 | Counting Witnesses to Determine Cache Behavior          | 65 |

|   |     | 5.3.1 Counting Witnesses                                | 65 |

|   |     | 5.3.2 Counting Interior and Replacement Misses          | 67 |

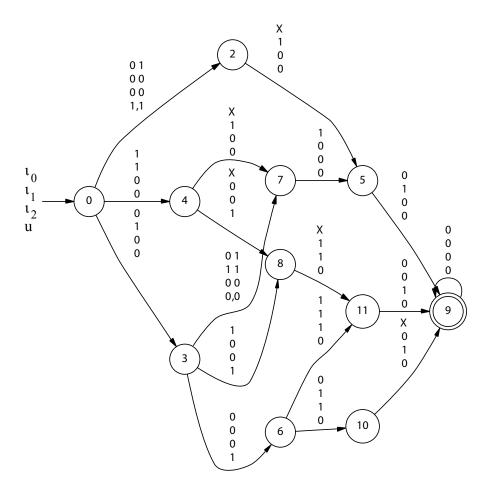

|   |     | 5.3.3 Counting Boundary Misses and Updating Cache State | 68 |

|   | 5.4 | Handling Misses Independent of Associativity            | 75 |

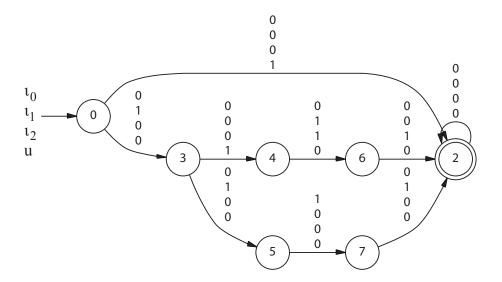

|   |     | 5.4.1 Interior Misses in Direct-Mapped Caches           | 75 |

|   |     | 5.4.2 Compulsory Misses                                 | 76 |

|   | 5.5 | Summary                                                 | 76 |

| 6 | Put | ting It All Together 7                                  | 77 |

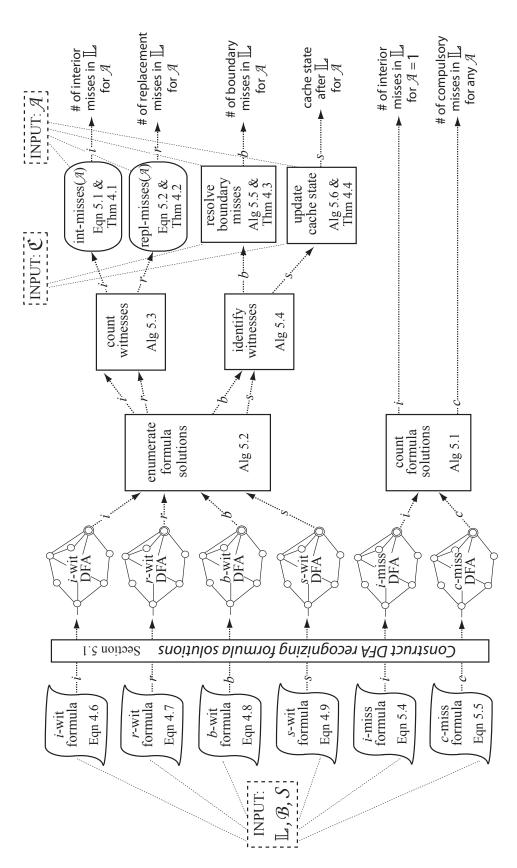

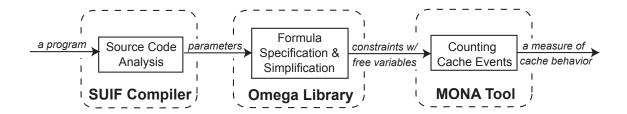

|   | 6.1 | The Analysis Framework                                  | 77 |

|   | 6.2 | Implementation                                          | 79 |

|   |     | 6.2.1 Source Code Analysis                              | 80 |

|   |     | 6.2.2 Formula Specification and Simplification          | 81 |

|   |     | 6.2.3 Counting Cache Events                             | 81 |

| 7 | Ext | ensions to Analysis Framework 8                         | 83 |

|   | 7.1 | Nonlinear Data Layouts                                  | 83 |

|   | 7.2 | FIFO Cache Replacement Algorithm                        | 86 |

|   | 7.3 | Summary                                                 | 87 |

| 8            | App  | olication and Validation                       | 88  |

|--------------|------|------------------------------------------------|-----|

|              | 8.1  | Single Loop Nests                              | 89  |

|              | 8.2  | Loop Nest Sequence                             | 103 |

|              | 8.3  | Nonlinear Data Layouts                         | 110 |

|              | 8.4  | Loop Transformation                            | 115 |

|              |      | 8.4.1 Loop Tiling                              | 115 |

|              |      | 8.4.2 Loop Permutation                         | 117 |

|              | 8.5  | Aggregate Array Computations                   | 118 |

|              |      | 8.5.1 Partial Summation                        | 120 |

|              |      | 8.5.2 Sequence Local Average                   | 122 |

|              | 8.6  | Summary                                        | 123 |

| 9            | Rela | ated Work                                      | 127 |

|              | 9.1  | Work Based on Reuse Vectors                    | 127 |

|              | 9.2  | Work Based on Stack Distances                  | 128 |

|              | 9.3  | Work Based on Linear Constraints               | 129 |

|              | 9.4  | Work Based on Reference Traces                 | 131 |

|              | 9.5  | Work Based on Cache State                      | 132 |

|              | 9.6  | Summary                                        | 132 |

| 10           | Con  | aclusions                                      | 135 |

|              | 10.1 | Thesis Contributions                           | 135 |

|              | 10.2 | Commentary                                     | 138 |

|              | 10.3 | Future Research Directions                     | 140 |

|              |      | 10.3.1 Improving Framework Robustness          | 140 |

|              |      | 10.3.2 Modeling More Cache Features and Events | 140 |

|              |      | 10.3.3 Applying the Analysis Framework         | 141 |

|              | 10.4 | Summary                                        | 142 |

| $\mathbf{A}$ | Exa  | mple Witness Formulas and DFAs                 | 143 |

| ΒI           | BLI  | OGRAPHY                                        | 155 |

# LIST OF TABLES

| Presburger formulas used to describe cache behavior                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{tri}$ in data caches                                                                                     |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{tri}$ in TLBs                                                                                            |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{tri}$ , varying $\mathcal{B}$ and $\mathcal{S}$                                                          |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{\text{vec}}$ in data caches                                                                              |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{\text{vec}}$ in TLBs                                                                                     |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{mm}$ in data caches                                                                                      |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{mm}$ in TLBs                                                                                             |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{mm}$ , varying array starting addresses                                                                  |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{mm-var}$ in data caches                                                                                  |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{mm\text{-}var}$ in TLBs                                                                                  |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{calc3}$ in data caches                                                                                   |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by loop nest $\mathbb{L}_{calc3}$ in TLBs                                                                                          |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by the loop nest sequence of calc3 in data caches, for                                                                             |

| m=n=19                                                                                                                                    |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by the loop nest sequence of calc3 in data caches, for                                                                             |

| $m=n=29.\ldots 108$                                                                                                                       |

| Results of using the analysis framework to count misses in-                                                                               |

| curred by the loop nest sequence of calc3 in data caches, for                                                                             |

| $m = 19 \text{ and } n = 99. \dots \dots$ |

|                                                                                                                                           |

| 8.16          | Results of using the analysis framework to count misses in-                                                                 |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------|--|

|               | curred by the loop nest sequence of calc3 in data caches, for                                                               |  |

| 0.15          | m = 99 and $n = 19$                                                                                                         |  |

| 8.17          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by the loop nest sequence of calc3 in TLBs, for $m =$                                                                |  |

|               | $n = 19.  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  |  |

| 8.18          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by the loop nest sequence of calc3 in data caches, for                                                               |  |

|               | several problem sizes                                                                                                       |  |

| 8.19          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{vec}}$ with nonlinear array layouts, for $m =$                                       |  |

|               | $n = 16. \dots \dots$ |  |

| 8.20          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{vec}}$ with nonlinear array layouts, for $m=$                                        |  |

|               | 16 and $n = 32$                                                                                                             |  |

| 8.21          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{vec}}$ with nonlinear array layouts, for $m=$                                        |  |

|               | 32 and $n = 16$                                                                                                             |  |

| 8.22          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{vec}}$ with nonlinear array layouts, for $m=$                                        |  |

|               | $n = 32. \dots \dots$ |  |

| 8.23          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{tiled}}$ , varying tile size $T$                                                     |  |

| 8.24          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by all six loop permutations of the matrix multiplication                                                            |  |

|               | loop nest                                                                                                                   |  |

| 8.25          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{ps-orig}}$ in data caches                                                            |  |

| 8.26          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{ps-opt}$ in data caches                                                                    |  |

| 8.27          | Results of using the analysis framework to count misses in-                                                                 |  |

|               | curred by loop nest $\mathbb{L}_{\text{sla-orig}}$ in data caches                                                           |  |

| 8.28          | Results of using the analysis framework to count misses in-                                                                 |  |

| - <b>-</b> -0 | curred by loop nest $\mathbb{L}_{\text{sla-opt}}$ in data caches                                                            |  |

|               | carroa by 100p nebu m <sub>sla-opt</sub> in data caches                                                                     |  |

| 9.1           | Comparison of frameworks that do static analysis of memory behavior 134                                                     |  |

# LIST OF FIGURES

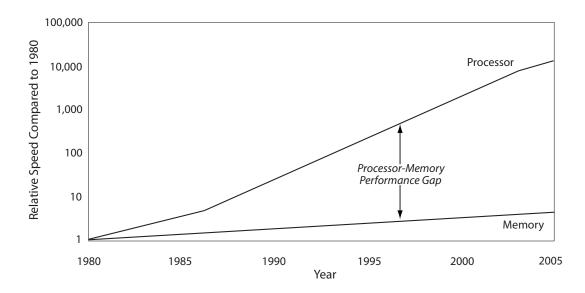

| 1.1 | The processor-memory performance gap                                                  | 2   |

|-----|---------------------------------------------------------------------------------------|-----|

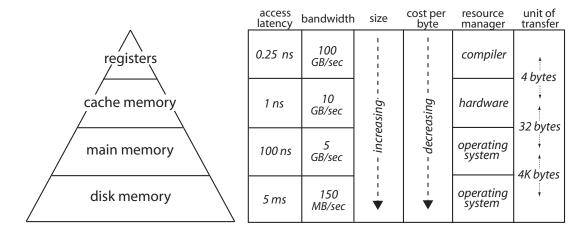

| 1.2 | The memory hierarchy pyramid                                                          | 3   |

| 1.3 | Examples of analyzable and unanalyzable loop nests                                    | 10  |

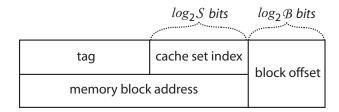

| 2.1 | The portions of a memory byte address                                                 | 14  |

| 2.2 | Representation of an $(A, B, C; S)$ cache                                             | 15  |

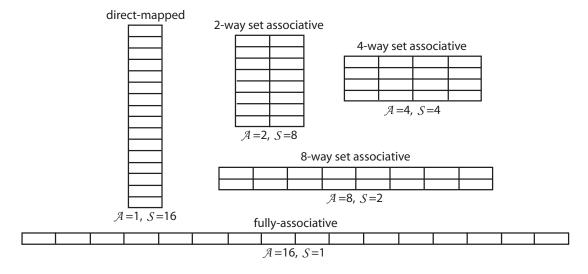

| 2.3 | The shapes of caches with differing associativity                                     | 15  |

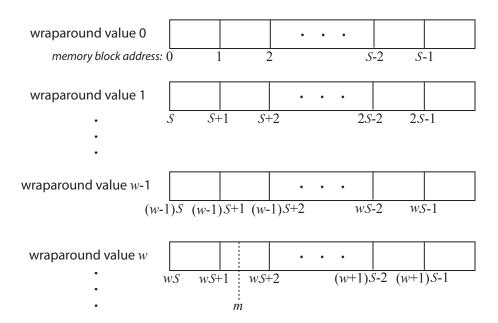

| 2.4 | The wraparound value of a memory byte address                                         | 16  |

| 2.5 | The running example loop nest $\mathbb{L}_{mm}$                                       | 17  |

| 2.6 | Wraparound values for the memory locations accessed by loop                           |     |

|     | nest $\mathbb{L}_{mm}$                                                                | 17  |

| 2.7 | An illustration of loop normalization to make step size one                           | 21  |

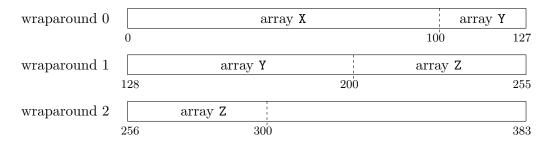

| 3.1 | 3-D views of the interior and potential boundary misses in-                           |     |

|     | curred by loop nest $\mathbb{L}_{mm}$                                                 | 31  |

| 3.2 | The role of cache state in the composition of program fragments                       | 33  |

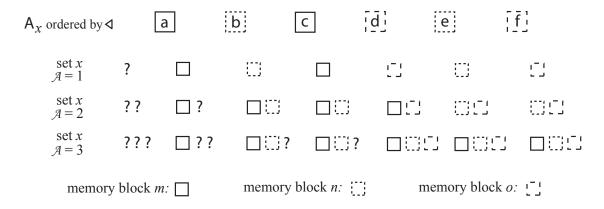

| 4.1 | Example sequence of accesses in $A_x$ and the contents of cache                       |     |

|     |                                                                                       | 41  |

| 4.2 | Presburger formula describing the <i>i</i> -witnesses of loop nest $\mathbb{L}_{mm}$  | 45  |

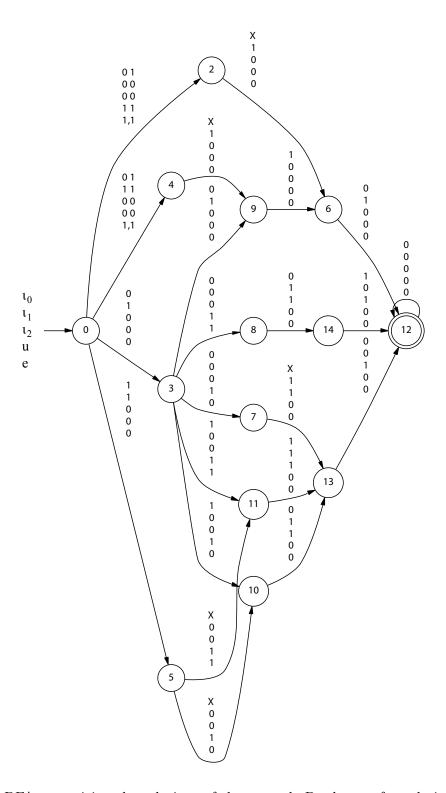

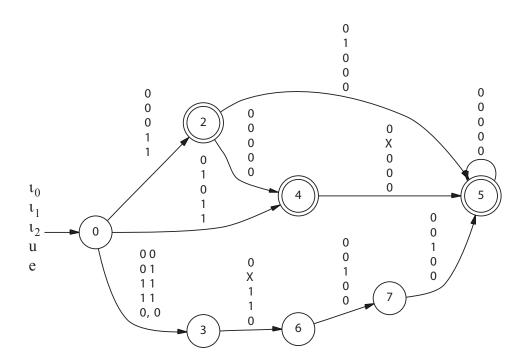

| 5.1 | DFA recognizing the solutions of an example $i$ -witness formula                      | 56  |

| 6.1 | High-level view of the method for modeling cache behavior pre-                        |     |

|     | sented in this dissertation.                                                          | 78  |

| 6.2 | Illustration of how tools fit into the analysis framework                             | 80  |

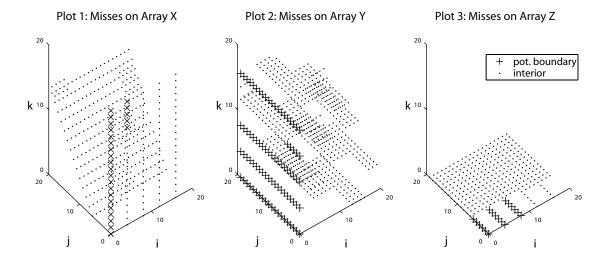

| 7.1 | Example arrangement of array data in memory using nonlinear                           |     |

|     | array layouts                                                                         | 84  |

| 8.1 | • • • • • • • • • • • • • • • • • • • •                                               | 99  |

| 8.2 | Loop nest $\mathbb{L}_{calc3}$ from the calc3 subroutine                              | 101 |

| 8.3 | The sequence of four loop nests from the calc3 subroutine                             | 104 |

| 8.4 | The six permutations of the matrix multiplication loop nest                           | 117 |

| 8.5 | Original partial summation loop nest $\mathbb{L}_{\text{ps-orig}}$ and optimized ver- |     |

|     | $\operatorname{sion} \mathbb{L}_{\operatorname{ps-opt}}$                              | 120 |

| 8.6  | Original sequence local average loop nest $\mathbb{L}_{	ext{sla-orig}}$ and optimized  |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | version $\mathbb{L}_{	ext{sla-opt}}$                                                   | 122 |

| A.1  | Presburger formula describing the $r$ -witnesses of loop nest $\mathbb{L}_{mm}$        | 144 |

| A.2  | Presburger formula describing the $b$ -witnesses of loop nest $\mathbb{L}_{\text{mm}}$ | 145 |

| A.3  | Presburger formula describing the s-witnesses of loop nest $\mathbb{L}_{mm}$           | 146 |

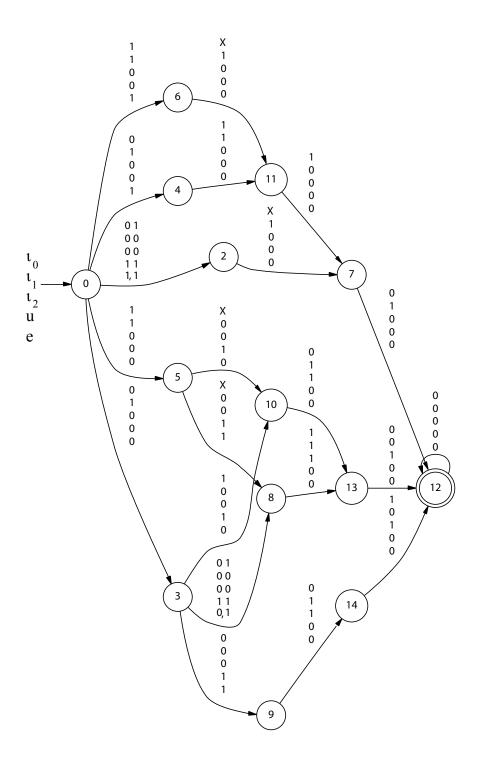

| A.4  | DFA recognizing the solutions of an example $r$ -witnesses formula                     | 147 |

| A.5  | DFA recognizing the solutions of an example $b$ -witnesses formula                     | 148 |

| A.6  | DFA recognizing the solutions of an example $s$ -witnesses formula                     | 148 |

| A.7  | Presburger formula describing interior misses of loop nest $\mathbb{L}_{mm}$           |     |

|      | in a direct-mapped cache                                                               | 149 |

| A.8  | DFA recognizing the solutions of an example Presburger for-                            |     |

|      | mula describing interior misses in a direct-mapped cache                               | 150 |

| A.9  | Presburger formula describing compulsory misses in loop nest $\mathbb{L}_{mm}$         | 151 |

| A.10 | DFA recognizing the solutions of an example compulsory miss formula                    | 151 |

| A.11 | Presburger formula describing the <i>i</i> -witnesses of loop nest $\mathbb{L}_{mm}$   |     |

|      | with a nonlinear array layout                                                          | 152 |

| A.12 | DFA recognizing the solutions of an example $i$ -witnesses for-                        |     |

|      | mula with a nonlinear array layout                                                     | 153 |

|      |                                                                                        |     |

## Chapter 1

## Introduction

As advances in processor speeds continue to outstrip those of main memory access, the processor-memory performance gap grows every year [66, 138]. The time required for accessing data from main memory is one to two orders of magnitude larger than the time required for operations on the data. Cache memory, one or more levels of fast memory placed between the processor and main memory, attempts to reduce the average data access time by capturing the most frequently referenced data close to the processor. In general, hardware alone does not solve the problem of poor memory performance, because not all programs use cache memory effectively. Therefore, even with the addition of caches, the execution time of many programs is dominated by the time spent accessing data from main memory.

By modifying a program's data access patterns or data layout (*i.e.*, the manner in which program variables map to memory locations), it is possible to use cache memory more effectively and improve the program's performance. Either a programmer can make code and data layout changes "by hand", or a compiler can do so automatically. In transforming a program, it is critical to know what changes will lead to improved performance, or better yet, what changes will lead to the best possible performance. The challenge of transforming a program to reduce its memory access time is understanding the behavior of the program executing in the presence of cache memory. This dissertation presents a static framework that produces the exact cache behavior of a program, given virtually any configuration of cache memory. The remainder of this chapter further motivates the work of analyzing cache behavior (Section 1.1), reviews a variety of methods for determining cache behavior (Section 1.2), lists the contributions of this thesis (Section 1.3), points out the limitations of analysis framework presented here (Section 1.4), and provides a roadmap for the rest of the document (Section 1.5).

#### 1.1 Motivation

Processor and main memory, or dynamic random access memory (DRAM), technologies are constantly improving, but at different rates. From 1980 to 1986, processor frequency improved

Figure 1.1: Processor speed and speed of accessing main memory plotted over time, with speed in 1980 as a baseline.

by about 35% per year, while from 1987 to 2002, processor frequency improved by about 55% per year [66]. Since 2003, the rate of improvement in processor frequency has slowed down to about 35% per year [53]. DRAM performance (*i.e.*, the latency of accessing data) has improved steadily at about 7% per year [66]. The diverging rates of improvement have formed the processor-memory performance gap. Figure 1.1 shows how processor and memory performance have improved over time relative to their performance in 1980, with the processor-memory performance gap clearly evident. For more and more programs, memory access time determines execution time, and this trend will continue unless the performance gap begins to close.

In an ideal system, memory would be infinitely large and any data required by a program would be immediately available to the processor. Given the physical constraints of a computer, such an ideal is not possible. As early as 1946, Burks, Goldstine, and von Neumann [28] suggested a hierarchy as a way of arranging memory:

We are therefore forced to recognize the possibility of constructing a hierarchy of memories, each of which has greater capacity than the preceding but which is less quickly accessible.

In 1962, Kilburn *et al.* [79] proposed automatic management of two levels of memory and demonstrated it in the Atlas computer. A few years later, Wilkes [130] wrote the first paper describing the concept of a cache. The first commercial computer with cache memory, the IBM 360/85 [87], followed shortly. Today almost all computer systems have cache memory, and most have multilevel caches [8, 71, 126].

Figure 1.2 shows the hierarchy of four kinds of memory typically found in systems today. A

Figure 1.2: The memory hierarchy pyramid and typical values of relevant parameters [66]. Smaller memories are faster to access and more expensive per byte. Data contained in upper level i is also contained in lower level i + 1.

relatively small register file located in the processor core is the most quickly-accessible memory. Disk memory is far from the processor and the slowest to access. Five parameters describe the levels of a uniprocessor memory hierarchy: speed (indicated by both access latency and bandwidth), size, cost per byte, manager of the memory level, and the unit of transferring data between levels. The table in Figure 1.2 gives typical parameter values for each memory level [66]. Moving up the hierarchy, speed and cost per byte increase, as size decreases. Also, an upper level of memory is usually a subset of lower levels (*i.e.*, data contained in upper level i is also contained in lower level i+1). Given the speed of the memory hierarchy's upper levels, it would be best to access all data from there, but the expense of fast memory forces the upper levels to be small in size. These levels, therefore, cannot hold all of the data. As a result, some of the data is discarded from the upper levels before the program has finished using it. A program is said to have good **locality of reference** if it can reuse data while it is still in the upper levels of memory, which requires that the use and reuse of data be close together in time. The property of programs to reuse data and instructions they have used recently is called **locality** [66], and locality of reference refers to locality in the context of data.

The job of cache memory is to hold frequently referenced data close to the processor. A cache miss occurs when a program requests data that is not found in cache memory. **Miss penalty** is the cost of a cache miss, *i.e.*, the time required to access missed data from the lower levels of memory. The following equations [66] illustrate the impact of cache misses and miss penalty on the execution time of a program.

execution time = (CPU clock cycles + memory stall cycles)

$$\times$$

clock cycle time (1.1)

memory stall cycles = number of cache misses

$$\times$$

miss penalty (1.2)

It is clear that more cache misses and/or larger miss penalties slow the overall execution time of a program by worsening its memory performance. A good measure of memory performance is **average memory access time**, the average time spent accessing memory per request, as given by the following equation [66].

average memory access time = hit time + (miss rate

$$\times$$

miss penalty) (1.3)

Hit time is the time to access memory from cache, and miss rate is the fraction of cache accesses resulting in a miss. Attempts in software to improve the memory performance of programs (e.g., via transformations in code and data layout) cannot change hit time or miss penalty, but can shorten the average memory access time by reducing the number of cache misses. In other words, improving a program's locality of reference allows execution of the program to better utilize caches.

Efficient programs have good **locality of reference**, both temporal, by accessing recently referenced data together, and spatial, by accessing data with memory addresses near recently referenced data [114]. Caches exploit locality of reference in a program by capturing blocks of memory containing recently referenced data close to the processor. A program must have well-crafted code and data organization in order to achieve good locality of reference, which is a burden on the programmer, since the relationship between writing a program and its resulting locality of reference is often not straightforward. Locality of reference is often elusive and brittle: as an application evolves, seemingly insignificant modifications to its code or to the machine platform can lead to dramatic changes in its locality of reference.

There are two ways of transforming a program to improve its locality of reference: altering the order in which the program accesses data, and altering the data layout. Loop transformations [135] change the ordering of operations in loop-oriented programs in a way that preserves the semantics of the original program while producing a data access sequence with better locality of reference. Loop interchange [133], loop skewing [135], and iteration-space tiling [76, 132, 134] are examples of loop transformations. Although the issues of transformation legality and code generation for transformed loops are well-defined, methods for predicting the performance benefit of transforming a particular loop are less understood. Existing methods for evaluating the potential benefit of loop transformations usually offer only approximate or heuristic findings [40, 84, 93, 101, 108, 109, 132].

Recently, researchers have given some attention to transforming the layout of program data [7, 32, 33, 35, 36, 57, 84, 108, 109, 119, 131]. Data transformations modify the layout of data in memory in order to improve the locality of reference for the program's data access sequence. Array copying [84, 119], array padding [7, 108, 109], and nonlinear array layouts [32, 33, 57, 131] are examples of well-known data transformations. Careful placement of data in C-language structures, either by reordering fields within a single structure or by packing the frequently-accessed fields of several structures in the same cache line [35, 36], is another

example of an effective data transformation. Many code and data transformations have parameters whose values determine the behavior of the transformed program, such as tile sizes (for iteration-space tiling) and pad sizes (for array padding). As in the case for loop transformations, predictions of performance improvement due to a data transformation are often approximations. Rarely are code and data layout transformations beneficial when applied blindly. At issue are which transformations to apply, in which order to apply them, and how to set transformation parameters.

In attempting to improve a program's locality of reference, the goal of code and data transformations is to increase the number of times that the program accesses data from cache memory rather than from main memory. When successful, the average memory access time of the program is reduced. Another approach to dealing with large memory access latency is to tolerate, or hide, it. Techniques such as nonblocking (or lock-up free) caches [83], software-controlled prefetching [94, 95, 96], hardware-controlled prefetching [101, 114], stream buffers [70], and speculative loads [110] overlap data access with operations on previously-accessed data, hiding the large latency of accessing memory. These techniques work by reducing the observed latency for a group of memory accesses, exploiting concurrency at the hardware level. All of these methods attempt to cover up the problem of a large average memory access time and do not attempt to reduce it. Prefetching, stream buffers, and speculative loads potentially access more data from memory that is needed by the program, creating more contention from memory resources and possibly worsening the memory performance bottleneck. When effective, techniques for reducing the average memory access time are preferable over those that tolerate it. Extensive research has looked at the use of program transformations for reducing average memory access time, as the next section discusses.

### 1.2 Determining Cache Behavior

Much research has been devoted to guiding the application of code and data transformations, and most of the work focuses on loop-oriented programs. Improving the memory performance of loops has a significant impact on scientific programs, which spend the majority of their execution time in loops. Scientific programs tend to operate on large amounts of data, of which the cache can hold only a small amount. If scientific programs are not written in a manner that leads to good locality of reference, most of the data is displaced from cache before it can be reused. As a result, scientific programs are often the target of code and data transformations.

Early techniques for guiding loop and data transformations [7, 58, 84, 108] target specific loops, cache memory configurations, and/or loop transformations. Lam *et al.* [84] present a model for approximating the number of cache misses for tiled matrix multiplication and give an algorithm for selecting tile size, a parameter for iteration-space tiling. Fricker *et al.* [58] develop a model for approximating the number of cache misses for tiled matrix-vector multiplication

executing in a specific cache memory. Bacon *et al.* [7] introduce an algorithm for selecting pad sizes, a parameter for array padding. Rivera and Tseng [108] put forth techniques for applying inter- and intra-array padding transformations. Although the work has resulted in useful insights on the effects of specific transformations, it may not be possible to generalize these insights to apply to all programs.

Program simulation [46, 85, 91] is a well-established method for gauging memory performance. Entire programs can be simulated and there are no limits on cache memory configurations or program transformations. Simulating the execution of a program allows the effects of back-end compiler phases, such as instruction scheduling and register allocation, to be reflected in the cache behavior of the program. MemSpy [91] simulates the execution of a program to provide cache miss rates and causes for particular code and data objects. Similarly, CProf [85] is a cache performance profiler that uses simulation to identify source code and data structures with poor cache behavior. The Dinero [46] simulator reports the behavior of one or more cache designs, given as input a list of the memory references that a program makes during execution. However, there is a potential disadvantage to simulating execution of a program: the simulation running time greatly exceeds that of the original program, in general. Dynamic instrumentation [43] and hardware counters [25, 51] also capture the memory referencing behavior of a program, and have the same advantages and potential disadvantage as simulation.

Static analysis [31, 34, 54, 62, 122] gathers information from the source code of a program and from the configuration of an underlying memory system to determine the exact or approximate cache behavior without actually running or simulating the program. In particular, for loops, static analysis, whose complexity relates to the static structure of the loops, has the potential to be faster than simulation, whose complexity relates to the iteration count of the loops and is proportional to the execution time of the loops. Static analysis may be especially useful in profiling the cache activity of programs with very long execution times for which it is undesirable to do explicit simulation. Just as knowledge of the low-level, machine-specific arrangement of memory accesses is an advantage for simulation, the lack of such knowledge is a disadvantage for static analysis. Static analysis must make simplifying assumptions about the scheduling of instructions, about what data resides in registers, and so on. Memory behavior information determined at compile time via static analysis of a program can be used in a compiler to select program transformations.

Despite the benefits of static cache behavior analysis, there currently exists no compiletime framework for understanding cache behavior that is flexible, exact, and fast. Chapter 9 discusses several existing frameworks for analyzing memory behavior. The following are six weaknesses common to some or all of these frameworks.

• Approximating cache behavior. Simplifications in modeling the behavior of a program executing in a cache lead to an approximation of the program's actual cache be-

havior. Using sampling to estimate the number of cache misses provides a good understanding of a program's cache behavior when there are many cache misses occurring uniformly throughout the program. When the cache misses are few and sparse throughout the program, only an exact model of cache behavior guarantees an accurate picture of a program's cache performance.

- Modeling only fully-associative caches. The mapping of data from main memory to cache depends on the organization of the cache. For data caches, the organization is typically set-associative, sometimes direct-mapped, and almost never fully-associative. Furthermore, frameworks that model only fully-associative caches usually require that memory blocks contain only one data element. A cache model with such parameters is not representative of the caches in today's systems.

- Modeling data caches only, ignoring misses in the translation lookaside buffer (TLB). A data cache stores most frequently referenced data close to the processor, while a TLB stores memory address translations. The misses in both the data cache and TLB determine a program's memory performance. Modeling a program's behavior in a data cache and TLB is more complete than modeling its behavior in a data cache alone.

- Considering only perfectly-nested loops. A loop nest is a loop containing one or more other loops, and the nesting may be perfect or imperfect. Considering only perfect loop nests restricts the programs whose cache behavior can be analyzed.

- Considering loop nests in isolation of each other. Modeling the cache behavior of loop nests out of the context of the rest of the program is inexact. Not taking into account the contents of the cache before a loop nest begins execution leads to an overestimation of the actual cache miss count for the loop nest.

- Handling only canonical array layout functions (*i.e.* row- and column-major). Row- and column-major are the standard ways of mapping arrays to memory. However, the ability to evaluate the potential benefit of nonstandard data layouts is useful.

This dissertation describes an analytical framework for understanding the behavior of loop nests executing in a memory hierarchy. The framework has three components:

- 1) an alternative classification of cache misses that makes it possible to obtain the exact cache behavior of a sequence of program fragments by combining the cache behavior of the individual fragments (see Chapter 3);

- 2) the use of Presburger arithmetic [102, 103, 117] to model data access patterns and describe events such as cache misses (see Chapter 4); and

3) algorithms exploiting the connection among Presburger arithmetic, automata theory, and graph theory to produce exact cache miss counts (see Chapter 5).

The cache analysis framework presented in this dissertation addresses the six weaknesses outlined above. Given a program consisting of a sequence of loop nests and the configuration of the underlying cache memory, the framework produces the number of cache misses incurred by the program, indicating the program's cache behavior. The framework produces the exact number of cache misses incurred by a sequence of loop nests. The framework models cache memories of any organization, including direct-mapped, set-associative, and fully-associative caches. The framework handles cache memories of virtually any configuration, allowing the counting of both data cache misses and TLB misses. The framework produces cache miss counts for arbitrarily-nested loops. The framework gives the actual cache miss count incurred by a loop nest sequence, and not merely the sum of cache misses incurred by each individual loop nest in isolation. The framework models the data access patterns of a program whether it uses a standard row- or column-major array layout, or a novel nonlinear array layout based on bit interleavings of the binary expansions of the array coordinates. As this document will show, the cache analysis framework of this dissertation does not suffer from any of the weaknesses outline above.

#### 1.3 Thesis Contributions

The following are statements of the major contributions in this dissertation.

- A new alternative cache miss classification has advantages over traditional cache miss classification schemes. Unlike traditional miss classification schemes, the alternative miss classification allows combining of the cache behaviors of individual program fragments to obtain the cache behavior of the sequence of such program fragments. Determining the state of the cache at certain points in program execution is critical to accurately combining the cache behavior of the program fragments in the sequence. The alternative miss classification also permits approximation of the number of cache misses incurred by a program fragment sequence with a small error bound, which avoids the computation of cache state.

- The cache analysis framework of this dissertation models the behavior of loop nests executing in set-associative caches. The framework produces the exact cache miss count incurred by a loop nest executing in caches of arbitrary associativity. Assuming a least-recently used (LRU) cache replacement policy, a single pass through the method gives cache miss counts for multiple associativity values.

- The cache analysis framework of this dissertation models the data access patterns of arbitrarily-nested loops using Presburger arithmetic and exploits connections between

Presburger arithmetic, automata theory, and graph theory to identify cache misses. The framework employs an exact model of the behavior of arbitrarily-nested loops executing in the presence of set-associative caches, expressed in Presburger arithmetic. To determine the number of cache misses incurred by a loop nest, the framework applies automata-theoretic methods for counting and enumerating Presburger formula solutions to the formulas describing cache behavior. The counting method builds on a connection between automata theory and graph theory to efficiently count solutions. The automata-theoretic methods are not specific to cache behavior formulas and are relevant to many other applications in program analysis, such as load balancing.

- The cache analysis framework of this dissertation is flexible. The inherent flexibility of the framework derives from the use of Presburger formulas, as any behavior describable in Presburger arithmetic may be modeled in the framework. As a result, the framework can identify cache misses according to either the new alternative miss classification or traditional miss classification. Moreover, the framework handles the row- and column-major array layout functions, as well as nonlinear array layout functions expressible in Presburger arithmetic.

- The cache analysis framework of this dissertation is a tool for improving program behavior and exploring the space of memory design. The framework can be used to investigate the effect of changes in the values of code and data transformation parameters. The framework models caches of virtually any configuration, making it well suited to model data cache and translation lookaside buffer (TLB) misses in a wide variety of memory systems.

#### 1.4 Limitations

There are some limitations on the loop nests whose memory behavior may be analyzed by the framework presented in this dissertation, pertaining to control structure and data structure.

Control structure. The framework analyzes sequences of nested count-controlled loops (i.e., loops that execute a specified number of times), and the number of times the loops execute must be known at compile time. For example, consider the three loop nests in Figure 1.3. Loop nest **a** is analyzable because it is clear how many times each of the two loops execute. Loop nest **b** is analyzable only if the value of MAX is known at compile time. Loop nest **c** is not analyzable since the number of times the loop executes depends on the values stored in array **A**, which are not known at compile time.

The framework can analyze loop nest **a** in Figure 1.3 because the lower and upper bounds on the loop control variables **i** and **j** are either values known at compile time or are linear expressions of the control variables of the outer loops. The lower bound of loop control variable

do i = 0, 1000 do i = 0, MAX do j =

$$2*i+5$$

, 1000 do j =  $2*i+5$ , MAX  $x += A[i,3*j+i]$   $x += A[i,3*j+i]$  enddo enddo enddo enddo  $x += A[i,3*j+i]$  enddo  $x += A[i]$   $x += A$

Figure 1.3: Example loop nests: **a.** analyzable by the framework, **b.** possibly analyzable by the framework, **c.** not analyzable by the framework.

j is 2\*i+5, which is a linear expression of the control variable of the outer loop i. If the lower bound of loop control variable j were instead 2\*i\*i+5, loop a would not be analyzable because the expression is not linear in i. This restriction on lower and upper loop bounds is due to the underlying polyhedral model [47] of loop nests and the use of Presburger arithmetic to model loop nest behavior.

Also, the framework analyzes loop nests that execute on a uniprocessor.

**Data structure.** The framework of this dissertation analyzes loop nests that access memory via array references.

The framework can analyze loop nest  $\mathbf{a}$  in Figure 1.3 because the expressions for indexing array  $\mathbf{A}$  are linear expressions of the control variables in the loops containing the array reference. The index expressions are  $\mathbf{i}$  and  $3*\mathbf{j}+\mathbf{i}$ . If one of these expressions were instead  $3*\mathbf{i}*\mathbf{j}$ , loop nest  $\mathbf{a}$  would not be analyzable because the expression is not linear in  $\mathbf{i}$  and  $\mathbf{j}$ . As with lower and upper loop bounds, this restriction on array index expressions is due to the polyhedral model and the use of Presburger arithmetic.

If the array reference in loop nest **a** in Figure 1.3 were instead an indirect reference such as A[B[i,3\*j+i]], the framework could not analyze the loop nest, because the values stored in array B are not known at compile time.

Given these limitations, the analysis framework presented in this dissertation can analyze loop nests typically found in dense matrix computations, such as linear algebra, Fourier and related transforms, and low-level image processing. The framework cannot analyze loop nests that perform sparse matrix computations, as they tend to have indirect array references. For more on the types of loop nests whose memory behavior may be analyzed by the framework of this dissertation, see Section 4.1.

### 1.5 Organization

The remainder of this dissertation is organized as follows.

Chapter 2 reviews terminology and background material relevant to this dissertation. In

particular, this chapter discusses the underlying models of cache memory, loop nests, and array referencing, which are fundamental to the analytical framework presented here. This chapter also discusses Presburger arithmetic, automata theory, and their connection, on which the framework builds to obtain an accurate model of cache behavior.

Chapter 3 introduces a new alternative classification of cache misses that addresses a short-coming of traditional miss classification schemes. With traditional miss classification schemes, it is not possible to obtain the exact cache behavior of a sequence of program fragments from the cache behavior of the individual fragments. This chapter shows the role of cache state in producing an accurate cache miss count for a sequence of program fragments and provides an option for approximating the number of cache misses in the sequence with a small error bound.

Chapter 4 discusses how to model data access patterns in Presburger arithmetic. First, this chapter introduces the notions of neighborhood and witness, which serve to identify the situations that cause a cache miss. Then, the chapter shows how to express various types of witnesses as formulas of Presburger arithmetic and gives rules for identifying cache misses based on the existence of such witnesses.

Chapter 5 explains how the analysis framework exploits a fundamental connection between Presburger arithmetic and automata theory to count solutions in Presburger formulas. This chapter illustrates how accepting DFA paths encode the formula solutions and gives algorithms for counting and enumerating such paths. The key to efficiently counting the number of accepting paths in a DFA is to treat the DFA as a directed graph. To reveal the number of cache misses incurred by a loop nest, the framework applies the automata-theoretic methods for counting and enumerating Presburger formula solutions to the formulas describing cache behavior given in Chapter 4.

Chapter 6 provides a high-level view of the analysis framework presented in this dissertation and describes the tools used in the implementation of the framework. The framework employs existing tools to extract relevant loop nest parameters from source code, to simplify Presburger formulas describing cache behavior, and to represent a cache behavior formula as a DFA whose accepting paths recognize the formula's solutions.

Chapter 7 extends the analysis framework presented here to handle nonlinear data layouts expressible in Presburger arithmetic. The analysis framework assumes an LRU cache replacement policy. This chapter also considers the first-in first-out (FIFO) cache replacement policy and gives insights on why it cannot be completely modeled by the framework.

Chapter 8 applies and validates the analysis framework of this dissertation on a variety of example programs. Experiments demonstrate the framework's ability to model exactly the behavior of loop nests executing in set-associative caches by giving accurate cache miss counts for virtually any value of associativity for all example programs. This chapter illustrates the flexibility of the framework by giving cache miss counts for data caches and TLBs and by

considering example programs with both canonical and nonlinear data layouts. This chapter also shows the usefulness of the framework in several example loop transformations.

Chapter 9 compares the analysis framework presented here to existing work for memory behavior analysis. In particular, this chapter points out how the analysis framework of this dissertation goes beyond related work by addressing the weaknesses outlined in Section 1.2.

Finally, Chapter 10 concludes the dissertation and provides directions for future work.

## Chapter 2

## Terminology and Notation

This chapter provides background material and defines notation for the analytical framework presented in this dissertation. Section 2.1 describes the static structure and dynamic behavior of cache memory. Section 2.2 gives the underlying model for loop nests, while Section 2.3 gives the underlying model for referencing array variables in loop nests. Section 2.4 reviews Presburger arithmetic and its worst-case complexity. Section 2.5 discusses the connection between Presburger arithmetic and automata theory.

#### 2.1 Cache Basics

A cache is a small, fast memory located between the processor and main memory designed to capture frequently referenced data [64, 66, 67, 104, 105, 114]. This section reviews the static structure of a cache (Section 2.1.1), the dynamic behavior of a cache (Section 2.1.2), and a special type of cache—the translation lookaside buffer (Section 2.1.3).

#### 2.1.1 Static Cache Structure

From a hardware perspective, a large number of parameters characterize a cache [105]. However, it is standard to characterize the primary organization of a cache with the following three parameters: associativity  $\mathcal{A}$ , blocksize  $\mathcal{B}$ , and capacity  $\mathcal{C}$  [114]. Capacity, expressed in bytes, is the total amount of data that a cache can hold. The seemingly complex organization of a cache is motivated by the need to quickly locate data. On request of a memory byte address, a search of the entire cache is avoided by quickly narrowing the search to a small portion of the cache. Then, all memory in this limited portion of cache is simultaneously checked to locate the requested memory address. A memory byte address<sup>1</sup> is divided in such a way that this limited portion of the cache is easily identified. Figure 2.1 shows how a memory byte address

<sup>&</sup>lt;sup>1</sup>This address may be either a physical memory address or a virtual memory address. The framework presented in this dissertation assumes that the data cache is virtually indexed. Fortunately, most operating systems employ page coloring [78], which ensures that the cache set indexes of physical and virtual addresses are identical. Therefore, whether it is a physical address or a virtual address is not of concern.

Figure 2.1: The portions of a memory byte address. The index selects the cache set, and the tag disambiguates memory blocks in a set. The block offset locates the desired data within a memory block at the memory block address.

is divided. First, the higher-order bits specify the address of the memory block containing the memory byte address, and the block offset identifies the memory byte address within the memory block. A memory block is the unit of mapping main memory to cache. For a cache with blocksize  $\mathcal{B}$ , each memory block holds  $\mathcal{B}$  contiguous bytes of memory. A cache has  $\frac{\mathcal{C}}{\mathcal{B}}$  cache frames, and each frame either may be occupied by a memory block or may be empty. At no time may two cache frames contain the same memory block. The memory block address is further partitioned, with the higher-order bits specifying a tag and the lower-order bits specifying a cache set index. The cache set index eliminates the need to search the entire cache for a memory address by quickly selecting the cache set (a small portion of the cache) to which a memory block maps. The tag disambiguates memory blocks within the same cache set, and simultaneous checking of the tags for all memory blocks in the cache set rapidly locates the requested memory address or determines its absence from the cache. A cache set is the collection of  $\mathcal{A}$  frames that a particular memory block may occupy in the cache. A cache set contains one cache frame at each of A degrees of associativity, and the collection of frames from all sets at each degree of associativity is called a way. The number of cache sets,  $\mathcal{S}$ , is equal to  $\frac{\mathcal{C}}{AB}$ . Figure 2.2 illustrates the cache structure described above. In general,  $\mathcal{B}$  and  $\mathcal{S}$ are powers of two to allow quick determination of the cache set index and block offset using a bit-level mask (see Figure 2.1).

Of the four cache parameters  $\mathcal{A}$ ,  $\mathcal{B}$ ,  $\mathcal{C}$ , and  $\mathcal{S}$ , only three are independent of one another. While associativity  $\mathcal{A}$ , blocksize  $\mathcal{B}$ , and capacity  $\mathcal{C}$  are considered the main cache parameters, the number of sets  $\mathcal{S}$  is critical in mapping data to cache. Notice that the size of the cache set index is  $\log_2 \mathcal{S}$ . The representation  $(\mathcal{A}, \mathcal{B}, \mathcal{C}; \mathcal{S})$  denotes a cache with associativity  $\mathcal{A}$ , blocksize  $\mathcal{B}$ , capacity  $\mathcal{C}$ , and  $\mathcal{S}$  cache sets. Consistent with the convention that  $\mathcal{A}$ ,  $\mathcal{B}$ , and  $\mathcal{C}$  are the main cache parameters, the semicolon signifies that  $\mathcal{S}$  is an auxiliary parameter. If  $\mathcal{A} = \frac{\mathcal{C}}{\mathcal{B}}$ , then  $\mathcal{S} = 1$  and a memory block may reside in any frame of the cache; such a cache is designated fully-associative. If  $\mathcal{A} = 1$ , then a memory block must reside in a particular frame; such a cache is designated direct-mapped [66]. Figure 2.3 shows five caches with various values of associativity  $\mathcal{A}$ , fixing capacity  $\mathcal{C}$  and blocksize  $\mathcal{B}$ . Notice how the number of sets  $\mathcal{S}$  and the shape of the cache change with the associativity.

|           | way 0                                                | way 1                                                |  | way $A-1$                                            |

|-----------|------------------------------------------------------|------------------------------------------------------|--|------------------------------------------------------|

| set 0     | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |  | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |

| set 1     | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |  | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |

| :         | :                                                    |                                                      |  | :                                                    |

| set $S-1$ | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |  | $a \ cache \ frame \ (\mathcal{B} \ \mathrm{bytes})$ |

Figure 2.2: Representation of an A-way set-associative cache with blocksize  $\mathcal{B}$ ,  $\mathcal{S}$  cache sets, and capacity  $\mathcal{C} = A \cdot \mathcal{B} \cdot \mathcal{S}$ .

Figure 2.3: The different shapes of caches with fixed capacity  $\mathcal{C}$  and blocksize  $\mathcal{B}$ , varying associativity  $\mathcal{A}$ . Notice how the mapping of data to cache will differ for each shape.

The four cache parameters described above are used to define the mapping<sup>2</sup> of blocks from main memory to cache memory. The *Block* function (with  $Block(m) = \lfloor \frac{m}{\mathcal{B}} \rfloor$ ) associates a memory byte address with a unique memory block address. The *Set* function (with  $Set(b) = b \mod \mathcal{S}$ ) associates a memory block address with a unique cache set.

For a program executing in a direct-mapped cache, at any point during execution of the program each set of the cache either contains a memory block or is empty. If a program executes in a two-way set-associative cache, each set of the cache contains two distinct memory blocks, one memory block, or is empty at any point during executing of the program. In general,

<sup>&</sup>lt;sup>2</sup>Other schemes for mapping from main memory to cache have been proposed, such as skewed-associative caches [112, 113] and XOR-based cache placement [63], but the scheme reviewed here is the universally accepted way of mapping blocks of main memory to cache memory in commercial processors.

Figure 2.4: Wraparound value w = Wrap(m), for memory byte address m. The cache set number s = 1 and wraparound value w identify the memory block address for m.

for an  $\mathcal{A}$ -way set-associative cache, each set of the cache contains one to  $\mathcal{A}$  distinct memory blocks or is empty at any point during execution of the program. The **state of the cache** is the collection of memory blocks residing in each cache set at any point during the execution of a program such that the memory blocks in each cache set are ordered by recency of access. Maintaining the order of most recently accessed is convenient for determining which memory blocks are candidates for replacement using the least-recently used (LRU) policy. The state of cache set s,  $\mathfrak{C}_s = \{b_1, \ldots, b_n\}$ , is the set of memory block addresses resident in cache set s, where  $n \in [0, \mathcal{A}]$  is the size of  $\mathfrak{C}_s$ . The state of cache set s is empty if no memory blocks have yet mapped to cache set s (i.e.,  $\mathfrak{C}_s = \{\}$  and s = 0). The contents of  $\mathfrak{C}_s$  have an implicit ordering that indicates the most recently accessed. Memory block address s is more recently accessed than s if s if s is more recently accessed. Memory block address s is more recently accessed than s if s if s is more recently accessed than s if s is more recently accessed that s is accessed that s is accessed that s is accessed to

Recall from Figure 2.1 that the lower-order bits of a memory block address specify the cache set to which it maps, and the higher-order bits (called the tag) distinguish the memory block from others in the same set. I refer to the tag in a memory address as the **wraparound value**. The Wrap function (with  $Wrap(m) = \lfloor Block(m)/S \rfloor$ ) associates a memory byte address with a unique wraparound value. Figure 2.4 shows the wraparound value w for a memory byte address m, and that all memory byte addresses with a block address equal to xS up to (x + 1)S - 1 have the same wraparound value x. The intuition of a wraparound value w is that memory

```

\mathbb{L}_{\text{mm}} \colon \qquad \text{do i = 0, } t-1 \\ \qquad \text{do j = 0, } u-1 \\ S_0 \colon \qquad \text{c = Z[i,j]} \\ \qquad \text{do k = 0, } v-1 \\ S_1 \colon \qquad \text{c += X[i,k] * Y[k,j]} \\ \qquad \text{enddo} \\ S_2 \colon \qquad \text{Z[i,j] = c} \\ \qquad \text{enddo} \\ \end{cases}

```

Figure 2.5: The running example loop nest  $\mathbb{L}_{mm}$ .

Figure 2.6: Wraparound values for the memory locations accessed by loop nest  $\mathbb{L}_{mm}$ .

"wraps around" the cache w times before m maps to set s. Notice that each cache set number and wraparound value pair identifies a unique memory block address, and each memory block address has a unique set number and wraparound value pair. Thus, it is a two-dimensional representation of a memory location (set number, wraparound value), which is an alternative to the traditional one-dimensional representation (memory byte address). In modeling the data access patterns of programs, the framework of this dissertation considers the behavior in each cache set individually and uses wraparound values to specify memory blocks.

In order to demonstrate the concept of a wraparound, consider the loop nest in Figure 2.5, which is the running example used for illustration throughout this document. Loop nest  $\mathbb{L}_{mm}$ , which is normalized<sup>3</sup> and language-neutral, performs the matrix multiplication  $Z_{t\times u}=X_{t\times v}\cdot Y_{v\times u}$ . Suppose that t=u=v=20 and that all arrays contain double-precision elements of 8 bytes each. For an  $(\mathcal{A}, 32, 4096 \cdot \mathcal{A}; 128)$  cache, Figure 2.6 shows one way of storing the three arrays in memory. Elements of array X have memory block addresses ranging from 0 to 99 and occupy memory locations with a wraparound value of 0. Some elements in array Y occupy memory locations with a wraparound value of 0, and other elements are in memory locations with a wraparound value of 1. Similarly, some elements of array Z occupy memory locations with a wraparound value of 1, and others with a wraparound value of 2.

<sup>&</sup>lt;sup>3</sup>In a normalized loop nest, all loops have step size equal to one [135].

Note that the wraparound value of a memory address does not have to be equivalent to its tag. As Chapter 4 discusses, the analytical framework presented in this dissertation uses the distinctness of wraparounds, and not their actual values, to model cache behavior. Therefore, it is always valid to change the starting addresses of all referenced arrays by some multiple of  $\mathcal{B} \cdot \mathcal{S}$ , in effect changing the actual values of all wraparounds but not their distinctness. Suppose that for the running example loop nest  $\mathbb{L}_{mm}$  (with t = u = v = 20, 8-byte array elements, and an  $(\mathcal{A}, 32, 4096 \cdot \mathcal{A}; 128)$  cache), the starting address of array X in memory is 12288, the starting address of array Y is 15488, and the starting address of array Y is 18688. All elements of array X have a wraparound value of 3. Elements of array Z have either a wraparound value of 4 or a wraparound value of 5. Subtracting 12288 =  $3 \cdot 32 \cdot 128$  from each starting array address gives the same wraparound values as in Figure 2.6. Thus, loop nest  $\mathbb{L}_{mm}$  with starting addresses 12288, 15488, and 18688 has the the same cache miss behavior as with the original starting array addresses of 0, 3200, and 6400.

#### 2.1.2 Dynamic Cache Behavior

When the processor requests data at a memory address m, a cache hit occurs if  $Block(m) \in$  $\mathfrak{C}(Set(Block(m)))$ . The cache satisfies the memory request after the hit time (i.e., the time required to fetch the requested data). A cache miss occurs if  $Block(m) \notin \mathfrak{C}\langle Set(Block(m)) \rangle$ . During a cache miss, the lower levels of memory satisfy the memory request and place memory block Block(m) in cache set s = Set(Block(m)), after the miss penalty (see equation (1.3)). A **replacement algorithm** selects which cache frame in set s to update with the new memory block. Ideally, an algorithm should select the cache frame containing the memory block that will be unused for the longest time in the future; this is known as the optimal replacement algorithm [13]. Because the optimal replacement algorithm requires perfect knowledge of the future, it is not implementable in hardware. However, it does serve to gauge the effectiveness of other replacement algorithms. Least-recently used (LRU), first-in first-out (FIFO), and random are three popular replacement algorithms [64]. The LRU algorithm chooses to replace the memory block in set s that has been unused for the longest time. The FIFO algorithm chooses to replace the memory block that has resided in set s for the longest time. The random algorithm chooses randomly among the memory blocks currently residing in set s. Note that for direct-mapped caches, a replacement algorithm is not necessary since each set holds only one memory block. The analytical framework presented in this dissertation assumes a LRU replacement policy. Section 7.2 discusses why the framework does not assume a FIFO

$<sup>^4</sup>$ As the cache associativity increases, the number of bits required to implement the LRU algorithm grows exponentially in  $\mathcal{A}$  [64]. As a result, LRU replacement is most often approximated (called pseudo-LRU) [64]. The framework of this dissertation assumes true LRU replacement. The possibility of a slight mismatch in a program's cache behavior with true LRU and its behavior with pseudo-LRU is beyond the scope of this dissertation.

replacement policy.

Assuming an LRU replacement policy, the state of the cache changes after a cache hit or miss to preserve the most-recently-accessed ordering and to update the contents of cache state (in the case of a miss).

**Definition 2.1** For a memory access a that touches memory block b in cache set s,  $\mathfrak{C}\langle s\rangle = \{b_1, \ldots, b_n\}$  becomes  $\mathfrak{C}'\langle s\rangle = UpdateState(\mathfrak{C}\langle s\rangle, a)$  where

$$UpdateState(\mathfrak{C}\langle s \rangle, \mathsf{a}) = \begin{cases} \{b, b_1, \dots, b_{i-1}, b_{i+1}, \dots, b_n\} & \text{if } b = b_i \text{ hits,} \\ \{b, b_1, \dots, b_n\} & \text{if } b \text{ misses and } n < \mathcal{A}, \\ \{b, b_1, \dots, b_{n-1}\} & \text{if } b \text{ misses and } n = \mathcal{A}. \end{cases}$$

$$(2.1)$$

Traditional cache miss categories are helpful in capturing the cause of a cache miss. A compulsory miss (or cold miss) occurs on the first access to a memory block because the block cannot already be resident in cache. Compulsory misses cannot be avoided, except with prefetching. A capacity miss occurs when accessing a memory block that was previously in cache but was replaced because the cache could not contain all of the memory blocks needed to execute a program. Capacity misses are due to the restricted size of the cache. A conflict miss occurs when accessing a memory block that was previously in a cache set but was replaced because too many other memory blocks mapped to the same cache set. Conflict misses are due to too many memory blocks mapping to a fraction of the cache. One way to compare capacity and conflict misses is to consider associativity. Capacity misses occur independent of the associativity of a cache (i.e., a capacity miss in an LRU set-associative cache with capacity  $\mathcal{C}$  also misses in an LRU fully-associative cache with capacity  $\mathcal{C}$ ). Conflict misses depend on associativity (i.e., a conflict miss in an LRU set-associative cache with capacity  $\mathcal{C}$ hits in an LRU fully-associative cache with capacity  $\mathcal{C}$ ). This classification of cache misses is known as the 3C model [67]. Because both capacity and conflict misses describe accesses to memory blocks that have resided in cache but were replaced, they are often grouped together as replacement misses. I refer to this classification of cache misses as the compulsoryreplacement miss classification.

#### 2.1.3 A Special Cache—the TLB

The cache described above is a data cache, storing the contents of the most frequently referenced blocks of main memory close to the processor. This work also considers another type of cache—the translation lookaside buffer (TLB). The TLB is a cache of memory address translations. TLB miss penalties are often larger than data cache miss penalties, contributing significantly to poor program performance.

Many programs operate on more data than main memory can hold, with the remaining data contained in secondary storage (*i.e.*, hard disk). Virtual memory is a technique for automatically managing these two levels of memory so that processes, such as an executing

program, need not be aware of whether the required data is in main memory or in secondary storage [66]. When a program needs data, the processor produces a virtual memory address for the data. The address space of virtual memory is divided into pages, and each virtual address is split into a virtual page number and an offset within the page. A page table gives the physical page number corresponding to a virtual page number, which combines with the page offset to give the complete physical address. The physical memory address indicates the actual memory location of the requested data.

The relationship between main memory and disk memory is similar to the relationship between cache and main memory. While a memory block is the unit of mapping to cache, the unit of mapping to main memory is a page. A memory block not found in the cache incurs a cache miss, while a page not found in main memory incurs a page fault. The critical difference in the two relationships is the placement of memory blocks in cache and the placement of pages in main memory. A page can be placed anywhere in main memory, and the mapping of pages to main memory can change over time. A page table is necessary to keep track of the translations from the virtual addresses of pages in main memory to their physical addresses in disk memory. The placement of a memory block into a particular set of the cache is well defined by the memory byte address, and there is no need for a table to keep track of the mappings from main memory to cache.