## SHARING GPUS FOR REAL-TIME AUTONOMOUS-DRIVING SYSTEMS

## Ming Yang

A dissertation submitted to the faculty at the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2020

Approved by:

James H. Anderson

Parasara Sridhar Duggirala

Jan-Michael Frahm

Shahriar Nirjon

F. Donelson Smith

Shige Wang

©2020 Ming Yang ALL RIGHTS RESERVED

#### ABSTRACT

Ming Yang: Sharing GPUs for Real-Time Autonomous-Driving Systems (Under the direction of James H. Anderson)

Autonomous vehicles at mass-market scales are on the horizon. Cameras are the least expensive among common sensor types and can preserve features such as color and texture that other sensors cannot. Therefore, realizing full autonomy in vehicles at a reasonable cost is expected to entail computer-vision techniques. These computer-vision applications require massive parallelism provided by the underlying shared accelerators, such as graphics processing units, or GPUs, to function "in real time." However, when computer-vision researchers and GPU vendors refer to "real time," they usually mean "real fast"; in contrast, certifiable automotive systems must be "real time" in the sense of being *predictable*.

This dissertation addresses the challenging problem of how GPUs can be shared predictably and efficiently for real-time autonomous-driving systems. We tackle this challenge in four steps.

First, we investigate NVIDIA GPUs with respect to scheduling, synchronization, and execution. We conduct an extensive set of experiments to infer NVIDIA GPU scheduling rules, which are unfortunately undisclosed by NVIDIA and are beyond access owing to their closed-source software stack. We also expose a list of pitfalls pertaining to CPU-GPU synchronization that can result in unbounded response times of GPU-using applications. Lastly, we examine a fundamental trade-off for designing real-time tasks under different execution options. Overall, our investigation provides an essential understanding of NVIDIA GPUs, allowing us to further model and analyze GPU tasks.

Second, we develop a new model and conduct schedulability analysis for GPU tasks. We extend the well-studied sporadic task model with additional parameters that characterize the parallel execution of GPU tasks. We show that NVIDIA scheduling rules are subject to fundamental capacity loss, which implies a necessary total utilization bound. We derive response-time bounds for GPU task systems that satisfy our schedulability conditions.

Third, we address an industrial challenge of supplying the throughput performance of computer-vision frameworks to support adequate coverage and redundancy offered by an array of cameras. We re-think

the design of convolution neural network (CNN) software to better utilize hardware resources and achieve increased throughput (number of simultaneous camera streams) without any appreciable increase in per-frame latency (camera to CNN output) or reduction of per-stream accuracy.

Fourth, we apply our analysis to a finer-grained graph scheduling of a computer-vision standard, OpenVX, which explicitly targets embedded and real-time systems. We evaluate both the analytical and empirical real-time performance of our approach.

To my sister, Yuan Yang.

#### ACKNOWLEDGEMENTS

It was serendipity that led me to UNC five years ago. As I stand at the end point of this journey now, with this dissertation being completed, I realize that anything I accomplished would not have been possible had I not received all the guidance, aid, and support from people I met. I am indebted and thankful to them.

First and foremost, I would like to express my deepest appreciation to my advisor, Jim Anderson, for his unwavering support, for his patience whenever I was slowly progressing, for his motivation and encouragement every time I was frustrated, and for his guidance that led me forward. I would also like to thank my dissertation committee: Parasara Sridhar Duggirala, Jan-Michael Frahm, Shahriar Nirjon, F. Donelson Smith, and Shige Wang, for their valuable advice.

I would also like to extend my sincere thanks to many colleagues I worked with. In particular, I am especially thankful to people who helped with the work of this dissertation: Tanya Amert, Joshua Bakita, Nathan Otterness, Thanh Vu, and Kecheng Yang. This dissertation would not have been possible without their contributions.

I am also grateful for the internships that General Motors and Aurora Innovation offered so I had the opportunities to enjoy sitting in the autonomous vehicles and experiencing how they work. I very much appreciate Shige Wang for his advice regarding and beyond my research and career. I am also thankful to Glenn Elliott for many inspiring discussions. I thank Joseph D'Ambrosio and Ken Conley for their support.

I am also thankful to my other co-authors: Alex Berg, Pontus Ekberg, Vance Miller, Saujas Nandi, Catherine Nemitz, Eunbyung Park, Sarah Rust; and other people I worked with in UNC: Shareef Ahmed, Akash Bapat, Lee Barnett, Micaiah Chisholm, Calvin Deutschbein, Shiwei Fang, Cheng-Yang Fu, Zhishan Guo, Clara Hobbs, Bashima Islam, Tamzeed Islam, Namhoon Kim, Seulki Lee, Yubo Luo, Mac Mollison, Sims Osborne, Abhishek Singh, Stephen Tang, Peter Tong, Sergey Voronov, and Bryan Ward.

I gratefully acknowledge the assistance I received from the staff of the UNC Computer Science Department. Special thanks to Denise Kenney, Beth Mayo, Jodie Gregoritsch, Adia Ware, and Mellisa Wood for keeping the graduate school paperwork in order. Many thanks to Murray Anderegg, Bil Hays, David Musick, Mike Stone, and other staff for their help with various hardware and system issues.

I cannot leave Chapel Hill without mentioning my friends. I owe special thanks to Weiwei Li, for preventing me from insanely giving up my PhD study. I was also very lucky to meet Shiwei Fang by chance in the roommate lottery. Thanks to them and my other friends for enriching my PhD life experience.

As I believe everyone needs a supporting system to survive the PhD process, mine is my dearest sister—in my darkest time or whenever, she was always there for me, persuasive and supportive, and finally, I share this victorious ending of this journey with her. Lastly, I thank my parents for their unwavering support, and my wife for her patience and love.

The research in this dissertation was funded by NSF grants CPS 1446631 and CPS 1837337, ARO grant W911NF-17-1-0294, and support from General Motors.

# TABLE OF CONTENTS

| LIST O  | F TABL                               | ES          |                                                                 | xiii |

|---------|--------------------------------------|-------------|-----------------------------------------------------------------|------|

| LIST O  | F FIGUE                              | RES         |                                                                 | xiv  |

| LIST O  | F ABBR                               | EVIATIO     | NS                                                              | xvi  |

| Chapter | 1: Intro                             | duction     |                                                                 | 1    |

| 1.1     | Compu                                | iter Vision | in Autonomous Driving                                           | 2    |

| 1.2     | Graphi                               | cs Process  | sing Units                                                      | 4    |

| 1.3     | Real-Time Systems and GPU Scheduling |             |                                                                 | 6    |

| 1.4     | Thesis                               | Statement   |                                                                 | 8    |

| 1.5     | Contril                              | outions     |                                                                 | 8    |

|         | 1.5.1                                | A Study     | of NVIDIA GPUs beyond Official Documentation                    | 9    |

|         | 1.5.2                                | A Model     | of GPU Execution                                                | 10   |

|         | 1.5.3                                | A Respo     | nse-Time Bound Analysis for Applications Sharing GPUs           | 10   |

|         | 1.5.4                                | A Comp      | uter-Vision Framework Providing Improved Throughput             | 11   |

|         | 1.5.5                                | A Case S    | Study Evaluating Analytical and Empirical Real-Time Performance | 12   |

| 1.6     | Organi                               | zation      |                                                                 | 13   |

| Chapter | 2: Back                              | ground      |                                                                 | 14   |

| 2.1     | Autono                               | omous Dri   | ving                                                            | 14   |

|         | 2.1.1                                | State of t  | he Art                                                          | 14   |

|         | 2.1.2                                | Autonom     | nous-Driving System Architecture                                | 17   |

|         |                                      | 2.1.2.1     | Architecture                                                    | 17   |

|         |                                      | 2.1.2.2     | Sensor Hardware                                                 | 19   |

|         |                                      | 2.1.2.3     | Perception                                                      | 20   |

|     |                   | 2.1.2.4             | Planning and Control                              | 23 |  |

|-----|-------------------|---------------------|---------------------------------------------------|----|--|

|     | 2.1.3             | Summar              | y                                                 | 24 |  |

| 2.2 | Compu             | ıter Vision         | for Autonomous Driving                            | 24 |  |

|     | 2.2.1             | Methods             |                                                   | 25 |  |

|     |                   | 2.2.1.1             | Classic Pipelines                                 | 25 |  |

|     |                   | 2.2.1.2             | Deep Learning Methods                             | 26 |  |

|     | 2.2.2             | Object-D            | Detection Accuracy Metrics                        | 29 |  |

|     |                   | 2.2.2.1             | IoU, Precision, and Recall                        | 29 |  |

|     |                   | 2.2.2.2             | Precision-Recall Curve and Mean Average Precision | 30 |  |

|     | 2.2.3             | Framewo             | orks and Libraries                                | 31 |  |

|     | 2.2.4             | OpenVX              | Standard                                          | 33 |  |

|     | 2.2.5             | Challeng            | es of Real-Time Certification Amenable Framework  | 35 |  |

| 2.3 | GPUs              | Us and Accelerators |                                                   |    |  |

|     | 2.3.1             | Accelera            | tors                                              | 36 |  |

|     | 2.3.2             | GPU Hai             | rdware Architecture                               | 39 |  |

|     |                   | 2.3.2.1             | CUDA-Enabled Devices                              | 41 |  |

|     | 2.3.3             | GPU Pro             | gramming Model                                    | 42 |  |

|     | 2.3.4             | Prior Wo            | rk on Non-Real-Time GPUs                          | 46 |  |

|     |                   | 2.3.4.1             | GPU Reverse Engineering                           | 47 |  |

|     |                   | 2.3.4.2             | GPU Resource Management                           | 48 |  |

|     |                   | 2.3.4.3             | GPU Sharing                                       | 49 |  |

|     |                   | 2.3.4.4             | GPU Virtualization                                | 51 |  |

|     |                   | 2.3.4.5             | GPU Scheduling                                    | 53 |  |

|     | 2.3.5             | Challeng            | es for Real-Time GPUs                             | 55 |  |

| 2.4 | Real-Time Systems |                     |                                                   |    |  |

|     | 2.4.1             | Real-Tim            | ne Task Model                                     | 57 |  |

|     | 2.4.2             | Scheduling          |                                                   |    |  |

|     | 243               | Response            | 2-Time Rounds                                     | 60 |  |

|         | 2.4.4                                                                    | Real-Time DAG Scheduling                    | 61  |  |  |

|---------|--------------------------------------------------------------------------|---------------------------------------------|-----|--|--|

|         | 2.4.5                                                                    | Real-Time Frameworks                        | 63  |  |  |

|         | 2.4.6                                                                    | Real-Time GPUs                              | 64  |  |  |

| 2.5     | Chapte                                                                   | er Summary                                  | 67  |  |  |

| Chapter | 3: Sche                                                                  | duling, Synchronization, and Execution      | 68  |  |  |

| 3.1     | Basic (                                                                  | GPU Scheduling Rules                        | 71  |  |  |

|         | 3.1.1                                                                    | Motivating Experiment                       | 71  |  |  |

|         | 3.1.2                                                                    | Scheduling Rules                            | 72  |  |  |

| 3.2     | Additio                                                                  | onal Complexities                           | 78  |  |  |

|         | 3.2.1                                                                    | The NULL Stream.                            | 78  |  |  |

|         | 3.2.2                                                                    | Stream Priorities                           | 79  |  |  |

|         | 3.2.3                                                                    | Multiple Processes and Other Complications  | 84  |  |  |

| 3.3     | Synchi                                                                   | ronization and Blocking                     | 86  |  |  |

|         | 3.3.1                                                                    | Overview of GPU Synchronization             | 87  |  |  |

|         |                                                                          | 3.3.1.1 Explicit Synchronization            | 87  |  |  |

|         |                                                                          | 3.3.1.2 Implicit Synchronization            | 89  |  |  |

|         | 3.3.2                                                                    | Overcoming Synchronization-Related Pitfalls | 91  |  |  |

| 3.4     | Concu                                                                    | rrency and Performance                      | 92  |  |  |

|         | 3.4.1                                                                    | Multi-Process Service (MPS)                 | 92  |  |  |

|         | 3.4.2                                                                    | Case Study of Computer-Vision Tasks         | 93  |  |  |

| 3.5     | Perils of                                                                | of CUDA Programming for Real-Time Tasks     | 97  |  |  |

|         | 3.5.1                                                                    | Synchronous Defaults                        | 98  |  |  |

|         | 3.5.2                                                                    | Flawed Documentation                        | 99  |  |  |

|         | 3.5.3                                                                    | Unknown Future                              | 100 |  |  |

| 3.6     | Chapte                                                                   | er Summary                                  | 101 |  |  |

| Chapter | Chapter 4: Task Model and Schedulability Analysis for Tasks Sharing GPUs |                                             |     |  |  |

| 4.1     | DAG-l                                                                    | pased Task Model                            | 103 |  |  |

| 4.2    | GPU F     | GPU Response-Time Bound                                          |     |  |  |

|--------|-----------|------------------------------------------------------------------|-----|--|--|

|        | 4.2.1     | NVIDIA GPU Details                                               | 107 |  |  |

|        | 4.2.2     | System Model                                                     | 108 |  |  |

|        | 4.2.3     | Total Utilization Constraint                                     | 110 |  |  |

|        | 4.2.4     | Response-Time Bound                                              | 114 |  |  |

| 4.3    | Chapte    | er Summary                                                       | 118 |  |  |

| Chapte | r 5: Impr | rove CNN Frameworks for Autonomous-Driving Applications          | 120 |  |  |

| 5.1    | Backg     | ground                                                           | 123 |  |  |

|        | 5.1.1     | NVIDIA DRIVE PX2                                                 | 123 |  |  |

|        | 5.1.2     | YOLO and Darknet                                                 | 124 |  |  |

| 5.2    | Relate    | ed Work                                                          | 125 |  |  |

| 5.3    | Systen    | n Design                                                         | 125 |  |  |

|        | 5.3.1     | Enabling Parallelism                                             | 126 |  |  |

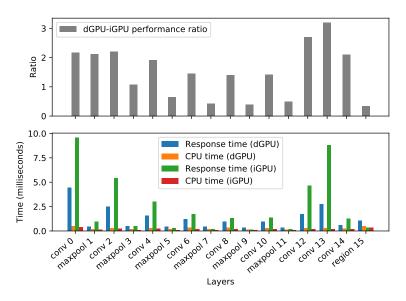

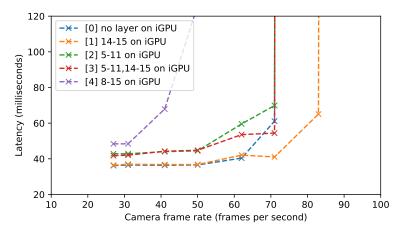

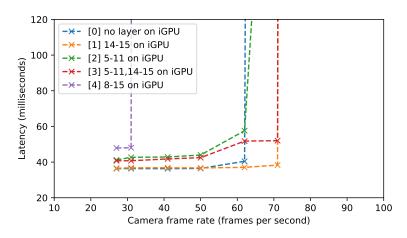

|        | 5.3.2     | Multi-GPU Execution                                              | 130 |  |  |

|        | 5.3.3     | Accelerating Multiple Streams with Multi-Camera Composite Images | 131 |  |  |

|        | 5.3.4     | Avoiding Implicit Synchronization                                | 132 |  |  |

| 5.4    | Evalua    | ation                                                            | 132 |  |  |

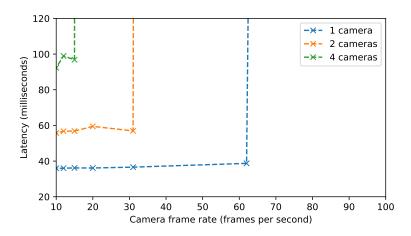

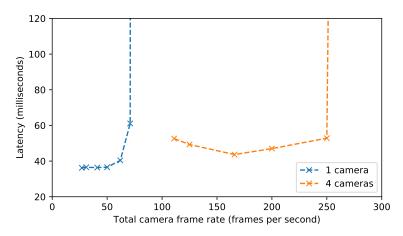

|        | 5.4.1     | How Many Cameras can be Supported?                               | 133 |  |  |

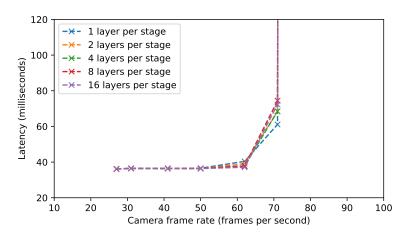

|        | 5.4.2     | Can Our CNN Implementations Be Better Configured?                | 135 |  |  |

|        | 5.4.3     | Are Multi-Camera Composite Images Effective?                     | 139 |  |  |

| 5.5    | Chapte    | er Summary                                                       | 142 |  |  |

| Chapte | r 6: Case | e Study                                                          | 144 |  |  |

| 6.1    | OpenV     | VX Graph Scheduling                                              | 146 |  |  |

|        | 6.1.1     | Coarse-Grained OpenVX Graph Scheduling                           | 146 |  |  |

|        | 6.1.2     | Fine-Grained OpenVX Graph Scheduling                             | 146 |  |  |

| 6.2    | Case S    | Study                                                            | 151 |  |  |

|        | 6.2.1     | Experimental Evaluation                                          | 151 |  |  |

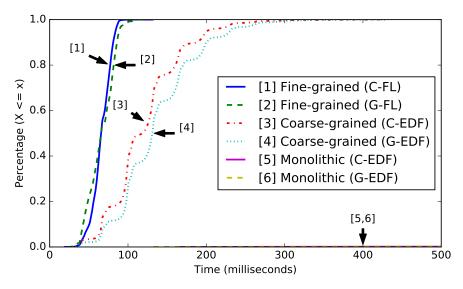

|         | 6.2.2 Results      |     |

|---------|--------------------|-----|

| 6.3     | Chapter Summary    | 156 |

| Chapter | 7: Conclusion      |     |

| 7.1     | Summary of Results | 158 |

| 7.2     | Acknowledgements   | 160 |

| 7.3     | Future Work        |     |

| 7.4     | Closing Remarks    |     |

| BIBLIO  | OGR APHY           | 164 |

## LIST OF TABLES

| 2.1 | Description of functions used in HOG pedestrian detection example                  | 34  |

|-----|------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison between accelerators.                                                   | 39  |

| 2.3 | Comparison between NVIDIA GPU architecture generations                             | 41  |

| 2.4 | Real-time task model notation.                                                     | 57  |

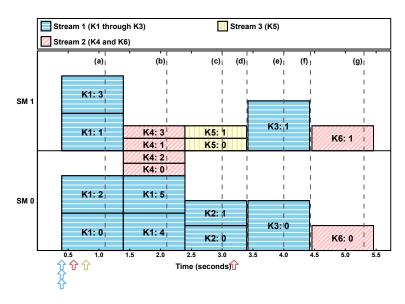

| 3.1 | Details of kernels used in the experiment in Figure 3.1                            | 73  |

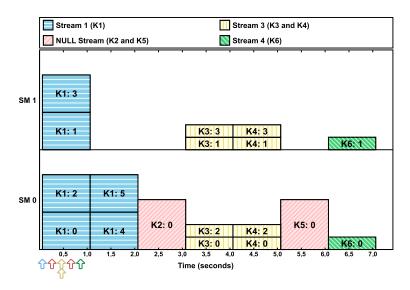

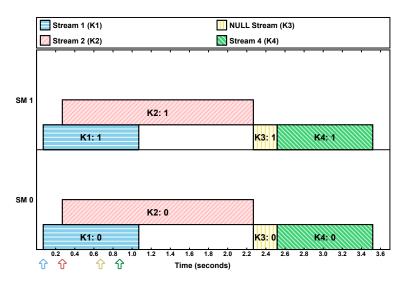

| 3.2 | Details of kernels used in the NULL-stream scheduling experiment in Figure 3.3     | 79  |

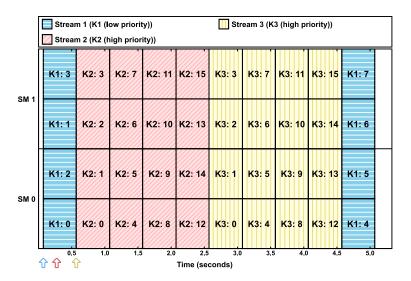

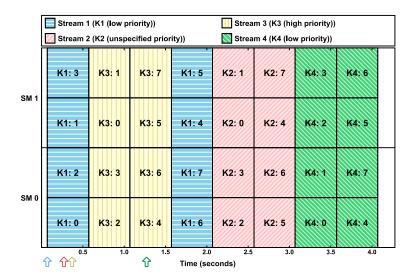

| 3.3 | Details of kernels used in the priority-stream scheduling experiment in Figure 3.4 | 81  |

| 3.4 | Details of kernels used in the priority-stream scheduling experiment in Figure 3.5 | 82  |

| 3.5 | Details of kernels used in the priority-stream scheduling experiment in Figure 3.6 | 83  |

| 3.6 | Abbreviations used for our four experimental scenarios                             | 94  |

| 3.7 | Per-frame response time data (in milliseconds) of VisionWorks samples              | 95  |

| 3.8 | Observed vs. documented synchronization sources in CUDA                            | 100 |

| 5.1 | Specifications of the PX2 iGPU and dGPU.                                           | 124 |

| 5.2 | CPU and memory usage.                                                              | 138 |

| 5.3 | GPU assignment strategies.                                                         | 139 |

| 5.4 | mAPs for full-size and composite tests with PASCAL VOC dataset.                    | 141 |

| 5.5 | mAPs of object classes relevant to autonomous driving                              | 141 |

| 6.1 | Analytical and observed response times                                             | 154 |

# LIST OF FIGURES

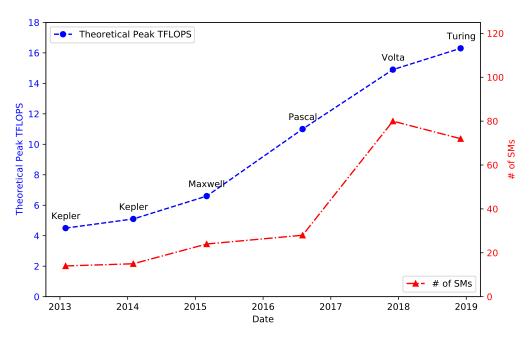

| 1.1  | Trends in NVIDIA GPU performance and the number of SMs over generations                                          | 5  |

|------|------------------------------------------------------------------------------------------------------------------|----|

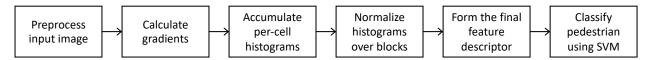

| 2.1  | HOG pedestrian detection pipeline.                                                                               | 26 |

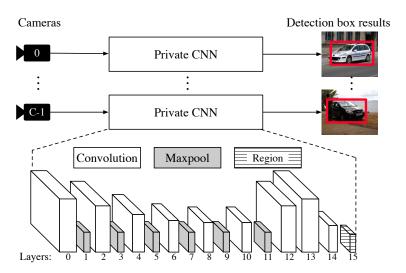

| 2.2  | Traditional camera processing setup and the Tiny YOLOv2 network architecture.                                    | 28 |

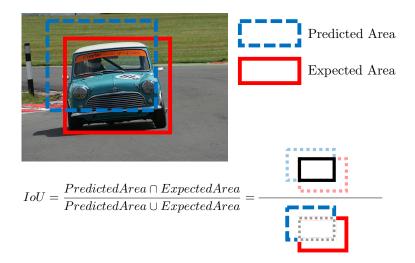

| 2.3  | IoU illustrated with an image example from PASCAL VOC dataset (Everingham et al., 2010)                          | 29 |

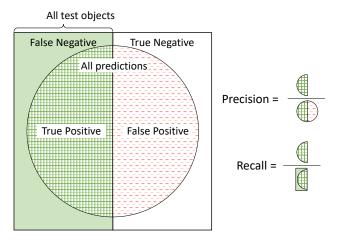

| 2.4  | Precision and recall                                                                                             | 30 |

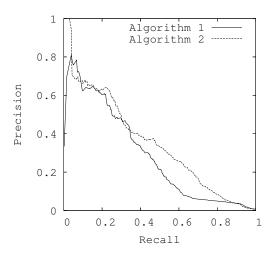

| 2.5  | Example Precision-Recall curves (Davis and Goadrich, 2006)                                                       | 31 |

| 2.6  | OpenVX graph example: pedestrian detection using HOG                                                             | 34 |

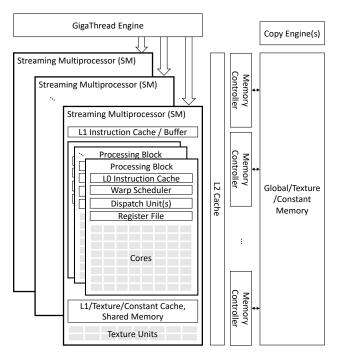

| 2.7  | NVIDIA GPU architecture                                                                                          | 40 |

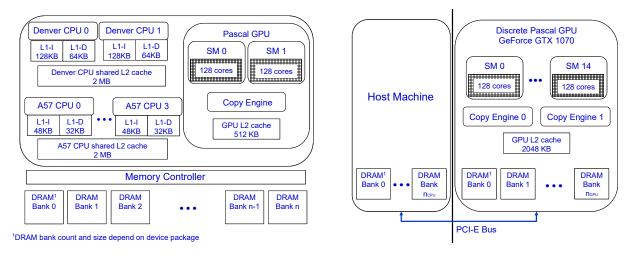

| 2.8  | Jetson TX2 Architecture (left) and GeForce GTX 1070 Architecture (right)                                         | 42 |

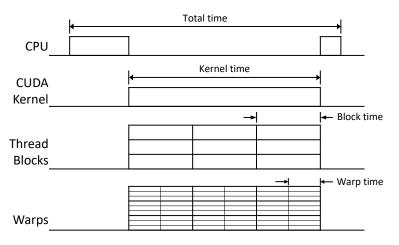

| 2.9  | Disgram illustrating the relation between CUDA programs, kernels, thread blocks, and warps                       | 45 |

| 3.1  | Basic GPU scheduling experiment.                                                                                 | 72 |

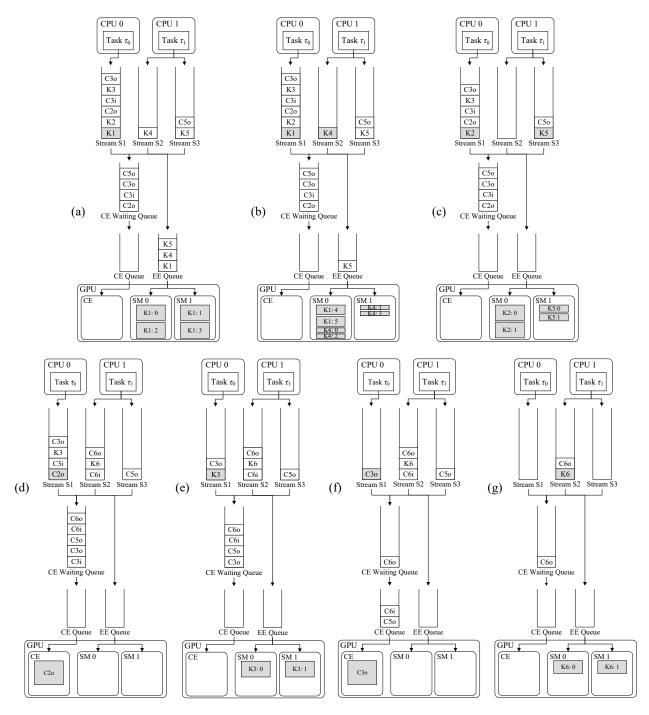

| 3.2  | Detailed state information at various time points in Figure 3.1                                                  | 74 |

| 3.3  | NULL stream scheduling experiment.                                                                               | 80 |

| 3.4  | Experiment showing starvation of a priority-low stream.                                                          | 81 |

| 3.5  | Experiment demonstrating two actual priority levels.                                                             | 82 |

| 3.6  | Experiment with both priorities and resource blocking.                                                           | 83 |

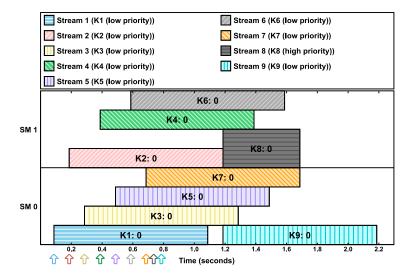

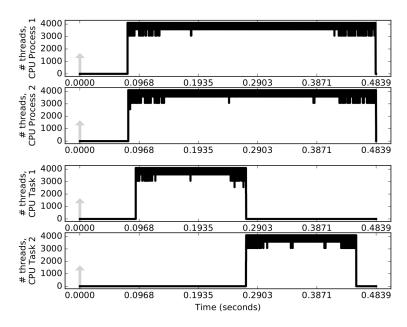

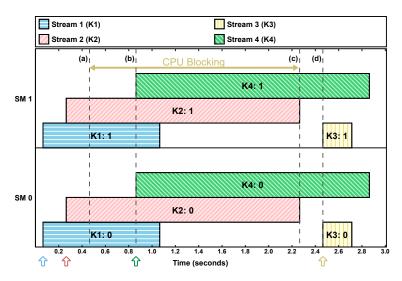

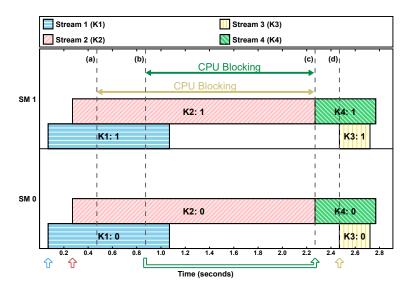

| 3.7  | Timelines contrasting kernels issued from processes (different address spaces) vs. tasks (shared address space). | 85 |

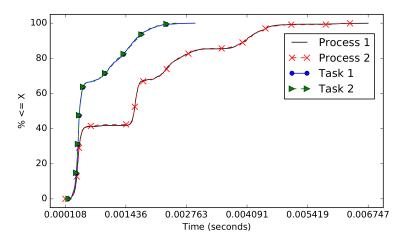

| 3.8  | CDFs contrasting blocks times from processes vs. tasks                                                           | 86 |

| 3.9  | Explicit synchronization requested before K3, observed on the Jetson TX2                                         | 88 |

| 3.10 | Implicit synchronization caused by launching kernel K3 in the NULL stream                                        | 90 |

| 3.11 | Implicit synchronization causing additional CPU blocking due to cudaFree                                         | 91 |

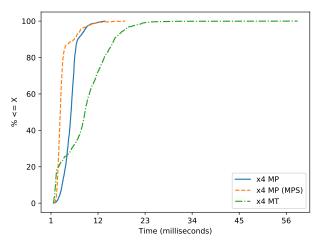

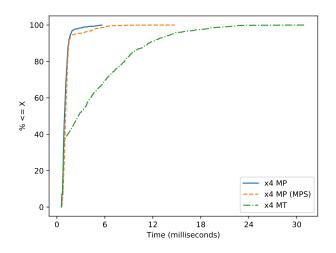

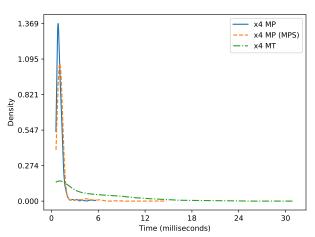

| 3.12 | Per-frame response time CDFs for Hough.                                                                          | 96 |

| 3.13 | Per-frame response time KDEs for Hough.                                                                          | 96 |

| 3.14 | Per-frame response time CDFs for Feature Tracking                                                                | 96 |

| 3.15 | Per-frame response time KDEs for Feature Tracking.                                                               | 96 |

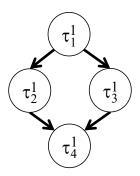

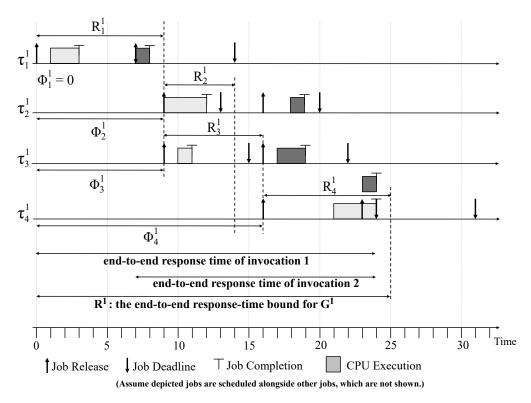

| 4.1  | $\mathrm{DAG}\ G^1$                                                                        | . 104 |

|------|--------------------------------------------------------------------------------------------|-------|

| 4.2  | Example schedule of the tasks in $G^1$ in Figure 4.1                                       | . 106 |

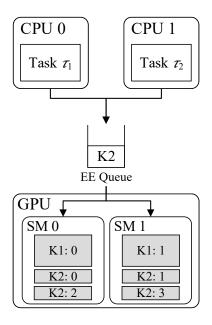

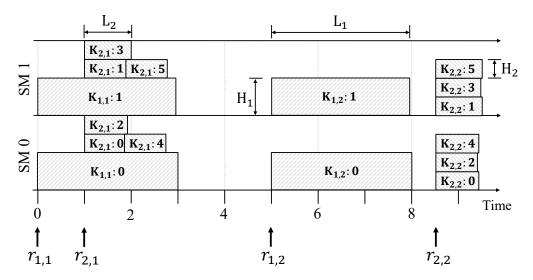

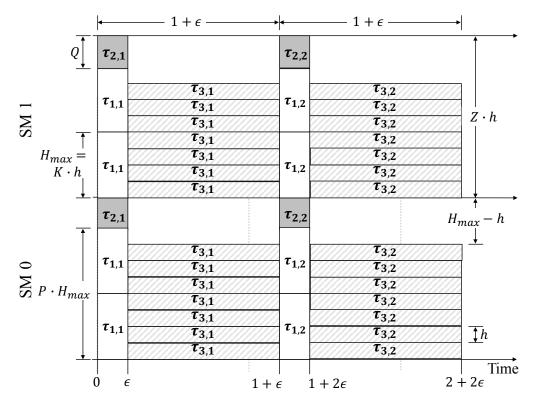

| 4.3  | GPU scheduling; kernel Kk's bth block is Kk:b.                                             | . 108 |

| 4.4  | A possible schedule corresponding to Figure 4.3.                                           | . 110 |

| 4.5  | Unbounded response time using per-task streams                                             | . 112 |

| 4.6  | Unbounded response time using per-job streams                                              | . 113 |

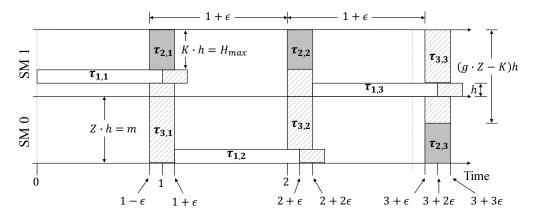

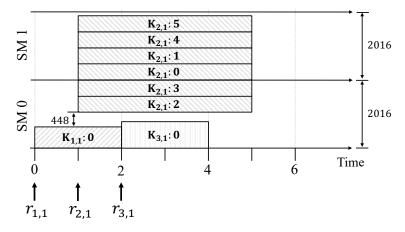

| 4.7  | A possible schedule for Example 4.4 with $m = 2016$                                        | . 118 |

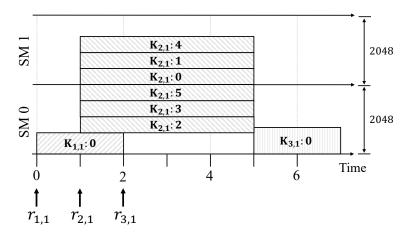

| 4.8  | A possible schedule for Example 4.4 with $m = 2048$                                        | . 118 |

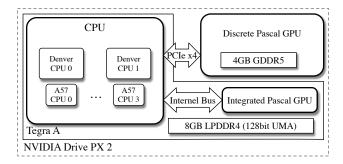

| 5.1  | NVIDIA DRIVE PX2 architecture.                                                             | . 124 |

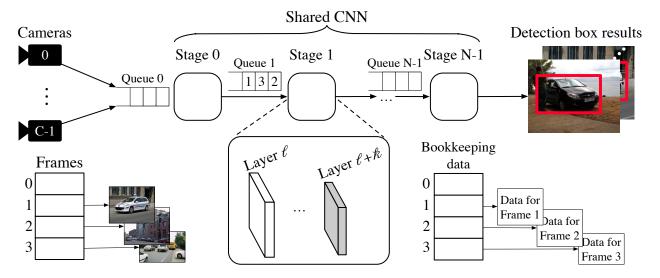

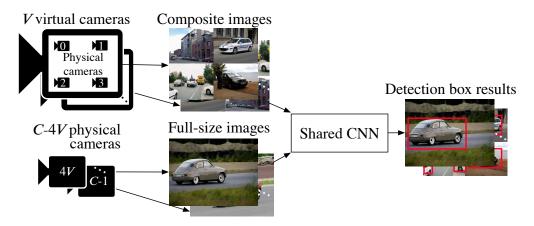

| 5.2  | Sharing one CNN for multiple cameras                                                       | . 127 |

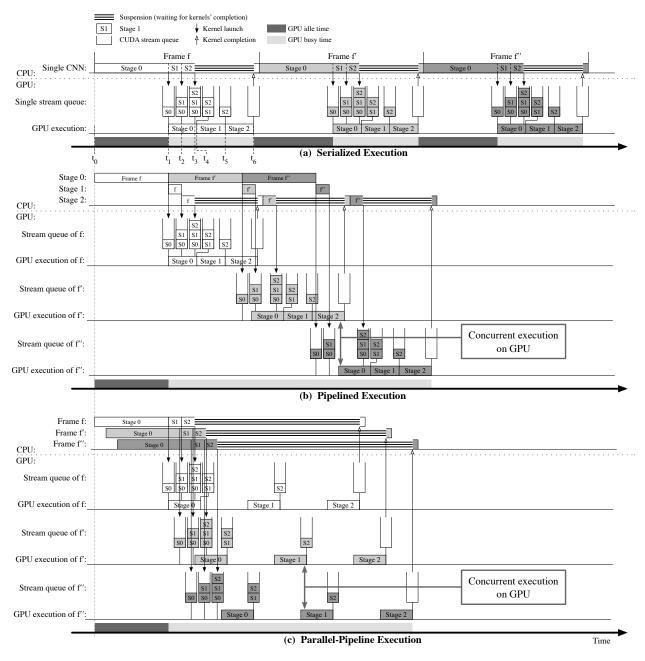

| 5.3  | Scheduling of Serial, Pipeline, and Parallel                                               | . 128 |

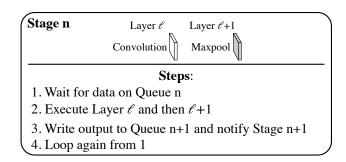

| 5.4  | Stage representation for pipelined execution model                                         | . 129 |

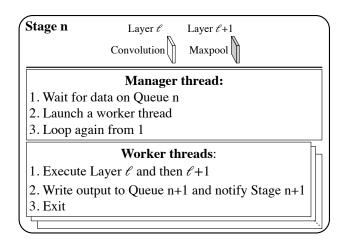

| 5.5  | Stage representation for parallel-pipeline execution model                                 | . 130 |

| 5.6  | CNN extended for multi-camera composite images.                                            | . 131 |

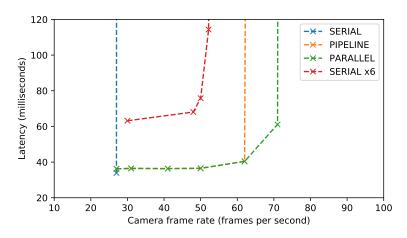

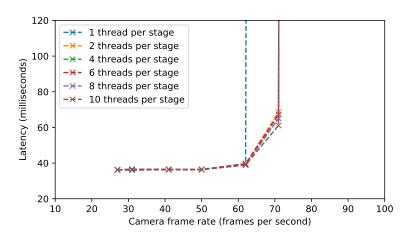

| 5.7  | Latency of SERIAL, PIPELINE, and PARALLEL YOLO.                                            | . 134 |

| 5.8  | PARALLEL YOLO latency with different numbers of cameras.                                   | . 135 |

| 5.9  | PARALLEL YOLO latency with different granularities (number of layers per stage)            | . 136 |

| 5.10 | PARALLEL YOLO latency with different numbers of threads                                    | . 137 |

| 5.11 | Per-layer execution times.                                                                 | . 138 |

| 5.12 | PARALLEL YOLO latency with different GPU assignments.                                      | . 139 |

| 5.13 | PIPELINE YOLO latency with different GPU assignments.                                      | . 140 |

| 5.14 | PARALLEL YOLO latency with multi-camera-image processing and different numbers of cameras  | . 142 |

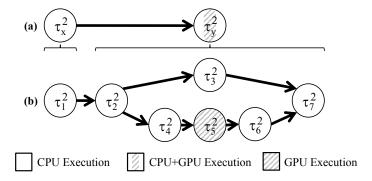

| 6.1  | (a) Coarse- and (b) fine-grained representations of the same DAG $G^2$                     | . 147 |

| 6.2  | Example schedules of the tasks corresponding to the DAG-based tasks in $G^2$ in Figure 6.1 | . 149 |

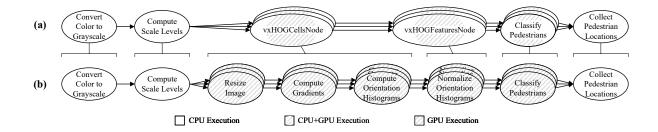

| 6.3  | (a) Monolithic/coarse-grained and (b) fine-grained HOG DAGs                                | . 151 |

| 6.4  | CDFs of response times for varying DAG granularity.                                        | . 155 |

#### LIST OF ABBREVIATIONS

ACC Adaptive Cruise Control

ADAS Advanced Driver Assist System

AI Artificial Intelligence

AP Average Precision

ASICs Application-Specific Integrated Circuits

BAND Bandwidth-Aware Non-preemptive Device

CAN Controller Area Network

CDF Cumulative Distribution Function

CE Copy Engine

C-FL Clustered Fair-Lateness

CKE Concurrent Kernel Execution

CNN Convolutional Neural Network

CPU Central Processing Unit

DAG Directed Acyclic Graph

DARPA Defense Advanced Research Projects Agency

DNN Deep Neural Network

DPM Deformable Part-based Model

DRAM Dynamic Random-Access Memory

DSPLIB DSP LIBrary

DSP Digital Signal Processor

EDF Earliest-Deadline-First

EE Execution Engine

FCW Forward Collision Warning

FFT Fast Fourier Transform

FIFO First-In-First-Out

FP Fixed-Priority

FPGA Field Programmable Gate Arrays

FPPI False Positive Per Image

FPPW False Positive Per Window

FPS Frames Per Second

G-EDF Global Earliest-Deadline-First

GEL G-EDF-like

G-FIFO Global First-In-First-Out

G-FL Global Fair-Lateness

GPGPU General-Purpose Graphics Processing Unit

GPS Global Positioning System

GPU Graphics Processing Unit

GVA Guest Virtual Address

HDL Hardware Description Language

HOG Histogram of Oriented Gradients

HPC High-Performance Computing

HRT Hard Real-Time

HSA Heterogeneous System Architecture

ILP Integer Linear Program

IMU Inertial Measurement Unit

IPC Inter-Process Communication

ISA Instruction Set Architecture

JLFP Job-Level Fixed-Priority

KDE Kernel Density Estimation

LDW Lane Departure Warning

LITMUS<sup>RT</sup> LInux Testbed for MUltiprocessor Scheduling in Real-Time systems

LKAS Lane-Keeping Assistance Systems

LKM Loadable Kernel Module

LRU Least Recently Used

MB Mega Bytes

MMIO Memory-Mapped Input/Output

MPA Machine Physical Address

MPH Miles Per Hour

MPS Multi-Process Service

NHTSA National Highway Traffic Safety Administration

NPP NVIDIA Performance Primitives

OS Operating System

PCA Principal Component Analysis

PCI Peripheral Component Interconnect

PGM<sup>RT</sup> Processing Graph Methods for Real-Time

PKM Preemptive Kernel Model

PREM PRedictable Execution Model

PR Precision-Recall

PTX Parallel Thread Execution

PT Persistent Threads

RL Reinforcement Learning

RNN Recurrent Neural Network

RPC Remote Procedure Call

RTA Response-Time Analysis

RTOS Real-Time Operating System

SAE Society of Automotive Engineers

SIFT Scale-Invariant Feature Transform

SIMD Single-Instruction Multi-Data

SIMT Single-Instruction Multi-Thread

SLAM Simultaneous Location And Mapping

SM Streaming Multiprocessor

SPT Shadow Page Table

SRT Soft Real-Time

SSD Single-Shot multibox Detector

SVM Support Vector Machine

SWaP Size, Weight, and Power

TLB Translation Lookaside Buffer

TPN Timed Petri Nets

VOC Visual Object Classes

WCET Worst-Case Execution-Time

#### **CHAPTER 1: INTRODUCTION**

After being envisioned for decades, autonomous vehicles seem to be just over the horizon. We expect this innovation to reduce traffic accidents, save lives, mobilize those with disabilities for driving, protect the environment, liberate workers from commuting, and ultimately transform how our cities function. More importantly, we expect these enhancements to be achieved *safely* because the fundamental goal of saving lives is rooted in the capabilities of technology. The safety requirements for autonomous vehicles focus around executing appropriate driving decisions in real time, imposing the requirements of both *logical correctness* and *temporal correctness*. Satisfying such safety requirements is challenging because of the complex software components and hardware platforms that underpin autonomous-driving systems.

One primary software component in an autonomous-driving system is the perception system that semantically senses and understands the surrounding environment. A common approach used in the perception system is vision-based sensing because compared to lidars and radars, cameras are less expensive and uniquely capable of perceiving colors and textures. With a proliferation of computer-vision research in the literature, many state-of-the-art features have been applied in today's autonomous vehicle prototypes.

However, existing computer-vision frameworks often fail to provide enough inference performance, not to mention that such performance is unpredictable, so the requirement for temporal correctness remains to be established. Despite the goal of improving performance and ensuring predictability, any induced accuracy loss must be tolerable. We investigate solutions for providing sufficient and predictable performance in the use of the underlying hardware accelerator with a focus on graphics processing units (GPUs).

GPUs are commonly used for accelerating computer-vision applications, as they provide the massive parallelism needed by these types of applications, which process millions of pixels per image streaming from multiple video sources to provide full coverage of a vehicle's surroundings. With applications providing disparate functionalities and advancements of GPUs offering more processing capacity, the incentives to share GPUs among multiple applications by enabling predictable simultaneous execution have grown. Also, any unnecessary idleness incurred by CPU-GPU interactions in existing computer-vision frameworks should be minimized for better performance.

Motivated by these challenges, our research considers how GPUs can be shared across multiple applications to improve throughput with bounded response times and high per-stream accuracy. In the following section, we provide the details of our application focus on computer vision to enable safe autonomous driving.

## 1.1 Computer Vision in Autonomous Driving

With the development in autonomous driving ongoing for decades, the latest research that spurred industrial production of autonomous vehicles came from the series of Grand and Urban challenges sponsored by the Defense Advanced Research Projects Agency (DARPA) (Buehler *et al.*, 2007, 2009). Today, semi-autonomous advanced driver assist systems (ADASs) are commonly available in high-end mass-market vehicles. Although fully autonomous driving is yet to be realized, promising progress has been seen in many industrial prototypes, such as Waymo's fleet of cars, which have completed over 20 million test miles since 2009, achieving an average of 11,017 miles between disengagements<sup>1</sup> in 2018 (Waymo, 2020; Crowe, 2019b).

Existing work on autonomous-driving systems can be classified as either a learning-based end-to-end system, considered a black-box that receives sensory inputs and generates the final control commands, or a modular system that is comprised of sub-components, which is the choice applied in many systems participating in the DARPA challenges and industrial prototypes. As the class focused on here, these systems are modular autonomous-driving platforms consisting of sensors, perception systems, and planning and control systems. These components capture the environment, distill semantic information, and plan routes while controlling the vehicle, respectively.

Every component is positioned along a critical path between sensing to control, and is subject to time constraints that are just as important as producing accurate results. Vehicles currently operating on the road have been assessed by safety certification authorities, *e.g.*, the National Highway Traffic Safety Administration (NHTSA), that follow functional safety standards, such as ISO 26262 (ISO, 2011). Although these safety standards are yet to be adopted for autonomous vehicles, the process for safety certification will be crucial to making these become trusted modes of transportation for daily use. The urgency in achieving certified autonomous driving is exemplified by recent interest in "real-time" computer vision.

<sup>&</sup>lt;sup>1</sup>While this metric is limited, it remains the only one used for measuring technological progress in autonomous driving. Disengagement occurs when the human driver must retake control of the vehicle during situations that the autonomous system is unable to handle.

Among common sensor types—cameras, lidars, and radars—cameras are the least expensive, and they preserve features such as color and texture that other sensors cannot. Therefore, realizing full autonomy in vehicles at a reasonable cost is expected to entail deploying computer-vision algorithms. As a result, there has been intense recent interest in real-time computer vision. Unfortunately, *in interpreting the term "real time," a significant disconnect exists* between computer-vision researchers and automotive system engineers. For the former, "real time" suggests *real fast* processing on a dedicated high-end hardware platform, and for the latter, it means *predictable*, notably on more impoverished embedded hardware that must be shared by many disparate computations. The "predictable" interpretation of real time is based on automobiles being safety-critical systems. When certifying such a system, showing that certain computations *predictably occur within specified time bounds* is more important than "real fast" performance under ideal conditions.

This disconnect between real-fast computer vision and real-time safety has led to unfortunate consequences. Several highly publicized accidents involving semi-autonomous and fully autonomous vehicles operating on open roads resulted in fatalities. Post-crash analyses of these incidents revealed a critical trade-off between time and accuracy at the nexus of computer vision and real time. As one analyst concluded, "public authorities should ... ensure that self-driving cars have the capacity to process all the needed information to adopt decisions *in real time*" (emphasis added) (Renda, 2018).

This observation suggests the need for *real-time certification*, which may result in the real-fast vs. real-time computer vision disconnect becoming more problematic. Today, computer-vision-based features are largely provided in settings where the driver is assumed to be able to retake full control of the vehicle. As such, these features are not yet subject to strict certification requirements. Moving forward, however, increased autonomy will come to mass-market vehicles, and the line between semi-autonomy and full autonomy will be crossed eventually, making strict certification critical. A challenge will exist for certifying computer-vision applications that are merely "real fast," as these will be difficult to accomplish, if not impossible.

On the other hand, certifiable computer-vision implementations should not diminish throughput performance, although sometimes a trade-off must be made. The throughput requirements of an autonomous system are determined by the necessity of ensuring adequate coverage and redundancy (for safety) that can be offered by a large quantity and diversity of cameras. A typical configuration in experimental automated-driving vehicles includes ten or more cameras that cover different fields-of-view, orientations, and near and far ranges. Each camera generates a stream of images at rates of 10 to 40 frames per second (FPS) depending on its function (*e.g.*, lower rates for side-facing cameras, higher rates for forward-facing ones). All these

image streams must be processed simultaneously by the onboard computer-vision applications, making sufficient throughput performance essential to support the processing of multiple data streams that fully cover a vehicle's surroundings.

To address these challenging problems of enabling real-time computer vision at the application level, achieving real-time performance and high utilization of the underlying hardware platform is important. Next, we discuss a key enabler for accelerating computer vision, the graphics processing unit (GPU).

#### 1.2 Graphics Processing Units

GPUs evolved from a fixed-function, special-purpose hardware pipeline for graphics rendering into a programmable general-purpose hardware platform, as the term general-purpose GPU (GPGPU) was coined (Owens *et al.*, 2008). GPUs became a key technological enabler that advanced the techniques of deep learning, which have existed for decades but have started growing in use recently. The massive parallelism enabled by the architecture and programming model of GPUs reduces the training processing time for deep neural networks (DNNs) and makes the inference process nearly instantaneous for real-world applications.

Taking NVIDIA GPUs as an example, rendering hardware pipelines are replaced with programmable units called CUDA (Compute Unified Device Architecture) cores that are organized into streaming multiprocessors (SMs). Each SM supports a large number of GPU threads on the fly, while a subset of these threads can be executed simultaneously. These numbers can vary across GPU generations, so are generation-specific parameters. In contrast, the programming model remains consistent over generations.

Without discussing the programming model in more detail here, which we do in Section 2.3.3, we briefly describe the basic process of a GPU program. A GPU program is launched from a CPU (or host) process as follows: (i) allocate memory for the GPU to use, (ii) copy the input data from CPU memory to GPU memory, (iii) execute a GPU program, called a *kernel*, to process data, (iv) copy the results from GPU memory back to CPU memory, and (v) free unneeded memory. A GPU kernel is comprised of these GPU threads, which are organized into a grid of blocks, and also accesses different types of memory, including registers, shared memory, and global memory. To manage concurrent kernel execution and algorithmic serialization, kernels are submitted to CUDA streams, and those from the same stream are serialized by submission order, whereas kernels from different streams can execute concurrently.

<sup>&</sup>lt;sup>2</sup>This terminology is not to be confused with an operating system (OS) kernel.

Figure 1.1: Trends in NVIDIA GPU performance and the number of SMs over generations. Each pair of a circle and a triangle data point that share the same date represent one NVIDIA TITAN GPU, annotated with its architecture code name; the circle corresponds to the performance metric on the left, and the triangle corresponds to the number of SMs on the right.

The concurrency between kernel executions becomes more important as GPUs become increasingly powerful, and the trend of increasing performance in TFLOPS (tera floating point operations per second) is illustrated in Figure 1.1. In this figure, each data point represents an NVIDIA flagship TITAN GPU product,<sup>3</sup> with its launch date, theoretical peak performance on the left, and the number of SMs on the right. These upward trends indicate the rapidly increasing performance of the GPU and its capacity to support additional on-the-fly GPU threads. Note that each SM supports 2,048 threads across all GPU architecture generations. Although from the Volta to Turing architectures, the number of SMs decreased, the performance continued to climb because the amount of global memory doubled, leading to more opportunities for concurrency among memory-intensive GPU applications.

Similar trends are followed by product lines of embedded GPUs, which are comparatively impoverished. Nonetheless, it further emphasizes the necessity of sharing GPUs because processing cycles should not be wasted, as their use in embedded environments is more sensitive to the size, weight, power, and cost issues. Even though a GPU kernel utilizes all resources most of the time during execution, it may leave the GPU partially idle once its threads start exiting.

<sup>&</sup>lt;sup>3</sup>Because the model names are similar, we annotate the data points with the architecture code name, and the points with the same date represent the same products.

While sharing GPUs is important, the process incurs challenges for real-time systems. The design principle of GPUs is throughput-oriented, given their origin of accelerating graphics rendering, only later being extended to the application of general-purpose computation, such as neural-network training. The former use case pursues "real-fast" performance, such as generating 30 frames per second for animation rendering, while the latter bears the throughput of finishing the training process with a large number of images over hours or even days. Guided by this performance requirement, the design of GPUs often sacrifices real-time predictability in favor of throughput. For example, GPU kernels from multiple processes are executed in a multi-programmed manner, resulting in unpredictable performance that depends on other co-scheduled workloads (Otterness *et al.*, 2017b; Capodieci *et al.*, 2018). Other forms of execution apply different scheduling rules, such as executing kernels from multiple threads in the same address space simultaneously when possible. However, these scheduling rules are undisclosed, including the condition of concurrency and execution order.

Closed-source software stacks and unknown hardware details have hindered research using NVIDIA GPUs in many aspects. Given their need for high efficiency in utilizing the hardware platform, embedded systems often require internal and low-level software and hardware information, which must be obtained through reverse engineering efforts for NVIDIA GPUs. The findings obtained in this way, such as scheduling rules, are rarely perfectly accurate due to the possible existence of edge cases. Even though they can be reaffirmed through large-scale experiments, they remain vulnerable to changes from product updates, so they are limited to short-term applicability. While we encourage openness that eliminates these issues, we perform reverse engineering to move forward, as this information is essential for sharing GPUs in real-time systems, as discussed below.

## 1.3 Real-Time Systems and GPU Scheduling

We mentioned the required temporal correctness and predictable performance of real-time autonomousdriving systems. To achieve them, we require a solid real-time analysis foundation upon which we can derive real-time guarantees. Although this has been well-studied for CPUs, little work is available for GPU scheduling, especially with shared GPUs. In this section, we first review several basic real-time concepts, which are introduced in greater detail in the Chapter 2. Then, we motivate the necessity of a novel task model and analysis for shared GPUs. Most real-time applications are embodied in recurrent *tasks*, such as the repetitive capture of new images. A classic abstraction for recurrent tasks is the *sporadic task model* (Mok, 1983), which is applied in this dissertation. A *sporadic task* repeatedly releases *jobs* with a minimum time separation called a *period*, and these jobs are subjected to finishing before their *deadlines*. Each task has a *utilization* that represents the fraction of processor capacity sufficient for meeting its timing constraints. With the timing parameters of the period, deadline, and utilization, a task model can express the timing requirements of a *task system* (or *task set*) that is comprised of a set of tasks.

The sporadic task model is analyzed to validate temporal correctness, *i.e.*, to determine if a task system is *schedulable*—if it always satisfies all timing constraints when scheduled by a particular scheduler. These timing constraints are categorized as hard real time (HRT) or soft real time (SRT), where the former requires all deadlines to be met, and the latter tolerates deadline misses. Various definitions of SRT exist, and we focus on one that requires a bounded response time, which is the time difference between the finish time and release time of a job. The concept of *schedulability* is a core aspect of real-time analysis, as an important goal of real-time analysis is to provide *schedulability tests* that determine if a task system is schedulable. These types of tests are specific to the scheduling algorithm applied.

For a task system to be schedulable, its *total utilization* cannot exceed the entire capacity of a platform. However, a task system with a total utilization less than the capacity of the platform may still not be schedulable due to *capacity loss* incurred by non-optimal scheduling algorithms or real-workd overheads.

Algorithmic non-optimality-induced capacity loss, or algorithmic capacity loss, is incurred by all previous work on schedulability analysis for real-time GPUs. This issue is partly due to the GPU programming model and the native low-level scheduler available on GPU hardware. We demonstrate this inevitable capacity loss for the current NVIDIA GPUs in Section 4.2.3, and it is more severe when GPUs are managed as resources (Elliott *et al.*, 2013) or limited to exclusive access (Capodieci *et al.*, 2018). Specifically, with resource-based management (Elliott *et al.*, 2013), executing GPU code introduces *task suspensions*, which are typically handled with *suspension-oblivious analysis* (Brandenburg and Anderson, 2010) that analytically views the suspension time as CPU computation time, resulting in significant processing-capacity loss.

Additionally, these works have to intervene with respect to GPU kernel launches at runtime, at the driver or hypervisor levels, to enforce customized scheduling policies. In contrast, we tackle the problem of deriving schedulability analysis differently by aiming for the native NVIDIA GPU scheduling rules, which must first be revealed through reverse engineering because we can only demonstrate the predictability of a *known*

scheduler, *i.e.*, one that manages GPU kernels that share GPUs. Such predictability then must be proved through real-time schedulability analysis that is conducted on models, *e.g.*, the sporadic task model, just as with CPUs. However, the difference from the architecture and programming model of CPUs necessitates a new task model for GPU tasks. From these goals, we present our thesis statement in the following.

#### 1.4 Thesis Statement

Computer-vision applications in autonomous-driving systems are subjected to real-time requirements and demand high-throughput performance. Existing computer-vision frameworks that lack real-time concepts and underutilize the underlying hardware platforms must be reconsidered. We exploit pipelining and parallelism in GPU-accelerated computer vision for improved throughput with bounded response times and good accuracy.

The real-time community has investigated the benefits of GPUs. However, prior schedulability-analysis research was subject to algorithmic capacity loss in the scheduling controls through middleware/OS-level management. We remove this management layer and target the native GPU scheduler. Furthermore, we enable GPU sharing to improve resource utilization and derive real-time schedulability analysis based upon the revealed GPU scheduling rules to guarantee predictable performance for tasks that share GPUs.

This usage of shared GPUs is applied to our improved computer-vision framework that supports the thesis of this dissertation as follows:

Capacity loss in GPU-using real-time task systems can be lessened through sharing GPUs. Such sharing can be guaranteed with bounded response times. Furthermore, throughput can be improved without compromising such guarantees by exploiting pipelining and parallelism in real-time tasks. These real-time guarantees of tasks on shared GPUs are enabled with a new model for GPU execution and corresponding schedulability analysis.

#### 1.5 Contributions

The contributions of this dissertation are briefly summarized in the following subsetions, which outline our efforts towards producing a study of NVIDIA GPUs, a model of GPU execution, a response-time bound analysis, a computer-vision framework, and a case study.

## 1.5.1 A Study of NVIDIA GPUs beyond Official Documentation

To share GPUs and derive a schedulability analysis for GPU tasks managed by the native NVIDIA GPU scheduler, the first step is to determine the details of the scheduler. In addition to undisclosed scheduling details, interactions between CPUs and GPUs, such as kernel launches, suffer from problematic synchronization issues that behave differently with the various ways to execute GPU tasks. We examine these GPU execution approaches to determine which is appropriate for executing real-time tasks.

As discussed above, the public documents from NVIDIA are incomplete in describing GPU scheduling details, and the software stack is closed-source. For the goal of sharing GPUs and enabling simultaneous execution, the GPU scheduling rules must be identified. Specific details to be resolved include the scheduling order of GPU kernels from multiple CUDA streams, how resources in GPUs are allocated to these GPU kernels that impact GPU scheduling, and how other special programming features influence the scheduling. Taking a team effort,<sup>4</sup> these questions are answered comprehensively through reverse engineering and are included in our study results in Chapter 3.

In addition to the scheduling rules, we expose pitfalls pertaining to the synchronization between CPUs and GPUs. For any task consisting of a combination of CPU and GPU computations, synchronization points exist (*e.g.*, a CPU program must wait until a GPU produces a result). Synchronization inherently leads to blocking terms in scheduling analysis, and we realized that synchronization blocking occurring in the GPU task is not straightforward. Further, some forms of synchronization lead to a significant capacity loss for both CPUs and GPUs. We constructed experiments that expose these synchronization effects and describe them in Chapter 3 along with pitfalls the unaware programmer may encounter.

We realized a fundamental trade-off exists for designing real-time tasks that use a GPU. A conventional choice is to write and execute the task program as an operating system (OS) process in its own non-shared address space that provides cross-task memory isolation. If this choice is used, however, the NVIDIA GPU programming environment does not permit concurrent computations on the GPU, even if sufficient resources are available. Depending on how GPU programs are organized and written, this can lead to capacity loss on the GPU. An alternate choice is to write and execute a task as a schedulable thread that shares a process address space with other task threads. While cross-task memory isolation is lost, the GPU programming

<sup>&</sup>lt;sup>4</sup>Tanya Amert, Nathan Otterness, and I collaboratively published a series papers investigating NVIDIA GPUs. Our individual contributions will be stated in Chapter 3.

environment provides mechanisms that allow concurrent computations on the GPU. NVIDIA provides a third option that leverages a middleware environment and is claimed to provide the best approach offering memory isolation and enabled concurrency. We performed a case study using exemplar computer-vision tasks in autonomous vehicles to evaluate these trade-off options, with our results and guidelines presented in Chapter 3.

## 1.5.2 A Model of GPU Execution

The above contributions provide a foundation for understanding GPUs, allowing us to further establish an abstract model of GPU execution. As with CPUs, a task model is created by considering the hardware architecture and programming model that reflect important aspects of GPUs. We extend the existing classic sporadic task model with additional parameters to describe GPU tasks, as presented in Chapter 4. These parameters are combined to express information about the parallel execution of tasks on GPUs.

As previously mentioned, NVIDIA GPUs employ scheduling rules that inherently sometimes cause unnecessary idleness of its processing units, implying a fundamental capacity loss when trying to ensure response-time bounds for GPU tasks. We express such a loss by providing a *total utilization bound* that is tight with a counterexample, a task system that has total utilization matching this bound but unbounded response times. We also demonstrate that capacity loss can be extreme if intra-task parallelism is forbidden. These two constraints of the utilization bound and intra-task parallelism establish a schedulability condition, and any task system satisfying this condition has a bounded response time.

## 1.5.3 A Response-Time Bound Analysis for Applications Sharing GPUs

Based on the revealed GPU scheduling rules and newly proposed model of GPU execution, we present the first response-time bounds for tasks that share GPUs. We apply similar analysis techniques proposed previously (Liu and Anderson, 2010; Devi and Anderson, 2005, 2008; Erickson *et al.*, 2014; Yang and Anderson, 2014a), including the directed-acyclic-graphs (DAGs) based analysis for heterogeneous platforms to derive end-to-end response-time bounds for our applications. These applications are decomposed into nodes of either CPU or GPU execution. For CPU nodes and tasks, we compute response-time bounds using existing analytical results for two real-time schedulers, the global earliest-deadline-first scheduler (G-EDF) and the global fair-lateness scheduler (G-FL), and for GPU nodes and tasks, we apply our analysis approach

from Chapter 4. The end-to-end response time is then calculated by accumulating the response-time bounds of the nodes along the critical path of the DAG.

## 1.5.4 A Computer-Vision Framework Providing Improved Throughput

As stated above, a fundamental challenge is to design a computer-vision framework that supports independent streams of images from multiple cameras. Because the hardware for embedded systems is constrained, enabling the effective utilization of every part of the system by computer-vision applications is essential.

We focus on the demanding computer-vision application needed by autonomous cars of the timely detection and recognition of objects in the surrounding environment using convolutional neural networks (CNNs). Many CNN implementations similarly seem to have limited throughput and poor GPU utilization. As explained further in Chapter 5, the root of the problem lies in viewing processing as a single run-through of all the processing layers comprising a CNN. However, in processing an image sequence from a single camera, each layer's processing of image i is independent of its processing of image i + 1. If the intermediate per-image data created at each layer is buffered and sequenced, there is no reason why successive images from the same camera cannot be processed in different layers concurrently.

This motivates us to consider the classic *pipelining* solution to sharing resources for increased throughput.<sup>5</sup> While pipelining offers the potential for greater parallelism, concurrent executions of the same layer on different images remain precluded. Allowing this may be of limited utility with one camera, but the potential exists for further increasing throughput substantially when processing streams of images from multiple independent cameras. This motivates us to extend pipelining by enabling each layer to execute in *parallel* on multiple images.

We altered the design of an existing CNN framework, called Darknet (Redmon, 2016), to enable pipelined execution, with parallel layer execution as an option, in the CNN. We also implemented a technique whereby different camera image streams are combined into a single image stream by combining separate per-camera images into a single composite image. This compositing technique can greatly increase throughput at the expense of some accuracy loss. We also enabled the balancing of GPU work across the platform's two GPUs,<sup>6</sup>

<sup>&</sup>lt;sup>5</sup>For example, instruction pipelining in processors can fully utilize data-path elements and increase throughput.

<sup>&</sup>lt;sup>6</sup>We use the NVIDIA DRIVE PX Parker AutoChauffeur, also called 'DRIVE PX2' or just 'PX2'.

which have differing processing capabilities. The CNN variants arising from these options and various other implementation details are discussed and evaluated in Chapter 5.

In summary, we provide an effective solution for a challenging problem faced by the autonomous-vehicle industry by designing CNN systems that provide the throughput, timeliness, and accuracy for computer-vision applications used in automated driving. By rethinking how the CNN is executed, we show that its throughput can improve by more than twofold with a minor increase in latency and no change in accuracy. We also show that throughput can be further improved with proper GPU load balancing. Finally, we show that the compositing technique can enable high throughputs of up to 250 FPS on the PX2. While this technique does incur some accuracy loss, we show that such loss can be mitigated by redoing the "training" CNNs require. We claim these results are sufficiently fundamental to guide CNN construction for similar automotive computer-vision applications on other frameworks or hardware.

## 1.5.5 A Case Study Evaluating Analytical and Empirical Real-Time Performance

We conduct a case study to evaluate analytical and empirical real-time performance with real-world applications by applying our analysis described previously. In particular, we address the limitation of coarse-grained scheduling from prior works on a computer-vision standard, OpenVX, which specifically targets computer vision in real-time embedded systems.

In prior work, our research group partially addressed the issues of enabling real-time OpenVX by proposing a new OpenVX variant in which individual graph nodes are treated as schedulable entities (Elliott *et al.*, 2015; Yang *et al.*, 2015). This variant allows greater parallelism and enables the computation of end-to-end graph response-time bounds. However, graph nodes remain high-level computer-vision functions, which is problematic for two reasons. First, these high-level nodes still execute sequentially, so some parallelism remains inhibited. Second, such a node will typically involve executing on both a CPU and a GPU. When a node accesses a GPU, it suspends from its assigned CPU. Suspensions are notoriously difficult to handle in schedulability analysis without inducing significant capacity loss, as discussed above. We show that these problems can be addressed through more fine-grained scheduling of OpenVX graphs.

We show how to transform the *coarse-grained* OpenVX graphs proposed in our group's prior work (Elliott *et al.*, 2015; Yang *et al.*, 2015) to *fine-grained* variants in which each node accesses either a CPU or a GPU, but not both. Such transformations eliminate the suspension-related analysis difficulties at the expense of minor overheads caused by the management of data sharing. Additionally, our transformation process

exposes opportunities for new potential parallelism at many levels. For example, because we decompose a coarse-grained OpenVX node into finer-grained schedulable entities, portions of such a node can now execute in parallel. Also, we allow not only successive invocations of the same graph to execute in parallel but even successive invocations of the same *node*.

For our case-study experiments conducted to assess the efficacy of our fine-grained graph-scheduling approach, we considered six instances of an OpenVX-implemented computer-vision application called HOG (histogram of oriented gradients), used in pedestrian detection, as scheduled on a multicore and GPU platform. These instances reflect a scenario where multiple camera feeds must be supported. We compared both analytical response-time bounds and observed response times for HOG under coarse-grained vs. fine-grained graph scheduling. We found that bounded response times could be guaranteed for all six camera feeds only under fine-grained scheduling based on our analysis. In fact, under coarse-grained scheduling, just one camera could (barely) be supported. We also found that the observed response times were substantially lower under fine-grained scheduling, and the overhead introduced by converting from coarse-grained to fine-grained had a modest impact. These results demonstrate the importance of enabling fine-grained scheduling in OpenVX if real time is *really* a first-class concern.

#### 1.6 Organization

For the remainder of this dissertation, we first provide a comprehensive background survey in Chapter 2 of autonomous driving research, applications of computer vision, GPU hardware platforms, and real-time systems research with a focus on real-time GPUs and DAG scheduling. Following this background of relevant work, we present our investigation of NVIDIA GPUs in Chapter 3 and a new model of GPU execution with schedulability analysis for real-time tasks that share GPUs in Chapter 4. We next describe our computer-vision framework design in Chapter 5, along with its experimental evaluation. Finally, we present a case study that evaluates the analytical and empirical real-time performance using our proposed analysis for GPU applications in Chapter 6. We conclude and discuss future work in Chapter 7.

#### **CHAPTER 2: BACKGROUND**

In this chapter, we survey related prior works and provide background information for this dissertation. We first review the development of autonomous-driving systems with a focus on computer-vision applications as our research context. We then describe the usage of GPUs versus other accelerators for computer-vision applications and the necessary fundamentals of GPUs, including the hardware architecture and GPU programming model. Lastly, we provide the fundamentals of real-time systems, and review the state-of-the-art literature on modeling and analyzing GPUs in real-time systems.

#### 2.1 Autonomous Driving

In this section, we first review state-of-the-art progress in autonomous-driving systems in both industry and academia. We then summarize typical system architectures of autonomous driving and explain each primary component. To motivate our research, we focus on explaining the safety- and timing-critical certification issues that relate to our work.

#### 2.1.1 State of the Art

Autonomous driving is expected to reduce traffic accidents and roadway fatalities, of which 94% are caused by human errors, as reported by the National Highway Traffic Safety Administration (NHTSA) in a recent technical report (National Highway Traffic Safety Administration, 2015). In addition to reducing vehicle crashes, autonomous driving can improve the mobility of people who have disabilities that relate to driving, benefit the environment by improving fuel efficiency and reducing emissions during congestion, give time back to commuters, and even reshape the layouts of our cities. With these benefits, it is projected that the nationwide adoption of autonomous driving could lead to nearly \$800 billion USD in annual social and economic benefits in America by 2050 (Montgomery *et al.*, 2018).

Although no industry players are even close to achieving fully-autonomous driving (Ackerman, 2017), semi-autonomous *advanced driver assist systems* (*ADASs*) are now commonly available in high-end mass-market vehicles; examples include Tesla Autopilot, Volvo Pilot Assist, Mercedes-Benz Drive Pilot, and

Cadillac Super Cruise (Hughes, 2017). These ADASs include functionalities such as adaptive cruise control (ACC), forward collision warnings (FCW), lane departure warnings (LDW), lane-keeping assistant systems (LKAS), and intelligent speed assistance (ISA). Each of these functionalities alone only qualifies as Level 1 automation, driver assistance, as defined in the taxonomy by the Society of Automotive Engineers (SAE) (SAE, 2018). When combined, these ADASs may enable Level 2, partial automation, which allows self-driving functionality in certain conditions such as on the highway, with the driver monitoring the environment and being ready to take over at any time as a fallback. With Level 0 denoting no automation, Levels 2 and below require the driver to monitor the environment at all times.

In contrast, Levels 3 and above encompass the classes of autonomous-vehicle (AV) systems. Level 3, conditional automation, allows the driver to focus on tasks other than driving, but requires the driver to be ready to quickly take over *upon request*. For instance, Audi's AI Traffic Jam Pilot achieves Level 3, at speeds below 37 miles per hour (MPH) (Ross, 2017).

Levels 4 and 5 require operating autonomously without relying on the driver as a fallback. Level 4, high automation, is limited to certain operational design domains such as highways, whereas Level 5, full automation, must be operational anywhere in any condition. Level 4 and Level 5 autonomous vehicles are still unavailable in the market as of today, and are being developed by many companies. Notably, one of the most press-worthy advancements is the fleet of Waymo cars, which have been drive-tested for over 20 million miles since 2009 (Waymo, 2020); in 2018, this fleet achieved an average of 11,017 miles traveled between disengagements, where emergency overrides by a human operator were enforced (Crowe, 2019a,b). However, this metric for distance between disengagements has been criticized by autonomous-driving companies, including Waymo themselves (Fernandez, 2020), because it is misleading when used for measuring progress as miles tested in different settings are hardly comparable, *e.g.*, empty highway vs. busy urban areas.

The commercialization and production development of autonomous driving were ignited by a series of the Defense Research Advance Projects Agency (DARPA) sponsored challenges: the Grand Challenges in 2004 and 2005, and the Urban Challenge in 2007 (Buehler *et al.*, 2007, 2009). Autonomous vehicles participating in the Grand Challenges were expected to drive through unrehearsed off-road terrain without manual intervention. In its first event in 2004, none of the 15 racing teams finished more than 5% of a 142-mile course on the desert within the ten-hour time limit (Thrun *et al.*, 2006). In the second event in 2005, five out of 23 racing teams finished, and "Stanley" (from Stanford University), finishing in under seven hours, won first place (Thrun *et al.*, 2006), six minutes before the second place of "Sandstorm" and

"H1ghlander" (Urmson *et al.*, 2006). These Grand Challenges spurred innovation in the areas of perception, collision avoidance, vehicle control, and others.

If driving on a desert as required by the DARPA Grand Challenges is not considered relevant enough to our daily life, the third event—the DARPA Urban Challenge—should be. The Urban Challenge set the goal to traverse through traffic in urban settings without violating California traffic rules (Buehler *et al.*, 2009; Urmson *et al.*, 2008). Eleven of the 53 teams passed the National Qualification Event, and competed in the Urban Challenge Final Event. In the end, six teams finished the challenge, with "Boss" of Carnegie Mellon University winning first place.

In all of these production and prototype cars, cameras and computer-vision technologies were used alongside processing techniques for other sensors such as lidars and radars.

The DARPA Challenges revitalized interest in autonomous driving, for which the initial interest can be traced back to the late 1980s, when Carnegie Mellon University's Navigation Laboratory (Navlab) presented a series of Navlab vehicles with basic autonomy (Thorpe *et al.*, 1988, 1991a,b). The basic system architecture developed by Thorpe *et al.* (1991b) is common in today's approaches. In 1988, Thorpe *et al.* presented a van equipped with one TV camera and one laser rangefinder to enable road-following and collision detection and avoidance (Thorpe *et al.*, 1988). Later, Pomerleau (1989, 1992) presented the neural network ALVINN, which generates navigation direction outputs from camera and laser rangefinder image inputs. At the end of the Navlab project, an important milestone was achieved as Jochem and Pomerleau (1995) finished "No hands across America," a trip from Pittsburgh, PA to San Diego, CA, with the steering direction controlled based on the image inputs and the throttle and brake handled by human.

During the same period, the Eureka Project PROgraMme for a European Traffic of Highest Efficiency and Unprecedented Safety (PROMETHEUS), the largest R&D autonomous-driving project at the time, was carried out and spread broad interest in Europe in active safety systems (Williams, 1988; Ibaez-Guzmn *et al.*, 2012). Dickmanns and Zapp (1987) first demonstrated the early results of vision-based guidance for high-speed autonomous driving on a well-structured highway with one-way traffic. In the PROMETHEUS project's final demonstration, two vehicles, "VITA II" of Daimler-Benz (Ulmer, 1994) and "VaMoRs-P" of Bundeswehr University Munich (Dickmanns *et al.*, 1994), demonstrated autonomous driving at a speed up to 130 km per hour in public traffic on highways (Dickmanns *et al.*, 1997).

The development of autonomous driving has been ongoing for some time, and has provided a valuable reference for autonomous-driving system architectures, which we review next.

## 2.1.2 Autonomous-Driving System Architecture

In this section, we review autonomous-driving system architectures that have been used in state-of-the-art proof-of-concept research projects, and then focus on modular systems, for which we provide a detailed review of each sub-component, and the connections and interfaces between them. Of these components, the perception component is highlighted in our review, given our focus on computer-vision applications.

#### 2.1.2.1 Architecture

Many of the aforementioned autonomous systems (Section 2.1.1) use a *modular system* architecture, in which components that provide different functionalities are encapsulated separately and are related as the nodes in a connected graph, from the sensor input to the vehicle control (Behere and Törngren, 2016). Another approach is learning-based *end-to-end driving systems*, which were demonstrated very early on (Pomerleau, 1989) and emerged again recently. These end-to-end driving systems are usually neural networks that receive sensor inputs through the network to directly generate control commands. We briefly review the history and state of the art of end-to-end driving systems, and then discuss why we instead focus on modular systems.

End-to-end driving systems. The earliest end-to-end driving system was ALVINN, presented by Pomerleau (1989). ALVINN is a neural network that generates directions for lane-following with inputs from a camera and a laser rangefinder. It was trained using supervised learning with simulated road images, and it demonstrates lane-following on real roads under certain conditions. Muller *et al.* (2006) extended its autonomous capability to off-road obstacle avoidance using stereo cameras and a convolutional neural network (CNN). The results were significantly improved in a similar approach by NVIDIA, in which a larger convolutional network and training dataset were used (Bojarski *et al.*, 2016), as demonstrated on highways and parking lots. These approaches are categorized as *imitation learning*, as they accept human input as part of the training data, and the goal of the system is to drive like a human. However, they fail in situations where turning guidance is needed at intersections, thus Codevilla *et al.* (2018) proposed *conditional imitation learning* to add training signals about a driver's intention to solve the ambiguity.

An alternative approach is *reinforcement learning* (RL), the goal of which is to maximize future rewards under predefined reward policies (Mnih *et al.*, 2015). Sallab *et al.* (2017) demonstrated deep RL in a simulator

<sup>&</sup>lt;sup>1</sup>Often called *pixel-to-torque* systems.

using recurrent neural networks (RNNs) that integrated information and handled partially observable scenarios. Kendall *et al.* (2019) then demonstrated real-road lane-following trained with a few episodes<sup>2</sup> using RL for the first time.