## A Lock-Free Approach to Object Sharing in Real-Time Systems

by

## Srikanth Ramamurthy

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill

1997

| Approved by:                  |  |  |  |

|-------------------------------|--|--|--|

|                               |  |  |  |

| Prof. James Anderson, Adviser |  |  |  |

|                               |  |  |  |

| Prof. Prasun Dewan, Reader    |  |  |  |

| Prof. Kevin Jeffay, Reader    |  |  |  |

©1997 Srikanth Ramamurthy ALL RIGHTS RESERVED SRIKANTH RAMAMURTHY. A Lock-Free Approach to Object Sharing in Real-Time Systems

(Under the direction of Professor James H. Anderson.)

#### Abstract

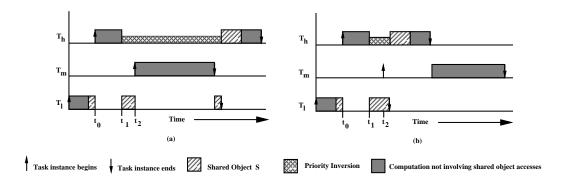

This work aims to establish the viability of lock-free object sharing in uniprocessor real-time systems. Naive usage of conventional lock-based object-sharing schemes in real-time systems leads to unbounded *priority inversion*. A priority inversion occurs when a task is blocked by a lower-priority task that is inside a critical section. Mechanisms that bound priority inversion usually entail kernel overhead that is sometimes excessive.

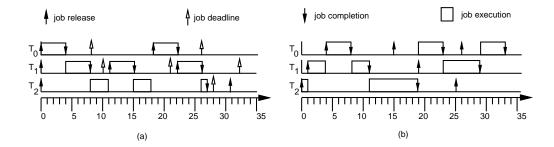

We propose that lock-free objects offer an attractive alternative to lock-based schemes because they eliminate priority inversion and its associated problems. On the surface, lock-free objects may seem to be unsuitable for hard real-time systems because accesses to such objects are not guaranteed to complete in bounded time. Nonetheless, we present scheduling conditions that demonstrate the applicability of lock-free objects in hard real-time systems. Our scheduling conditions are applicable to schemes such as rate-monotonic scheduling and earliest-deadline-first scheduling.

Previously known lock-free constructions are targeted towards asynchronous systems; such constructions require hardware support for strong synchronization primitives such as compare-and-swap. We show that constructions for uniprocessor real-time systems can be significantly simplified — and the need for strong primitives eliminated — by exploiting certain characteristics of real-time scheduling schemes.

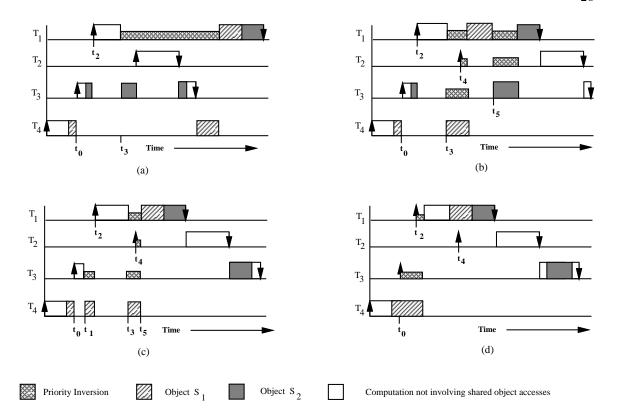

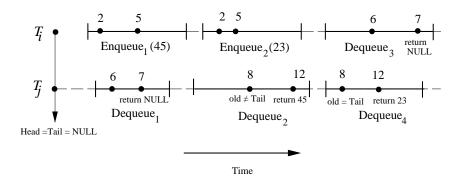

Under lock-based schemes, a task can perform operations on many shared objects simultaneously via nested critical sections. For example, using nested critical sections, a task can atomically dequeue an element from one shared queue and enqueue that element in another shared queue. In order to achieve the level of functionality provided by nested critical sections, we provide a lock-free framework that is based on a multi-word compare-and-swap primitive and that supports multi-object accesses — the lock-free counterpart to nested critical sections. Because multi-word primitives are not provided in hardware, they have to be implemented in software. We provide a time-optimal implementation of the multi-word compare-and-swap primitive.

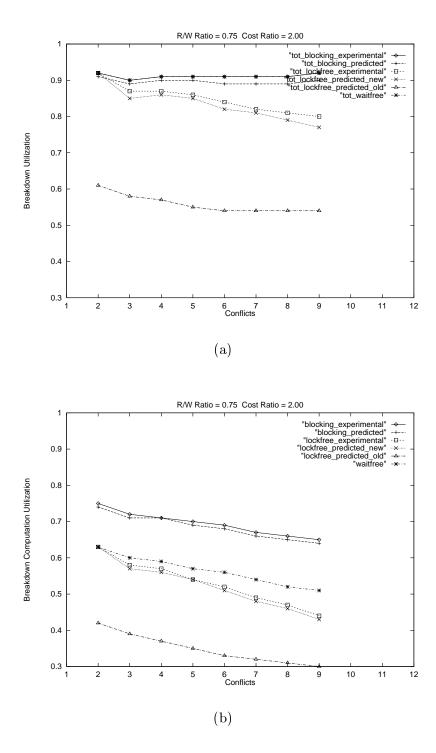

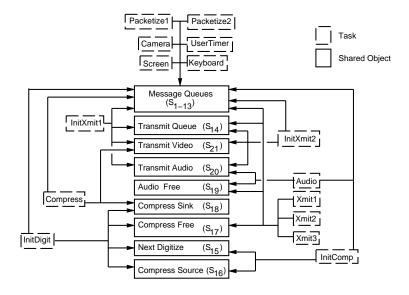

Finally, we present a formal comparison of the various object-sharing schemes based on scheduling conditions, followed by results from a set of simulation experiments that we conducted. Also, as empirical proof of the viability of lock-free objects in practical systems, we present results from a set of experiments conducted on a desktop videoconferencing system.

#### Acknowledgements

I would like to thank my adviser Jim Anderson for educating me and advising me over the years with much enthusiasm and patience. I would also like to thank him for supporting me for several years.

I would also like to thank my committee: Rance Cleaveland, Prasun Dewan, Rich Gerber, Kevin Jeffay, and Don Stanat. I thank them for their willingness to find time to attend the myriad pre-proposal meetings, oral examinations, proposals, and one-on-one meetings. Special thanks to Rance Cleaveland for driving long distances to attend the various meetings, and to Rich Gerber for enduring many long meetings over the phone and providing very insighful comments on my work. I am also grateful to Kevin Jeffay for being extremely supportive and encouraging of my work.

My work has also benefited significantly from many discussions with the following friends and colleagues: Steve Goddard, Rohit Jain, Mark Moir, M. Paramasivam, Tom White, and Jason Wilson. I would like to thank Dave Bennett, Peter Nee, Mark Parris, and Don Stone for their help in all the experimental work.

I would also like to thank many of my friends in Chapel Hill for their support and camaraderie; graduate school would have been boring and weary without them. I am thankful to my parents for encouraging me to strive for the best always and for their support. I am also thankful to Ranga and Malathi for their love and support. This dissertation would not have been possible were it not for the support of my wife Bhuva. She has tolerated a lot over the past few of years with much cheer.

# Contents

| $\mathbf{Li}$ | st of          | Figures                                                  | viii |

|---------------|----------------|----------------------------------------------------------|------|

| Li            | st of          | Tables                                                   | x    |

| 1             | Intr           | oduction                                                 | 1    |

|               | 1.1            | Lock-Based Object Sharing in Hard Real-Time Systems      | 3    |

|               | 1.2            | Lock-Free Objects                                        | 6    |

|               | 1.3            | Background on Real-Time Systems                          | 11   |

|               |                | 1.3.1 Real-Time Scheduling Schemes                       | 12   |

|               | 1.4            | Our Contributions                                        | 15   |

|               |                | 1.4.1 Schedulability of Lock-Free Task Sets              | 15   |

|               |                | 1.4.2 Eliminating Hardware Support for Strong Primitives | 16   |

|               |                | 1.4.3 A General Framework for Lock-Free Accesses         | 17   |

|               |                | 1.4.4 Experimental Results                               | 18   |

|               | 1.5            | Organization of the Dissertation                         | 19   |

| <b>2</b>      | Bac            | kground and Related Work                                 | 20   |

|               | 2.1            | Scheduling Conditions                                    | 20   |

|               |                | 2.1.1 Static-Priority Scheduling Conditions              | 21   |

|               |                | 2.1.2 Dynamic-Priority Scheduling Conditions             | 23   |

|               | 2.2            | Lock-Based Object Sharing                                | 26   |

|               |                | 2.2.1 Static-Priority Scheduling Conditions              | 32   |

|               |                | 2.2.2 Dynamic-Priority Conditions                        | 33   |

|               | 2.3            | Accounting for System Overhead Costs                     | 35   |

|               | 2.4            | Lock-Free Object Implementations                         | 38   |

|               |                | 2.4.1 Linearizability                                    | 39   |

|               |                | 2.4.2 The Consensus Hierarchy                            | 41   |

|               |                | 2.4.3 Universal Constructions of Lock-Free Objects       | 43   |

|               |                | 2.4.4 Specific Objects                                   | 49   |

| 3             | $\mathbf{Sch}$ | eduling Conditions                                       | 51   |

|               | 3.1            | Assumptions and Definitions                              | 52   |

|               | 3.2            | Preliminary Lemmas                                       | 58   |

|               | 3.3            | Static-Priority Scheduling Conditions                    | 63   |

|          | 3.4                                       | Dynamic-Priority Scheduling Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69                                                                        |

|----------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

|          | 3.5                                       | Accounting for Different Retry-Loop Costs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 74                                                                        |

|          |                                           | 3.5.1 Additional Notation and Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75<br>77                                                                  |

|          |                                           | 3.5.3 Static-Priority Scheduling Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 78                                                                        |

|          |                                           | 3.5.4 Dynamic-Priority Scheduling Schemes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 84                                                                        |

|          | 3.6                                       | Static-Priority Scheduling Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85                                                                        |

|          | 3.7                                       | Dynamic-Priority Scheduling Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88                                                                        |

| 4        | Sup                                       | oport for Strong Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90                                                                        |

|          | $4.1^{-}$                                 | The Real-Time Task Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91                                                                        |

|          | 4.2                                       | Definitions and Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 93                                                                        |

|          | 4.3                                       | Universality of Load and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96                                                                        |

|          | 4.4                                       | Implementing CAS using Loads and Stores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 101                                                                       |

|          |                                           | 4.4.1 Correctness Proof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 106                                                                       |

|          | 4.5                                       | Implementing CAS using Move, Load, and Store Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 127                                                                       |

|          |                                           | 4.5.1 Correctness Proof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 130                                                                       |

|          | 4.6                                       | Implementing Multi-Word Primitives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 138                                                                       |

|          |                                           | 4.6.1 A Wait-Free Implementation of MWCAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 138                                                                       |

|          |                                           | 4.6.2 Correctness Proof                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 147                                                                       |

|          |                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                           |

| 5        | АТ                                        | Transactional Framework for Implementing Lock-Free Objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | L61                                                                       |

| 5        | <b>A T</b> 5.1                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 <b>61</b>                                                               |

| 5        |                                           | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                           |

|          | 5.1                                       | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>7</b> 8                                                |

|          | 5.1                                       | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>1 <b>7</b> 9                                 |

|          | 5.1<br><b>A</b> (                         | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179                                          |

|          | 5.1<br><b>A</b> (                         | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179<br>179                                   |

|          | 5.1<br><b>A</b> 0<br>6.1                  | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179<br>181                                   |

|          | 5.1<br><b>A</b> 6.1<br>6.2                | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179<br>181<br>183                            |

|          | 5.1<br><b>A</b> (6.1<br>6.2<br>6.3        | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179<br>181<br>183<br>185                     |

|          | 5.1<br><b>A</b> 6.1<br>6.2                | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>1 <b>78</b><br>179<br>181<br>183<br>185<br>205              |

|          | 5.1<br><b>A</b> (6.1<br>6.2<br>6.3        | Lock-Free Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 162<br>169<br>178<br>179<br>181<br>183<br>185<br>205<br>206               |