# SCHEDULING AND LOCKING IN MULTIPROCESSOR REAL-TIME OPERATING SYSTEMS

Björn B. Brandenburg

A dissertation submitted to the faculty of the University of North Carolina at Chapel Hill in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science.

Chapel Hill 2011

Approved by:

James H. Anderson

Sanjoy K. Baruah

Hermann Härtig

Jan F. Prins

F. Donelson Smith

Paul E. McKenney

©2011 Björn B. Brandenburg ALL RIGHTS RESERVED

# **ABSTRACT**

BJÖRN B. BRANDENBURG: Scheduling and Locking in Multiprocessor Real-Time Operating

Systems

(Under the direction of James H. Anderson)

With the widespread adoption of multicore architectures, multiprocessors are now a standard deployment platform for (soft) real-time applications. This dissertation addresses two questions fundamental to the design of multicore-ready real-time operating systems: (1) Which scheduling policies offer the greatest flexibility in satisfying temporal constraints; and (2) which locking algorithms should be used to avoid unpredictable delays?

With regard to Question 1, LITMUS<sup>RT</sup>, a real-time extension of the Linux kernel, is presented and its design is discussed in detail. Notably, LITMUS<sup>RT</sup> implements link-based scheduling, a novel approach to controlling blocking due to non-preemptive sections. Each implemented scheduler (22 configurations in total) is evaluated under consideration of overheads on a 24-core Intel Xeon platform. The experiments show that partitioned earliest-deadline first (EDF) scheduling is generally preferable in a hard real-time setting, whereas global and clustered EDF scheduling are effective in a soft real-time setting.

With regard to Question 2, real-time locking protocols are required to ensure that the maximum delay due to priority inversion can be bounded *a priori*. Several spinlock- and semaphore-based multiprocessor real-time locking protocols for mutual exclusion (mutex), reader-writer (RW) exclusion, and *k*-exclusion are proposed and analyzed. A new category of RW locks suited to worst-case analysis, termed phase-fair locks, is proposed and three efficient phase-fair spinlock implementations are provided (one with few atomic operations, one with low space requirements, and one with constant RMR complexity).

Maximum priority-inversion blocking is proposed as a natural complexity measure for semaphore protocols. It is shown that there are two classes of schedulability analysis, namely suspension-oblivious and suspension-aware analysis, that yield two different lower bounds on blocking. Five

asymptotically optimal locking protocols are designed and analyzed: a family of mutex, RW, and k-exclusion protocols for global, partitioned, and clustered scheduling that are asymptotically optimal in the suspension-oblivious case, and a mutex protocol for partitioned scheduling that is asymptotically optimal in the suspension-aware case. A LITMUS<sup>RT</sup>-based empirical evaluation is presented that shows these protocols to be practical.

To my parents, Harald and Petra.

## ACKNOWLEDGEMENTS

I am indebted to many people who first helped me to get into graduate school, and then helped me to get out again. First of all, I would like to thank my advisor, Jim Anderson, for his unwavering support, and my committee, Sanjoy Baruah, Hermann Härtig, Jan Prins, Don Smith, and Paul McKenney, for their guidance and advice. I would also like to express my thanks and appreciation to all my co-authors, Aaron Block, Hennadiy Leontyev, John Calandrino, Uma Devi, Mac Mollison, Chris Kenna, Andrea Bastoni, Jonathan Hermann, and Alex Mills, and the students in the real-time systems group that I sadly did not have a chance to write a paper with, Cong Liu, Glenn Elliott, Guruprasad Aphale, Jeremy Erickson, Haohan Li, Bipasa Chattopadhyay, and Chih-Hao Sun, for their help and feedback. Many thanks also to the friendly CS department staff, and in particular Jodie Turnbull, John Sopko, Murray Anderegg, and Mike Stone, who helped me in many large and small ways over the years.

I am grateful to the German-American Fulbright Program and the Graduate School's Dissertation Completion Fellowship for financial support during my first and last year in graduate school, respectively. Without Fulbright's support, I probably would not have attended an American graduate school. Special thanks are also due to Jan Prins, for quickly un-rejecting my application to UNC after it ended up on the wrong pile due to a "processing mishap."

Life in Sitterson Hall and Brooks Building would not have been much fun without my friends in the CS department: Aaron Block, Sasa Junuzovic, Jay Aikat, Sean Curtis, Stephen Olivier, Keith Lee, Jamie Snape, Srinivas Krishnan, Anish Chandak, Jeff Terrell, Stephen Guy—thank y'all for a great time in North Carolina!

Outside school, I am greatly indebted to Jasper McChesney. I was very lucky to meet you by chance in the roommate lottery and have greatly enjoyed your company—thank you very much for the many interesting discussions, hiking trips, and wonderful times of advanced nerdery. In a similar vein, I would also like to thank Dot Hall for her compassion, energy, and the occasional crazy idea. Too bad that we overlapped in Chapel Hill for only a short time.

Very special thanks to Aaron and Nicki Block for their unrelenting support and mentorship. Whenever I needed help or guidance, I knew I could count on you. You taught me a lot about American culture; without you my stay in the U.S. would have been only half as interesting and fun. Thank you very much for your generosity and friendship. One day we will finish that bike ride around Berlin!

Another colleague and friend that deserves special mention is Andrea Bastoni, who was a visiting scholar with UNC's real-time group from October 2009 until October 2010. Thanks a lot for all the fun we had inside and outside of the department, for the papers we wrote, and for your contributions to LITMUS<sup>RT</sup>. You came at exactly the right time; unfortunately you had to leave again after only a year. Thanks for staying involved with LITMUS<sup>RT</sup> anyway.

Foremost, I thank my parents Harald and Petra for their unwavering support, understanding, and encouragement, both during graduate school and the years before. A defining event in my life was the high school exchange that brought me to Mayfield High School in Las Cruces, NM during junior year. In Las Cruces, I developed ambition and tenacity, without which this dissertation would not have been possible. For this I would like to thank my former host parents Barbara and George Stafford, who out of the kindness of their hearts opened their door to an unknown teenager.

Finally, I am deeply thankful to Nora, for all the love and support, for her patience, for following me halfway around the world to North Carolina, and for her trust that this was indeed the right way. I could not have finished this without you.

# TABLE OF CONTENTS

| LI | ST OI | FTABL   | ES                                                            | xvi   |

|----|-------|---------|---------------------------------------------------------------|-------|

| LI | ST OI | F FIGUI | RES                                                           | xvii  |

| LI | ST OI | F ABBR  | REVIATIONS                                                    | xxiii |

| 1  | INT   | RODUC   | CTION                                                         | 1     |

|    | 1.1   | The Co  | ost of Over-Provisioning                                      | 2     |

|    | 1.2   | The Di  | ivergence of Theory and Practice                              | 3     |

|    |       | 1.2.1   | Background                                                    | 3     |

|    |       | 1.2.2   | Multiprocessor Real-Time Scheduling                           | 6     |

|    |       | 1.2.3   | Real-Time Locking                                             | 9     |

|    | 1.3   | Thesis  | Statement                                                     | 10    |

|    | 1.4   | Contri  | butions                                                       | 11    |

|    |       | 1.4.1   | LITMUS <sup>RT</sup>                                          | 11    |

|    |       | 1.4.2   | Comprehensive Overhead Accounting                             | 12    |

|    |       | 1.4.3   | Overhead-Aware Evaluation Methodology                         | 13    |

|    |       | 1.4.4   | Case Study: Multiprocessor Real-time Scheduling on 24 Cores   | 14    |

|    |       | 1.4.5   | Spin-Based Locking Protocols                                  | 14    |

|    |       | 1.4.6   | Efficient Phase-Fair Spinlock Implementations                 | 16    |

|    |       | 1.4.7   | A Notion of Optimality for Suspension-Based Locking Protocols | 17    |

|    |       | 1.4.8   | Optimal Suspension-Based Multiprocessor Locking Protocols     | 18    |

|    |       | 1.4.9   | Case Study: The Impact of Overheads on Locking Protocols      | 19    |

|    | 1.5   | Organi  | ization                                                       | 20    |

| 2 | BAC | CKGRO  | ND AND PRIOR WORK                                    |

|---|-----|--------|------------------------------------------------------|

|   | 2.1 | Hardw  | re Foundations                                       |

|   |     | 2.1.1  | Multiprocessors and Multicore Platforms              |

|   |     | 2.1.2  | Processor Caches                                     |

|   |     | 2.1.3  | Interrupts                                           |

|   |     | 2.1.4  | Timers and Clocks                                    |

|   | 2.2 | Real-T | ne Task Model and Constraints                        |

|   |     | 2.2.1  | Temporal Correctness                                 |

|   |     | 2.2.2  | Alternate Soft Real-Time Definitions                 |

|   |     | 2.2.3  | Schedulability Analysis Concepts                     |

|   | 2.3 | Real-T | ne Scheduling                                        |

|   |     | 2.3.1  | Uniprocessor Real-Time Scheduling                    |

|   |     |        | 2.3.1.1 Fixed-Priority Scheduling                    |

|   |     |        | 2.3.1.2 Job-Level Fixed-Priority Scheduling          |

|   |     | 2.3.2  | Partitioned Multiprocessor Real-Time Scheduling      |

|   |     | 2.3.3  | Global Multiprocessor Real-Time Scheduling           |

|   |     |        | 2.3.3.1 Global Fixed-Priority Scheduling             |

|   |     |        | 2.3.3.2 Global Job-Level Fixed-Priority Scheduling   |

|   |     |        | 2.3.3.3 Global Job-Level Dynamic-Priority Scheduling |

|   |     | 2.3.4  | Clustered Multiprocessor Real-Time Scheduling        |

|   | 2.4 | Real-T | ne Locking Protocols                                 |

|   |     | 2.4.1  | Resource Model                                       |

|   |     | 2.4.2  | Priority Inversion Blocking                          |

|   |     | 2.4.3  | Uniprocessor Real-Time Locking Protocols             |

|   |     | 2.4.4  | Multiprocessor Real-Time Locking Protocols           |

|   |     |        | 2.4.4.1 Spinlock Protocols                           |

|   |     |        | 2.4.4.2 Semaphore Protocols                          |

|   |     | 2.4.5  | Further Results in Real-Time Locking                 |

| 2.  | 5 Rea | al-Time Oper   | rating Systems                                          | 135 |

|-----|-------|----------------|---------------------------------------------------------|-----|

|     | 2.5   | .1 Purpose     | e-Built Real-Time Operating Systems                     | 138 |

|     |       | 2.5.1.1        | Category I: Deeply-Embedded Real-Time Operating Systems | 139 |

|     |       | 2.5.1.2        | Category II: UNIX-like Real-Time Operating Systems      | 142 |

|     |       | 2.5.1.3        | Category III: Separation Kernels                        | 145 |

|     |       | 2.5.1.4        | Category IV: Research Kernels                           | 146 |

|     | 2.5   | .2 Real-Ti     | me Extensions of General-Purpose Operating Systems      | 148 |

|     |       | 2.5.2.1        | Para-Virtualized Real-Time Linux                        | 150 |

|     |       | 2.5.2.2        | Native Real-Time Linux                                  | 152 |

| 3 T | HEORY | Y, PRACTIC     | E, AND OVERHEADS                                        | 160 |

| 3.  | 1 A F | Practical Inte | rpretation of the Sporadic Task Model                   | 160 |

| 3.  | 2 The | e Linux Sche   | duling Framework                                        | 167 |

|     | 3.2   | .1 Invocati    | on of the Scheduler                                     | 167 |

|     | 3.2   | .2 Hierarch    | hical Scheduling Classes and Per-Processor Runqueues    | 168 |

|     | 3.2   | .3 The Tin     | nesharing Scheduling Class                              | 170 |

|     | 3.2   | .4 The Rea     | al-Time Scheduling Class                                | 171 |

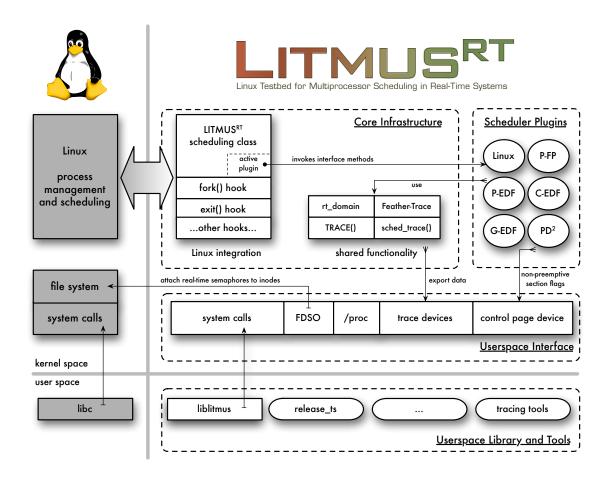

| 3.  | 3 The | e Design and   | Implementation of LITMUS <sup>RT</sup>                  | 180 |

|     | 3.3   | .1 The Arc     | chitecture of LITMUS <sup>RT</sup>                      | 182 |

|     |       | 3.3.1.1        | The LITMUS <sup>RT</sup> Core Infrastructure            | 182 |

|     |       | 3.3.1.2        | Scheduler Plugins                                       | 185 |

|     |       | 3.3.1.3        | User-Space Interface                                    | 189 |

|     |       | 3.3.1.4        | User-Space Library and Tools                            | 194 |

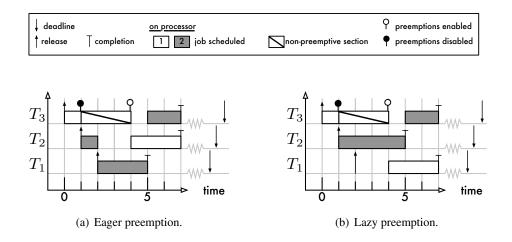

|     | 3.3   | .2 Low-Ov      | verhead Non-Preemptive Sections                         | 194 |

|     | 3.3   | .3 Non-Pro     | eemptive Sections with Predictable Pi-Blocking          | 198 |

|     | 3.3   | .4 Safe Pro    | ocess Migrations                                        | 205 |

|     | 3.3   | .5 Ready (     | Queue and Release Queue                                 | 209 |

|     |       |                |                                                         |     |

|   |     | 3.3.6  | Scheduler Plugin Implementation                | 211 |

|---|-----|--------|------------------------------------------------|-----|

|   |     |        | 3.3.6.1 The P-FP Plugin                        | 212 |

|   |     |        | 3.3.6.2 The P-EDF Plugin                       | 213 |

|   |     |        | 3.3.6.3 The G-EDF Plugin                       | 213 |

|   |     |        | 3.3.6.4 The C-EDF Plugin                       | 215 |

|   |     |        | 3.3.6.5 The PD <sup>2</sup> Plugin             | 216 |

|   | 3.4 | Overho | ead Accounting under Event-Driven Schedulers   | 219 |

|   |     | 3.4.1  | Approach                                       | 220 |

|   |     | 3.4.2  | Release Delay                                  | 221 |

|   |     | 3.4.3  | Preemption and Migration Delays                | 230 |

|   |     | 3.4.4  | Interrupt Delays                               | 235 |

|   |     |        | 3.4.4.1 Release Interrupts                     | 237 |

|   |     |        | 3.4.4.2 Timer Ticks                            | 242 |

|   |     | 3.4.5  | Preemption-Centric Interrupt Accounting        | 250 |

|   |     | 3.4.6  | Schedulability Analysis                        | 259 |

|   | 3.5 | Overhe | ead Accounting under Quantum-Driven Schedulers | 263 |

|   |     | 3.5.1  | Release Delay                                  | 264 |

|   |     | 3.5.2  | Effective Quantum Size                         | 266 |

|   |     | 3.5.3  | Periodic Task Sets                             | 269 |

|   | 3.6 | Summ   | ary                                            | 270 |

| 4 | OVE | ERHEAI | D-AWARE EVALUATION OF REAL-TIME SCHEDULERS     | 272 |

|   | 4.1 | Metho  | dology                                         | 273 |

|   |     | 4.1.1  | Sources of Capacity Loss                       |     |

|   |     | 4.1.2  | Evaluation Approach                            |     |

|   |     | 4.1.3  | Overhead Model                                 |     |

|   |     | 4.1.4  | Task Set Generation                            | 282 |

|   |     | 4.1.5  | Schedulability Experiments                     |     |

|     | 4.1.6  | Integrating Overhead Accounting          | . 286 |

|-----|--------|------------------------------------------|-------|

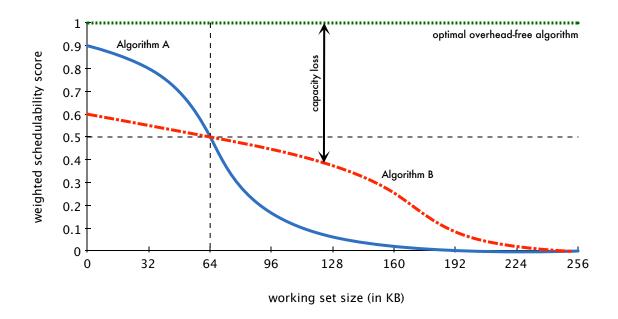

|     | 4.1.7  | Weighted Schedulability Score            | . 289 |

|     | 4.1.8  | Tardiness                                | . 293 |

| 4.2 | Case S | Study                                    | . 294 |

|     | 4.2.1  | Platform                                 | . 294 |

|     | 4.2.2  | Tested Schedulers                        | . 295 |

|     | 4.2.3  | Parameter Distributions                  | . 297 |

| 4.3 | Schedu | uling Overheads                          | . 299 |

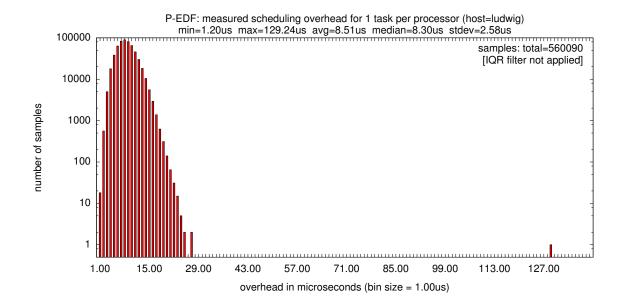

|     | 4.3.1  | Tracing, Post-Processing, and Statistics | . 299 |

|     | 4.3.2  | Experiments                              | . 305 |

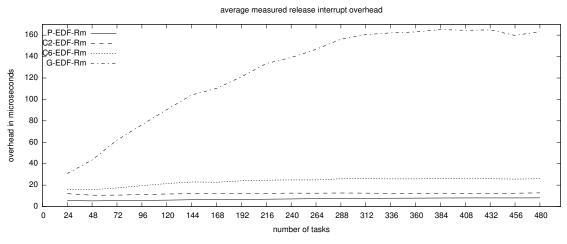

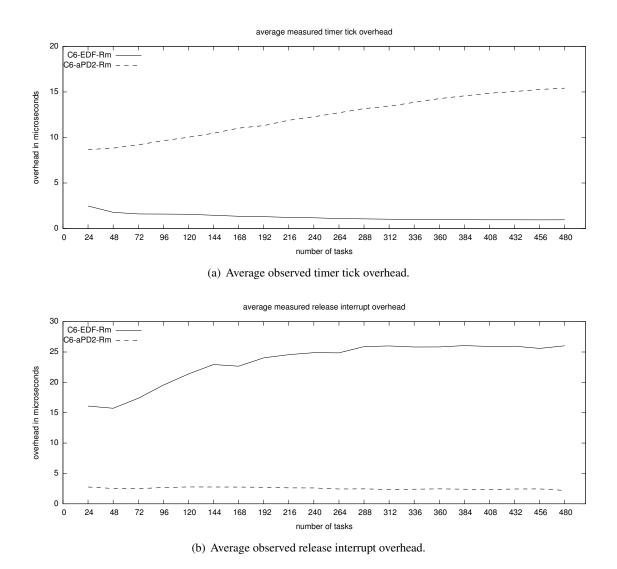

|     | 4.3.3  | Results                                  | . 306 |

| 4.4 | Cache- | -Related Overheads                       | . 318 |

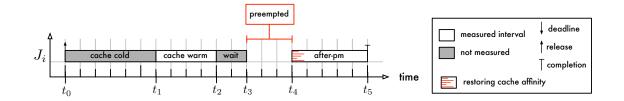

|     | 4.4.1  | Measurement Approach                     | . 319 |

|     |        | 4.4.1.1 Schedule-Sensitive Method        | . 321 |

|     |        | 4.4.1.2 Synthetic Method                 | . 322 |

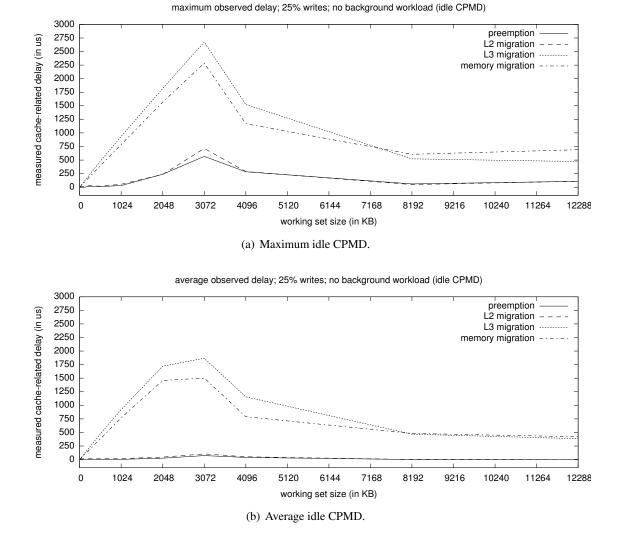

|     | 4.4.2  | Experiments                              | . 323 |

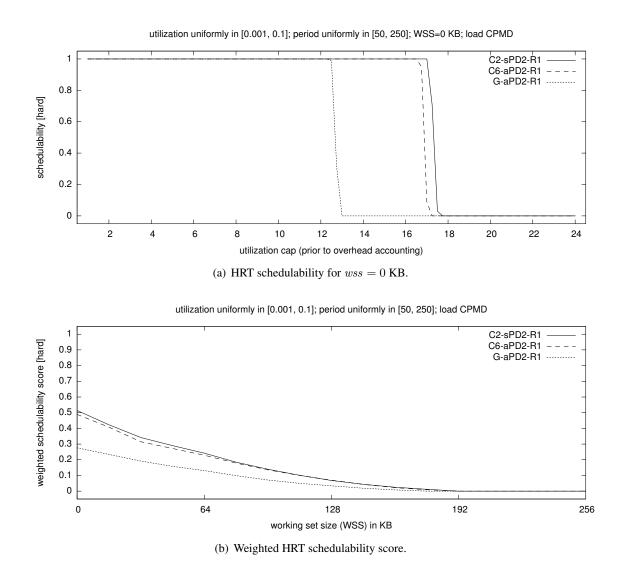

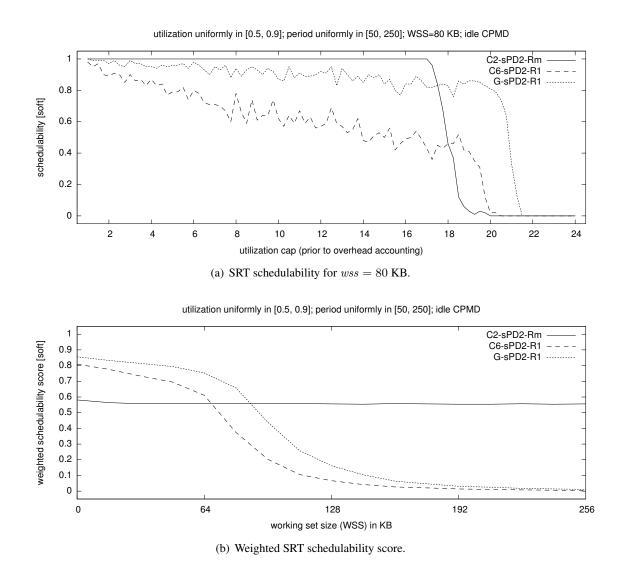

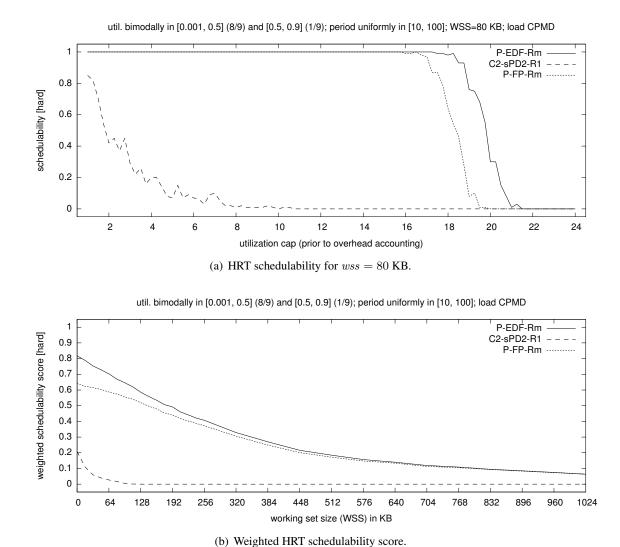

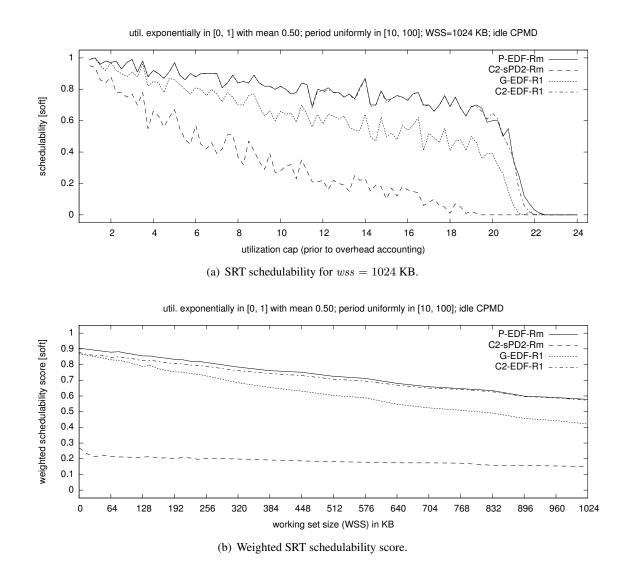

| 4.5 | Schedu | ulability Experiments                    | . 330 |

|     | 4.5.1  | Interrupt Handling and Quantum Alignment | . 333 |

|     | 4.5.2  | Cluster Size                             | . 346 |

|     | 4.5.3  | Scheduler Selection                      | . 356 |

|     | 4.5.4  | Prior Studies in Context.                | . 364 |

| 4.6 | Summ   | ary                                      | . 371 |

| REA | L-TIM  | E SPINLOCK PROTOCOLS                     | . 372 |

| 5.1 | Group  | Locking                                  | . 374 |

| 5.2 | Reader | r-Writer Spinlocks                       | . 376 |

|     | 5.2.1  | Request Order                            | . 376 |

|     |        | 5.2.1.1 Task-Fair Mutey Locks            | 377   |

5

|   |     |         | 5.2.1.2 Task-Fair RW Locks                                       | 378 |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     |         | 5.2.1.3 Preference RW Locks                                      | 380 |

|   |     |         | 5.2.1.4 Phase-Fair RW Locks                                      | 380 |

|   |     | 5.2.2   | Blocking Overview                                                | 383 |

|   | 5.3 | Efficie | ent Phase-Fair Reader-Writer Spinlocks                           | 386 |

|   |     | 5.3.1   | A Simple Phase-Fair Reader-Writer Spinlock                       | 387 |

|   |     | 5.3.2   | A Compact Phase-Fair Reader-Writer Spinlock                      | 391 |

|   |     | 5.3.3   | A Phase-Fair Reader-Writer Spinlock with Constant RMR Complexity | 395 |

|   | 5.4 | Detaile | ed Blocking Analysis                                             | 401 |

|   |     | 5.4.1   | Holistic Blocking Analysis                                       | 402 |

|   |     | 5.4.2   | Interference Sets                                                | 404 |

|   |     | 5.4.3   | Task-Fair Mutex Spinlocks                                        | 409 |

|   |     | 5.4.4   | Minimum Reader Parallelism                                       | 412 |

|   |     | 5.4.5   | Task-Fair RW Spinlocks                                           | 415 |

|   |     | 5.4.6   | Phase-Fair RW Spinlocks                                          | 417 |

|   | 5.5 | Summ    | ary                                                              | 420 |

| 6 | REA | L-TIM   | E SEMAPHORE PROTOCOLS                                            | 421 |

|   | 6.1 | Blocki  | ing Optimality                                                   | 423 |

|   |     | 6.1.1   | Priority Inversions in Multiprocessor Systems                    | 423 |

|   |     | 6.1.2   | A Blocking Complexity Measure                                    | 425 |

|   |     | 6.1.3   | Lower Bound on Maximum S-Oblivious Pi-Blocking                   | 426 |

|   |     | 6.1.4   | Lower Bound on Maximum S-Aware Pi-Blocking                       | 428 |

|   | 6.2 | Lockir  | ng under S-Oblivious Schedulability Analysis                     | 429 |

|   |     | 6.2.1   | Resource-Holder Progress                                         | 430 |

|   |     | 6.2.2   | Mutual Exclusion under Clustered Scheduling                      | 437 |

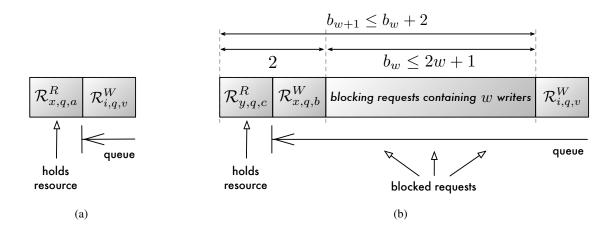

|   |     | 6.2.3   | Reader-Writer Exclusion under Clustered Scheduling               | 439 |

|   |     | 6.2.4   | k-Exclusion under Clustered Scheduling                           | 443 |

|   |     | 6.2.5   | Mutual Exclusion under Global Scheduling                  | 447 |

|---|-----|---------|-----------------------------------------------------------|-----|

|   |     | 6.2.6   | Optimality, Combinations, and Limitations                 | 451 |

|   | 6.3 | Lockir  | ng under S-Aware Schedulability Analysis                  | 457 |

|   |     | 6.3.1   | Mutual Exclusion under Partitioned Scheduling             | 458 |

|   |     | 6.3.2   | Priority Inheritance and Boosting under Global Scheduling | 463 |

|   |     | 6.3.3   | Maximum Pi-Blocking in Priority Queues                    | 469 |

|   |     | 6.3.4   | Open Questions                                            | 470 |

|   | 6.4 | Detaile | ed Blocking Analysis                                      | 472 |

|   |     | 6.4.1   | Global OMLP                                               | 473 |

|   |     | 6.4.2   | Clustered OMLP                                            | 476 |

|   |     |         | 6.4.2.1 Mutual Exclusion                                  | 476 |

|   |     |         | 6.4.2.2 Reader-Writer Exclusion                           | 478 |

|   |     |         | 6.4.2.3 <i>k</i> -Exclusion                               | 481 |

|   |     | 6.4.3   | Partitioned FMLP <sup>+</sup>                             | 483 |

|   |     |         | 6.4.3.1 Preemptive Request Execution                      | 483 |

|   |     |         | 6.4.3.2 Non-Preemptive Request Execution                  | 486 |

|   | 6.5 | Summ    | ary                                                       | 487 |

| 7 | OVE | ERHEAI  | D-AWARE EVALUATION OF REAL-TIME LOCKING PROTOCOLS         | 488 |

|   | 7.1 | Accou   | nting for Locking Overheads                               | 489 |

|   |     | 7.1.1   | Transitive Interrupt Delays                               | 490 |

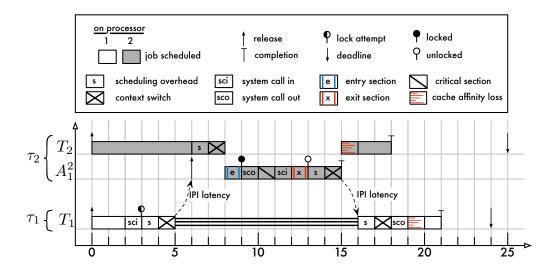

|   |     | 7.1.2   | Spinlock Protocols                                        | 492 |

|   |     | 7.1.3   | Non-Preemptive Semaphore Protocols                        | 495 |

|   |     | 7.1.4   | Preemptive Semaphore Protocols                            | 502 |

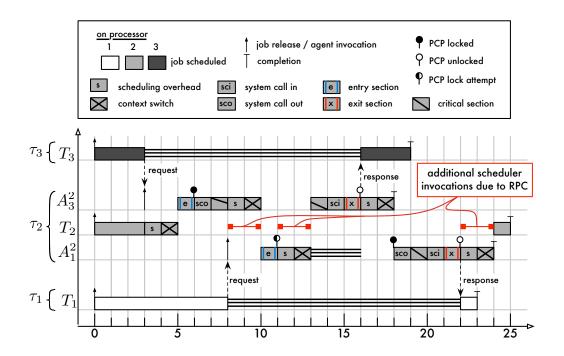

|   |     | 7.1.5   | Remote Procedure Calls                                    | 504 |

|   |     | 7.1.6   | Limitations                                               | 509 |

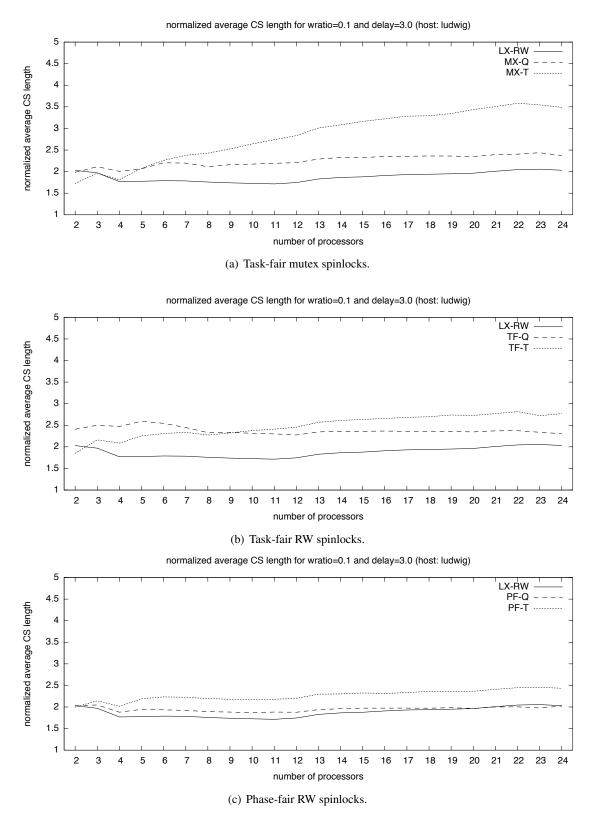

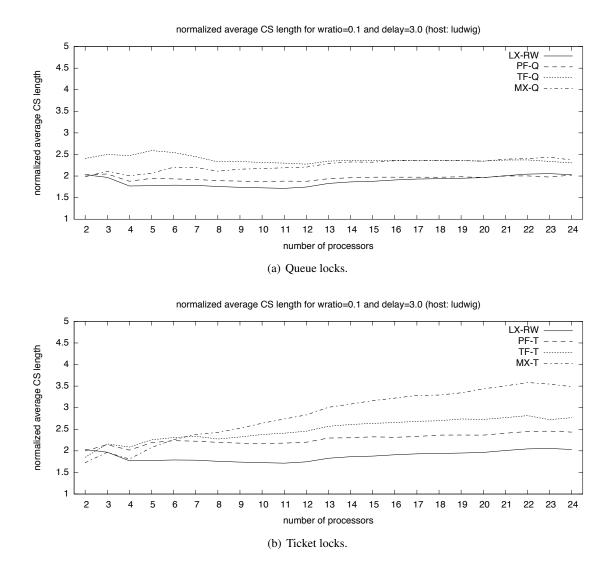

|   | 7.2 | Spinlo  | ck Implementation Efficiency                              | 510 |

|   | 7.3 | Mutex   | and Reader-Writer Spinlocks                               | 515 |

|    |      | 7.3.1  | Hard Real-Time Spinlock Comparison                                 | 517 |

|----|------|--------|--------------------------------------------------------------------|-----|

|    |      | 7.3.2  | Soft Real-Time Spinlock Comparison                                 | 521 |

|    |      | 7.3.3  | Scheduler Comparison                                               | 523 |

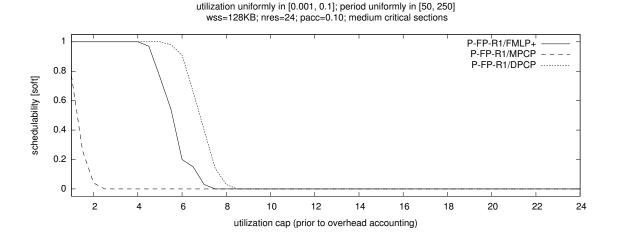

|    | 7.4  | Semap  | hore Protocols for S-Oblivious Analysis                            | 524 |

|    |      | 7.4.1  | The Global FMLP vs. the Global OMLP vs. the Clustered OMLP         | 528 |

|    |      | 7.4.2  | The Clustered OMLP vs. the MPCP-VS                                 | 532 |

|    | 7.5  | Semap  | hore Protocols for S-Aware Analysis                                | 533 |

|    |      | 7.5.1  | The FMLP <sup>+</sup> with Preemptive and Non-Preemptive Execution | 534 |

|    |      | 7.5.2  | The FMLP <sup>+</sup> vs. the MPCP vs. the DPCP                    | 535 |

|    | 7.6  | Spinni | ng vs. S-Oblivious Analysis vs. S-Aware Analysis                   | 538 |

|    | 7.7  | Summ   | ary                                                                | 543 |

| 8  | CON  | NCLUSI | ON                                                                 | 545 |

|    | 8.1  | Summ   | ary of Results                                                     | 545 |

|    |      | 8.1.1  | Theory, Practice, and Overheads                                    | 545 |

|    |      | 8.1.2  | Overhead-Aware Evaluation of Real-Time Schedulers                  | 546 |

|    |      | 8.1.3  | Real-Time Spinlock Protocols                                       | 548 |

|    |      | 8.1.4  | Real-Time Semaphore Protocols                                      | 549 |

|    |      | 8.1.5  | Overhead-Aware Evaluation of Real-Time Locking Protocols           | 550 |

|    | 8.2  | Assum  | aptions, Open Questions, and Future Work                           | 553 |

|    |      | 8.2.1  | Hardware Platform                                                  | 553 |

|    |      | 8.2.2  | Evaluation Methodology                                             | 557 |

|    |      | 8.2.3  | Scheduler Design and Implementation                                | 560 |

|    |      | 8.2.4  | Future Directions in Real-Time Locking                             | 564 |

|    | 8.3  | Closin | g Remarks                                                          | 567 |

| ΒI | BLIO | GRAPE  | IY                                                                 | 569 |

|    |      |        |                                                                    |     |

# LIST OF TABLES

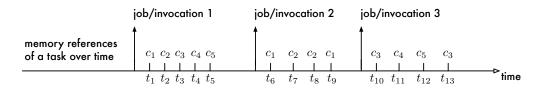

| 2.1 | Working set and cache footprint of the task depicted in Figure 2.4 | 28  |

|-----|--------------------------------------------------------------------|-----|

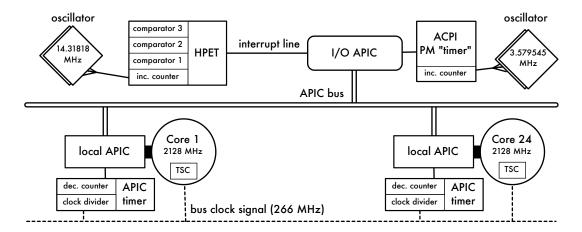

| 2.2 | Available hardware timers and clocks                               | 41  |

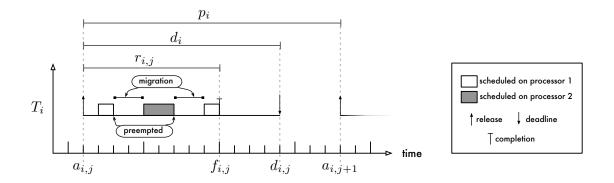

| 2.3 | Summary of notation: sporadic task model                           | 44  |

| 2.4 | Uniprocessor example task set                                      | 59  |

| 2.5 | Multiprocessor example task set                                    | 74  |

| 2.6 | Modified multiprocessor example task set                           | 86  |

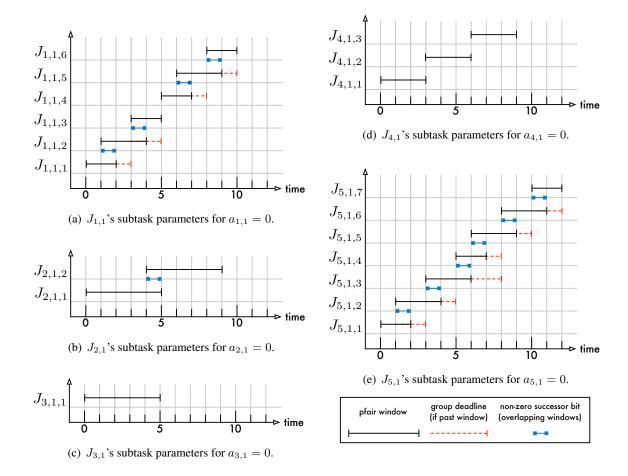

| 2.7 | Pfair subtask parameters                                           | 91  |

| 2.8 | Summary of notation: resource model                                | 104 |

| 3.1 | Methods in the LITMUS <sup>RT</sup> plugin interface               | 187 |

| 3.2 | Summary of notation: overheads in event-driven schedulers          | 260 |

| 4.1 | Evaluated schedulers                                               | 296 |

| 5.1 | Simplified bounds on worst-case s-blocking                         | 384 |

| 6.1 | S-oblivious blocking bounds of the OMLP                            | 451 |

| 6.2 | Parameters of the task set $	au^\phi$                              | 464 |

| 7.1 | Summary of notation: overheads in locking protocols                | 494 |

| 7.2 | Implemented and evaluated spinlock algorithms                      | 514 |

| 7.3 | Evaluated spinlock and scheduler combinations                      | 518 |

| 7.4 | Evaluated lock and scheduler combinations                          | 528 |

# LIST OF FIGURES

| 1.1  | Global, partitioned, and clustered scheduling             | 6  |

|------|-----------------------------------------------------------|----|

| 2.1  | Shared- and distributed-memory multiprocessors            | 22 |

| 2.2  | Identical, uniform, and unrelated multiprocessors         | 24 |

| 2.3  | Two-level cache hierarchy with shared L2 caches           | 26 |

| 2.4  | Memory reference trace                                    | 27 |

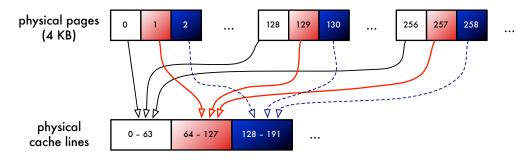

| 2.5  | Page coloring                                             | 32 |

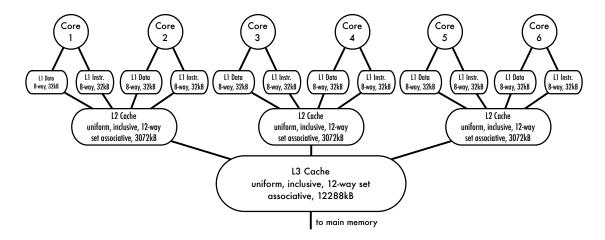

| 2.6  | Cache hierarchy of the experimental platform              | 34 |

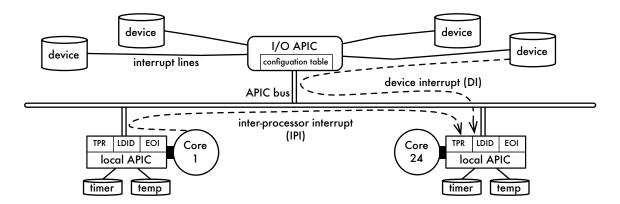

| 2.7  | I/O APIC and local APICs                                  | 36 |

| 2.8  | Available timers and clocks                               | 40 |

| 2.9  | Sporadic task model                                       | 43 |

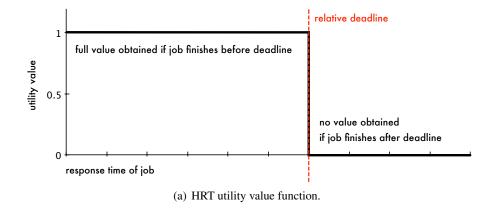

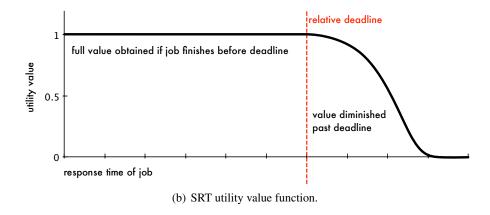

| 2.10 | Hard and soft utility value functions                     | 51 |

| 2.11 | Uniprocessor FP schedule                                  | 59 |

| 2.12 | Uniprocessor EDF schedule                                 | 62 |

| 2.13 | First-fit, best-fit, and worst-fit bin-packing heuristics | 67 |

| 2.14 | The Dhall effect                                          | 72 |

| 2.15 | Global RM schedule exhibiting unbounded tardiness         | 73 |

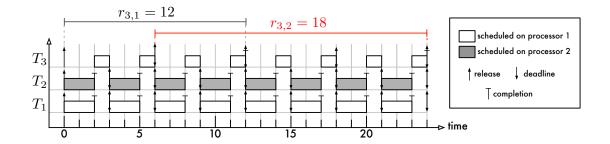

| 2.16 | Multiprocessor G-EDF schedule                             | 75 |

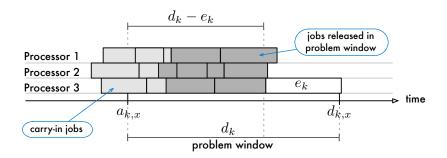

| 2.17 | Baker's problem-window approach                           | 77 |

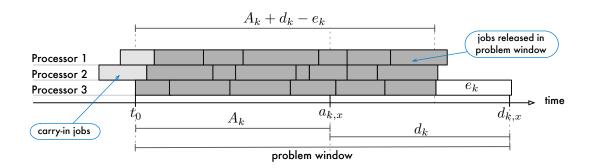

| 2.18 | Baruah's extended problem window                          | 81 |

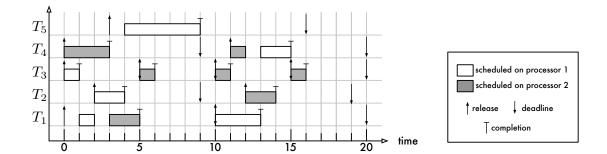

| 2.19 | Multiprocessor G-EDF schedule exhibiting a deadline miss  | 87 |

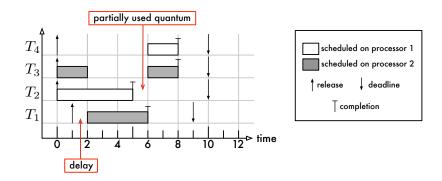

| 2.20 | Scheduling delays due to quantum-driven scheduling        | 88 |

| 2.21 | Pfair subtask parameters                                  | 92 |

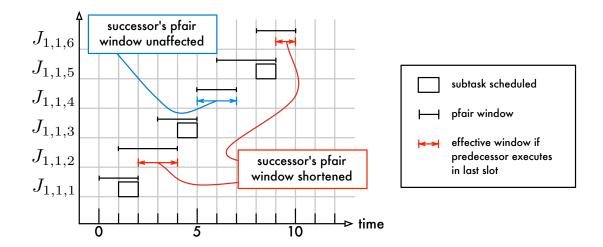

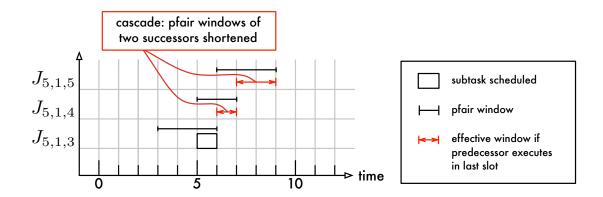

| 2.22 | Constrained pfair windows                                 | 93 |

| 2.23 | Pfair windows motivating group deadlines                  | 94 |

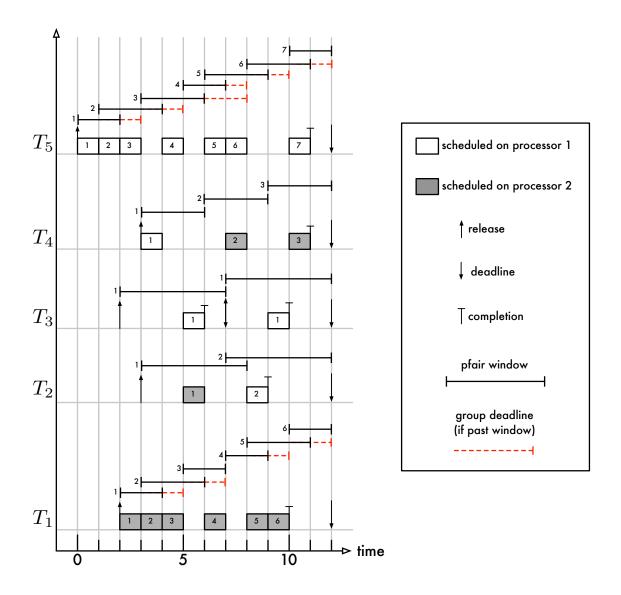

| 2.24 | Multiprocessor PD <sup>2</sup> schedule                   | 98 |

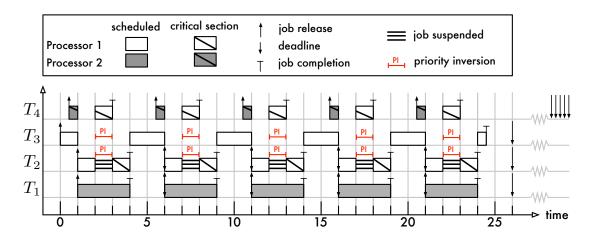

| 2.25 | Unbounded priority inversion                                             | 102 |

|------|--------------------------------------------------------------------------|-----|

| 2.26 | Resource request phases                                                  | 105 |

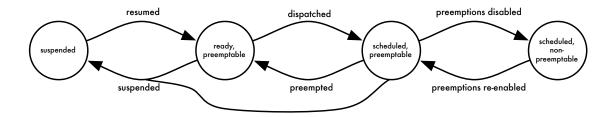

| 2.27 | Job state diagram                                                        | 106 |

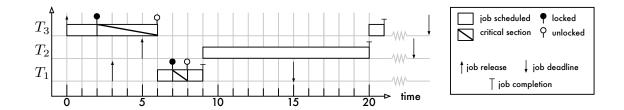

| 2.28 | Uniprocessor NCP schedule                                                | 110 |

| 2.29 | Deadline miss due to non-preemptive section                              | 111 |

| 2.30 | Uniprocessor PIP schedule demonstrating benefits of preemptive execution | 112 |

| 2.31 | Uniprocessor PIP schedule                                                | 113 |

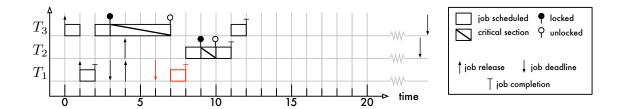

| 2.32 | Uniprocessor PIP schedule exhibiting deadlock                            | 114 |

| 2.33 | Uniprocessor PCP schedule                                                | 115 |

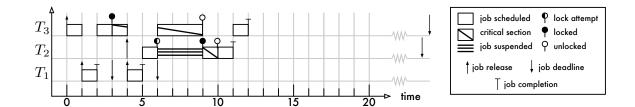

| 2.34 | Uniprocessor SRP schedule                                                | 117 |

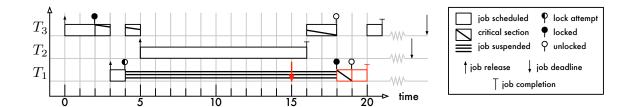

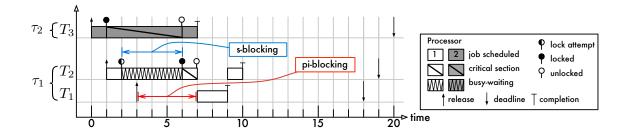

| 2.35 | Pi-blocking vs. s-blocking                                               | 121 |

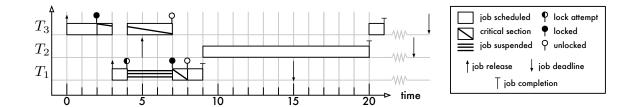

| 2.36 | MSRP schedule                                                            | 122 |

| 2.37 | PIP failure under partitioned scheduling                                 | 125 |

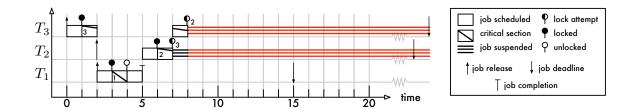

| 2.38 | DPCP schedule                                                            | 128 |

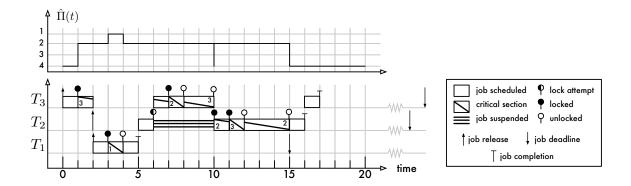

| 2.39 | MPCP schedule                                                            | 129 |

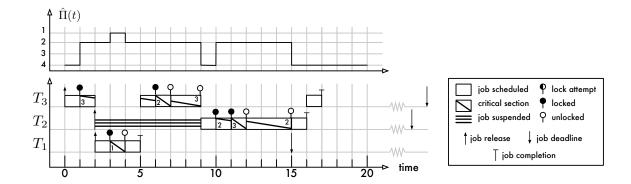

| 2.40 | MPCP-VS schedule                                                         | 132 |

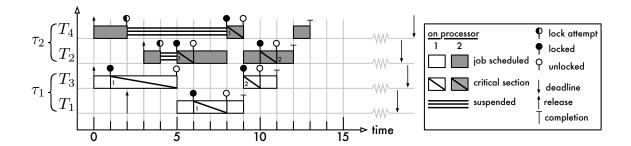

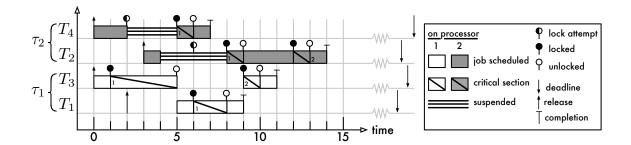

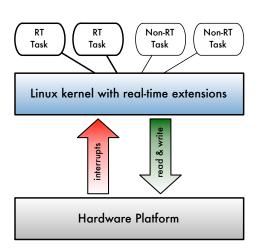

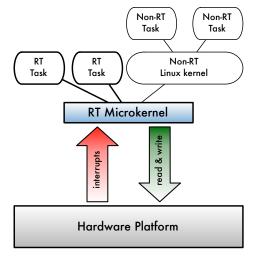

| 2.41 | Native and para-virtualized real-time Linux designs                      | 150 |

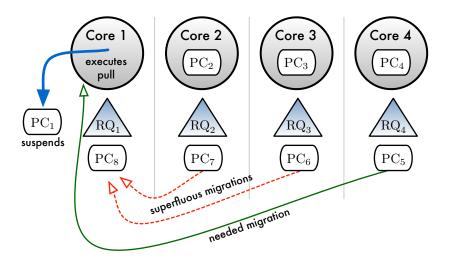

| 3.1  | Unneeded migrations caused by Linux's pull operation                     | 176 |

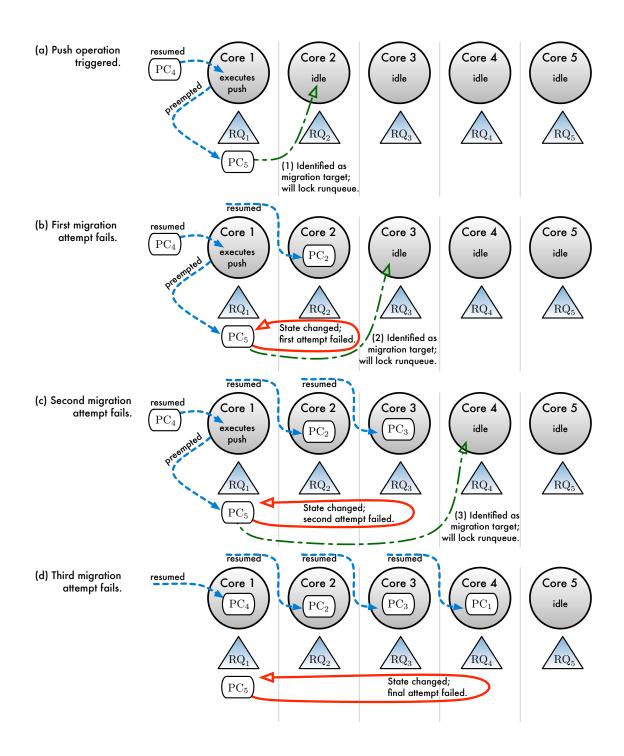

| 3.2  | Required migration missed by Linux's push operation                      | 178 |

| 3.3  | The structure of LITMUS <sup>RT</sup>                                    | 183 |

| 3.4  | Eager and lazy preemptions                                               | 199 |

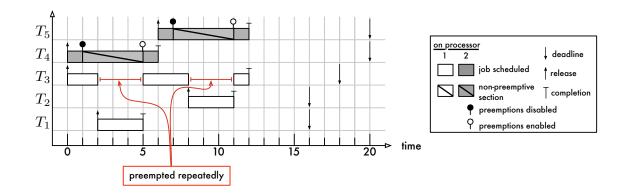

| 3.5  | Repeated, eagerly enacted preemptions                                    | 200 |

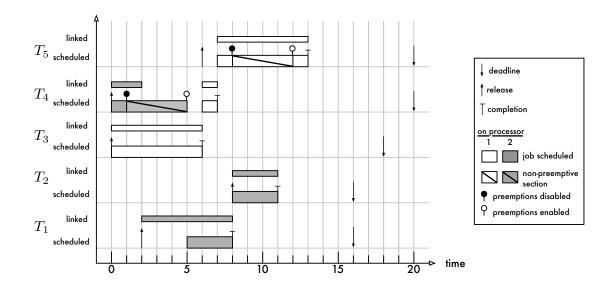

| 3.6  | O(1) pi-blocking under link-based scheduling                             | 205 |

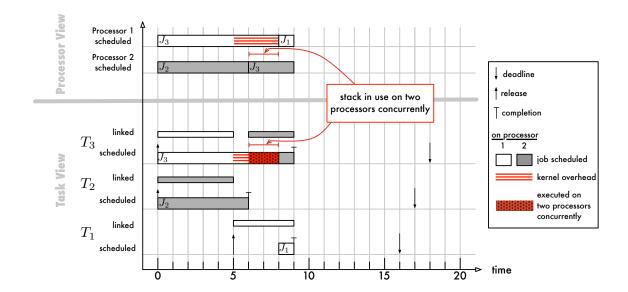

| 3.7  | Stack corruption due to migration races                                  | 208 |

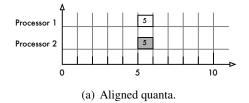

| 3.8  | Aligned and staggered quanta                                             | 218 |

| 3.9  | Release delay under global event-driven scheduling                       | 223 |

| 3.10 | Release delay under partitioned event-driven scheduling                  | 227 |

| 3.11 | Release delay under event-driven scheduling with non-preemptive sections    | . 228 |

|------|-----------------------------------------------------------------------------|-------|

| 3.12 | Uniprocessor EDF schedules with preemption overheads                        | . 231 |

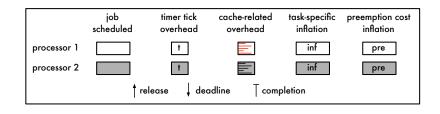

| 3.13 | G-EDF schedules with preemption and migration overheads                     | . 234 |

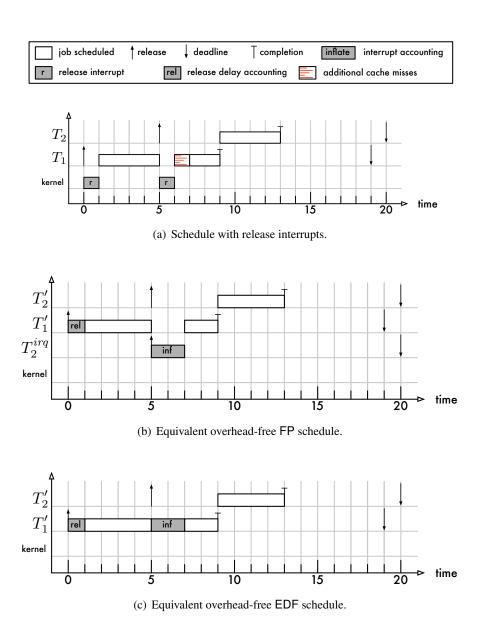

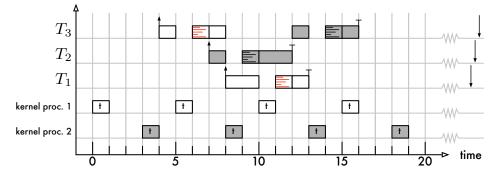

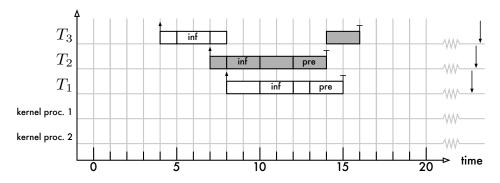

| 3.14 | Interrupt delay accounting techniques                                       | . 238 |

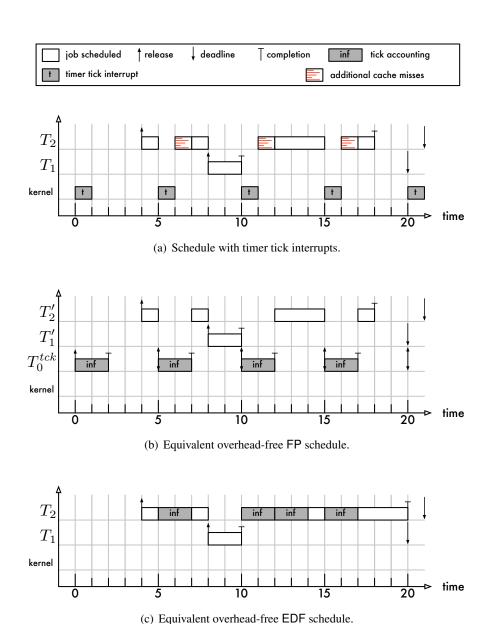

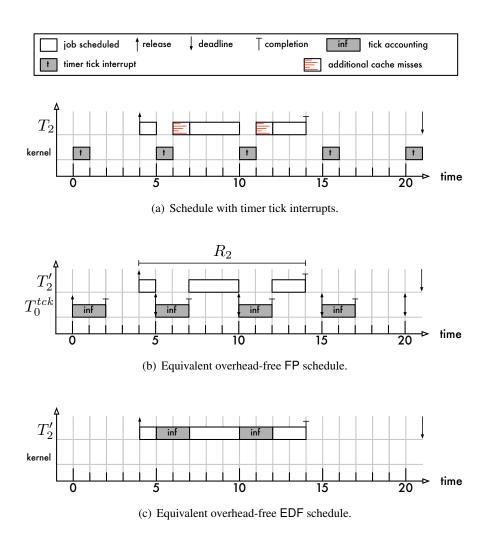

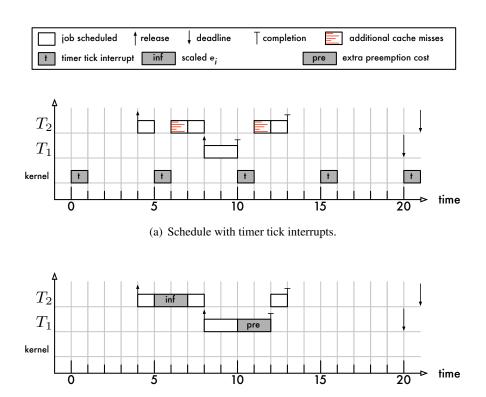

| 3.15 | Timer tick delay accounting techniques                                      | . 243 |

| 3.16 | Timer tick overhead in jobs that are not preempted                          | . 245 |

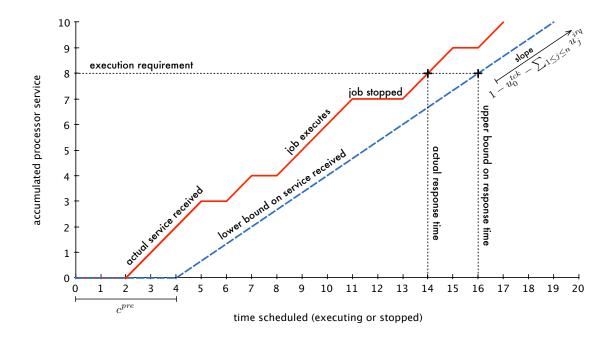

| 3.17 | Response-time bound for preemption-centric interrupt accounting             | . 252 |

| 3.18 | Preemption-centric timer tick delay accounting                              | . 256 |

| 3.19 | Preemption-centric interrupt accounting in the presence of migrations       | . 258 |

| 3.20 | Release delay under quantum-driven scheduling                               | . 265 |

| 3.21 | Effective quantum length                                                    | . 267 |

| 4.1  | Overhead-aware evaluation method                                            | 277   |

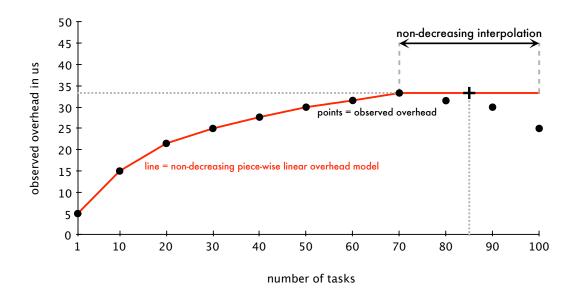

| 4.2  | Piece-wise linear overhead model                                            |       |

| 4.3  | Non-decreasing overhead interpolation                                       |       |

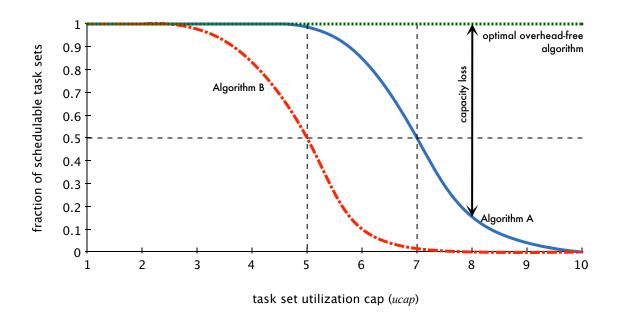

| 4.4  | Schedulability plot illustration                                            |       |

| 4.5  | Weighted schedulability plot illustration                                   |       |

| 4.6  | Statistical outlier in overhead measurement                                 |       |

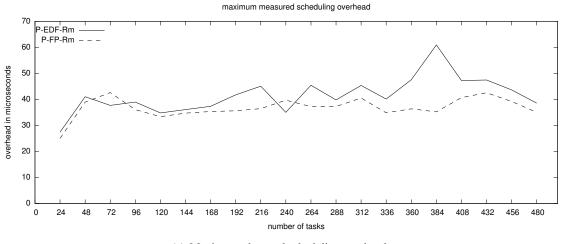

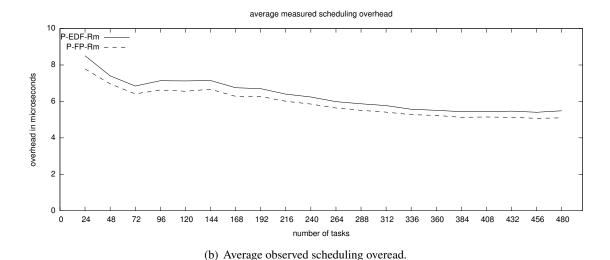

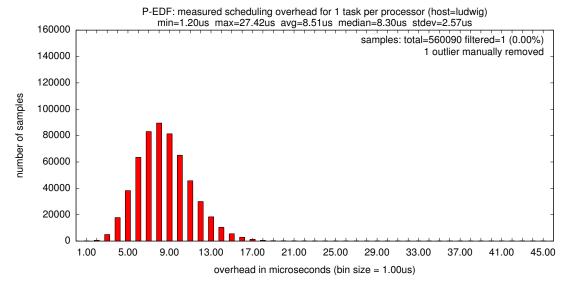

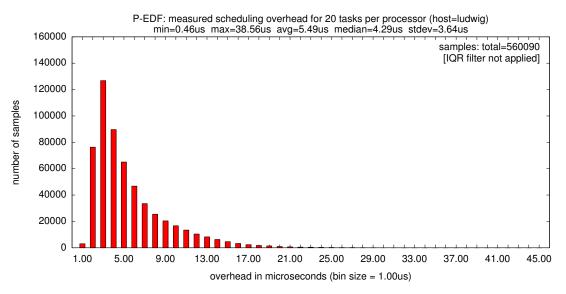

| 4.7  | Scheduling overhead under P-FP and P-EDF                                    |       |

| 4.8  | Distribution of scheduling overhead under P-EDF for $n=20$ and $n=480$      |       |

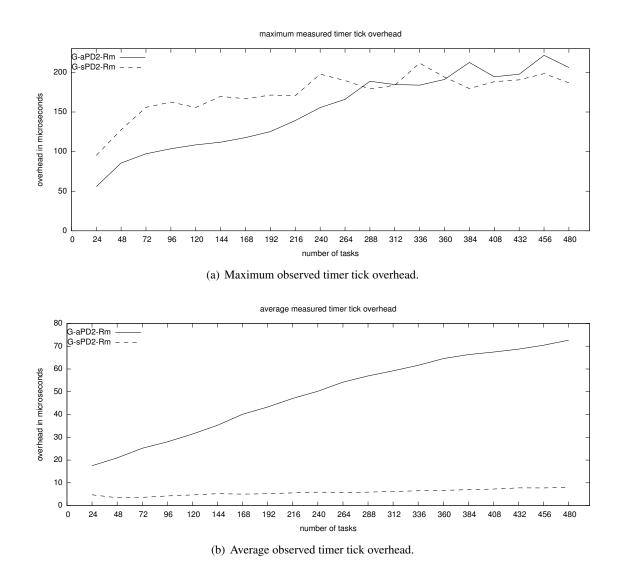

| 4.9  | Timer tick overhead under PD <sup>2</sup> with staggered and aligned quanta |       |

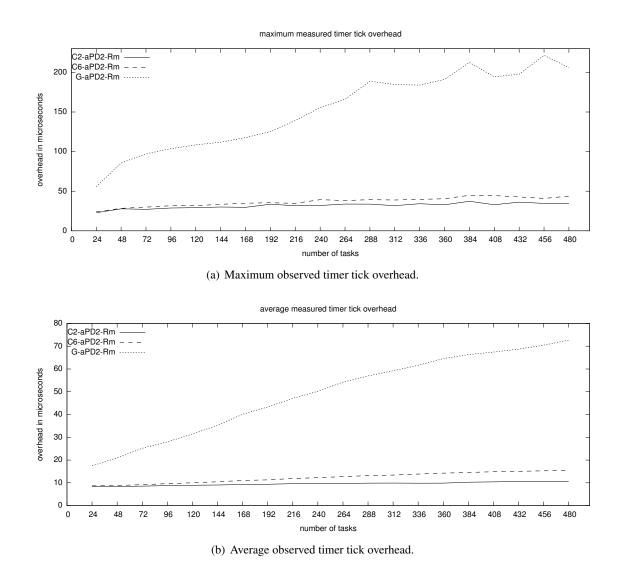

|      | Timer tick overhead under $PD^2$ and three cluster sizes                    |       |

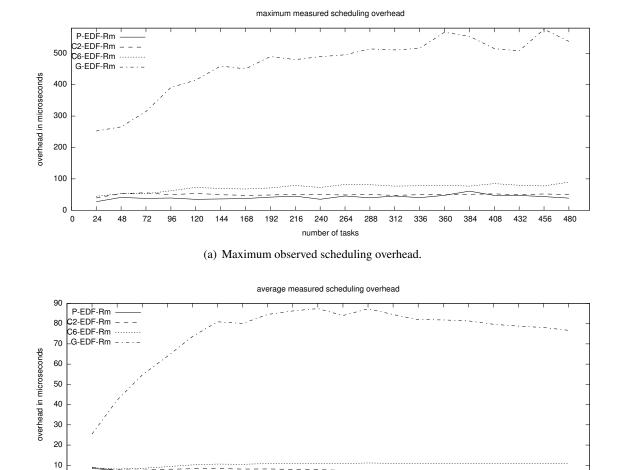

|      | Scheduling overhead under P-EDF, C-EDF, and G-EDF                           |       |

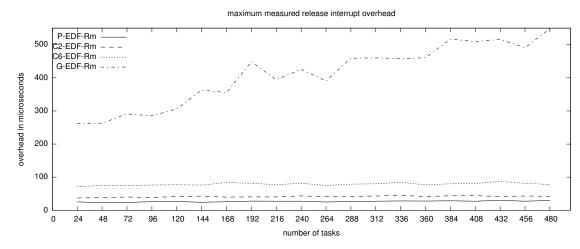

|      | Release interrupt overhead under P-EDF, C-EDF, and G-EDF                    |       |

|      | Tick and release interrupt overhead under C-PD <sup>2</sup> and C-EDF       |       |

|      | CPMD measurement approach                                                   |       |

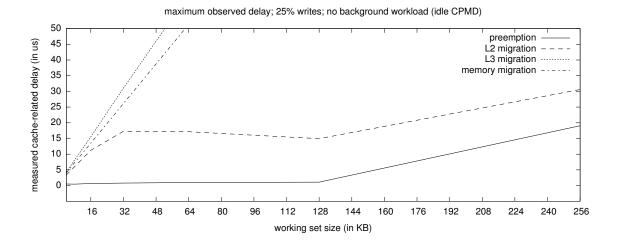

|      | Maximum and average observed CPMD in an idle system                         |       |

|      | Maximum observed CPMD in an idle system                                     |       |

|      | Transmission Court for CI 1/12 III will 1010 U JUNUIII                      | 0     |

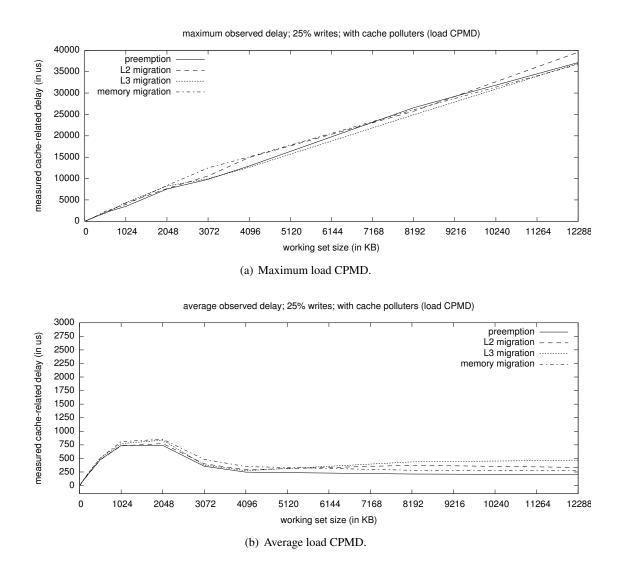

| 4.17 | Maximum and average observed CPMD in the presence of cache-polluting background tasks                               | . 328 |

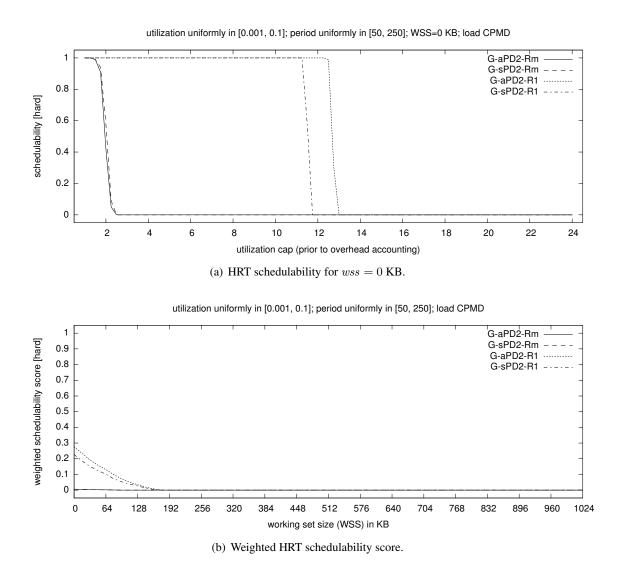

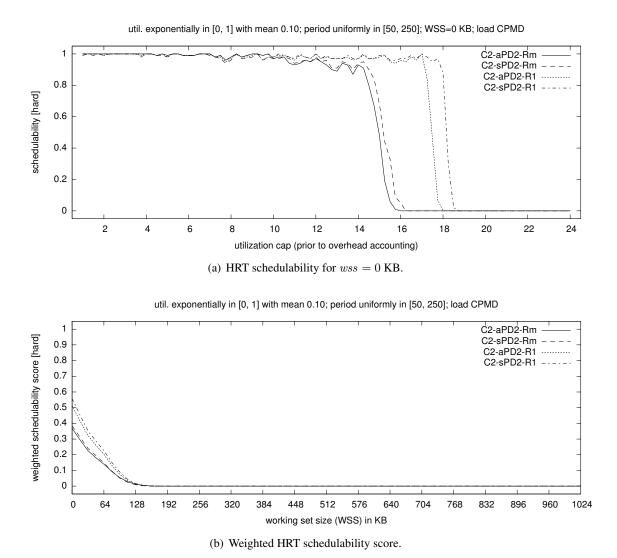

|------|---------------------------------------------------------------------------------------------------------------------|-------|

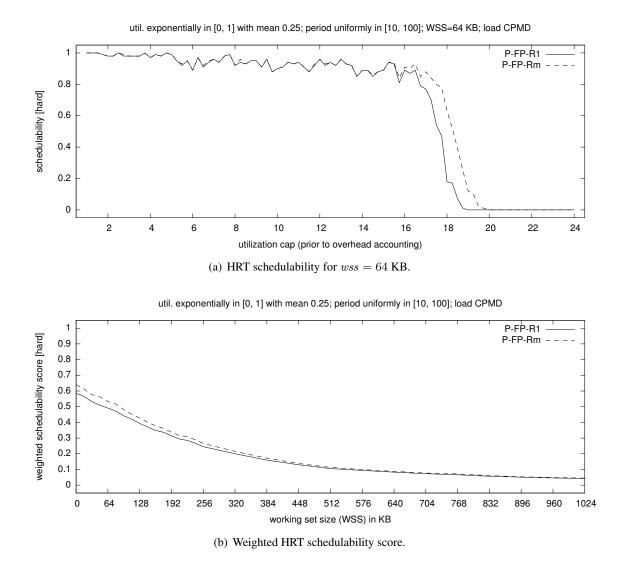

| 4.18 | P-FP HRT schedulability under global and dedicated interrupt handling                                               | 335   |

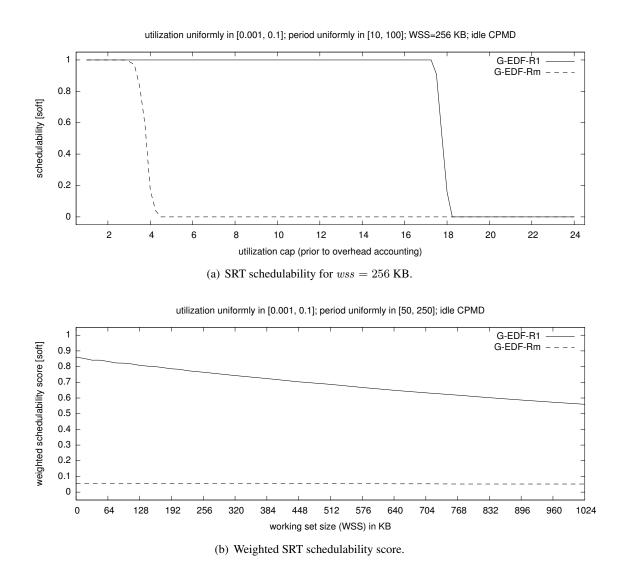

| 4.19 | G-EDF SRT schedulability under global and dedicated interrupt handling                                              | 337   |

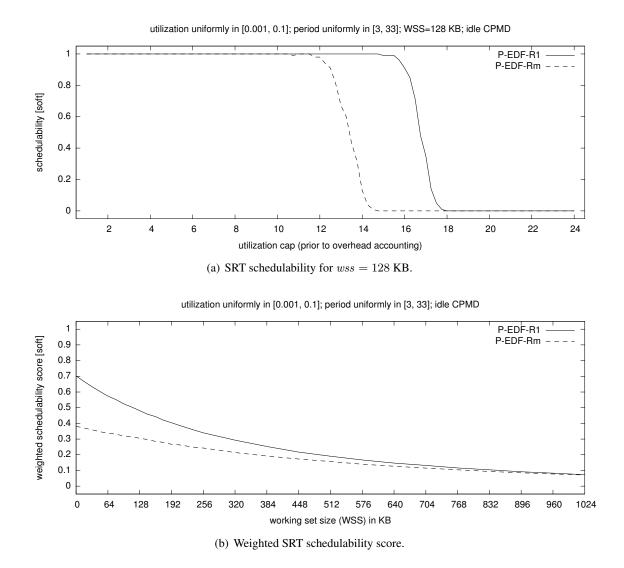

| 4.20 | P-EDF SRT schedulability under global and dedicated interrupt handling                                              | 339   |

| 4.21 | P-EDF HRT schedulability under global and dedicated interrupt handling                                              | 340   |

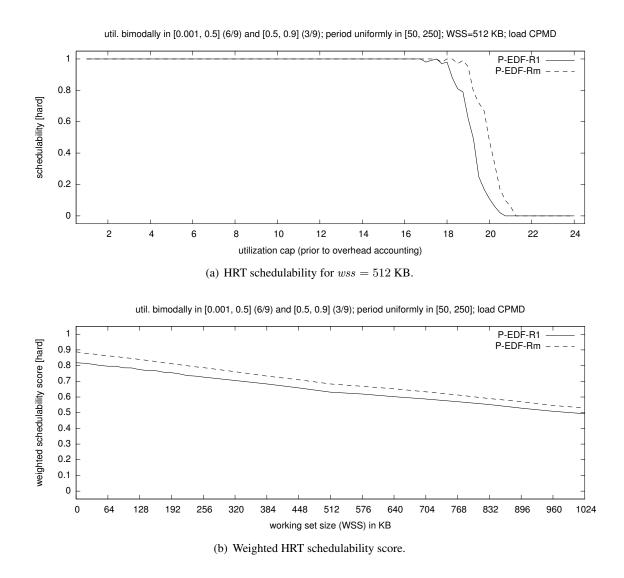

| 4.22 | $PD^2$ HRT schedulability under global and dedicated interrupt handling and staggered and aligned quanta for $c=24$ | . 342 |

| 4.23 | $PD^2$ HRT schedulability under global and dedicated interrupt handling and staggered and aligned quanta for $c=2$  | . 343 |

| 4.24 | C-PD <sup>2</sup> SRT schedulability under global and dedicated interrupt handling and staggered and aligned quanta | 345   |

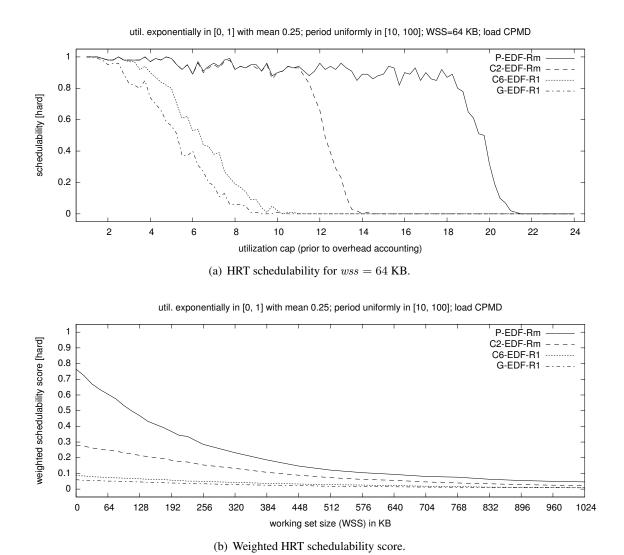

| 4.25 | Comparison of C-EDF cluster sizes in terms of HRT schedulability                                                    | 347   |

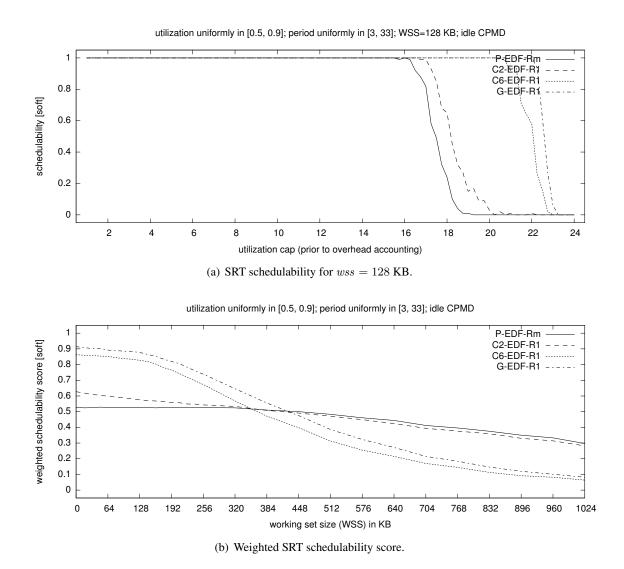

| 4.26 | Comparison of C-EDF cluster sizes in terms of SRT schedulability                                                    | 349   |

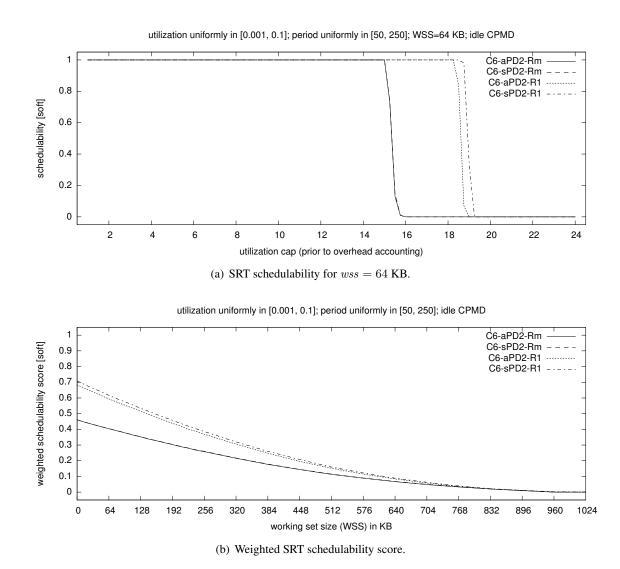

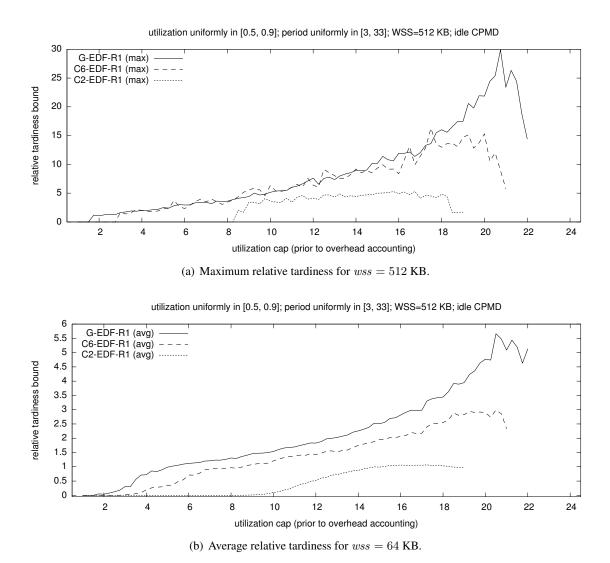

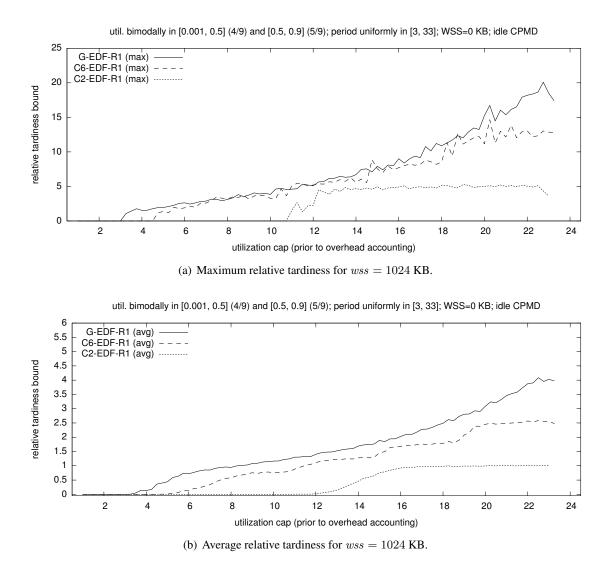

| 4.27 | Relative tardiness under EDF-based schedulers for uniform heavy utilizations and short periods                      | 351   |

| 4.28 | Comparison of PD <sup>2</sup> cluster sizes in terms of HRT schedulability                                          | 354   |

| 4.29 | Comparison of PD <sup>2</sup> cluster sizes in terms of SRT schedulability                                          | 355   |

| 4.30 | HRT schedulability under P-FP-Rm, P-EDF-Rm, and C6-aPD <sup>2</sup> -R1                                             | 358   |

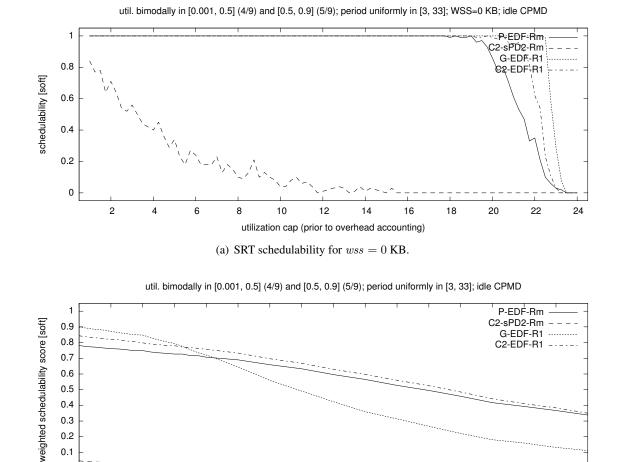

| 4.31 | SRT schedulability under P-EDF-Rm, C2-EDF-R1, G-EDF-R1, and C2-sPD <sup>2</sup> -Rm                                 | 360   |

| 4.32 | SRT schedulability under P-EDF-Rm, C2-EDF-R1, G-EDF-R1, and C2-sPD <sup>2</sup> -Rm                                 | 362   |

| 4.33 | Relative tardiness under EDF-based schedulers for heavy bimodal utilizations and short periods                      | . 363 |

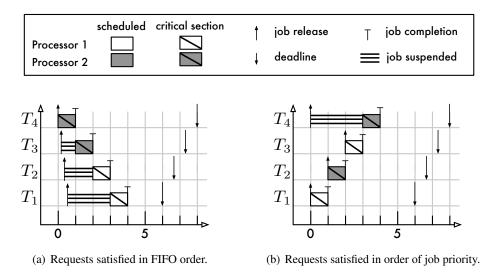

| 5.1  | Unnecessary sequencing of readers in task-fair mutex spinlocks                                                      | . 378 |

| 5.2  | Reader parallelism (and lack thereof) under task-fair RW locks                                                      | . 379 |

| 5.3  | Reader delay under writer preference locks                                                                          | 381   |

| 5.4  | Reduced delay under phase-fair RW locks                                                                             | 382   |

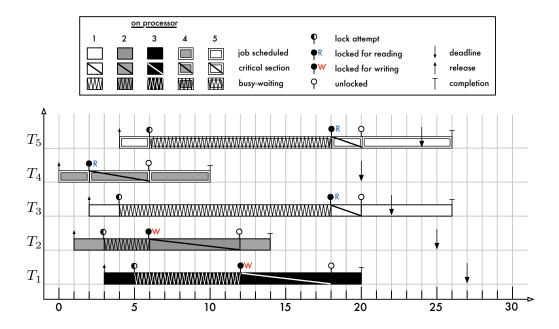

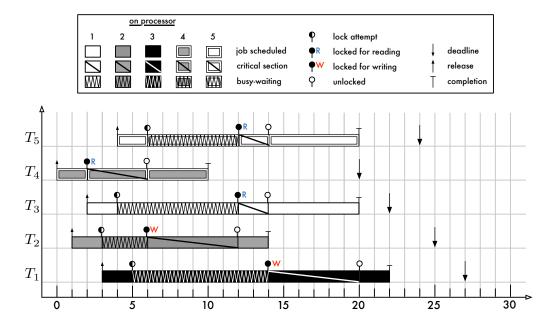

| 5.5  | Reader and writer control flow in the PF-T algorithm                                                                | 389   |

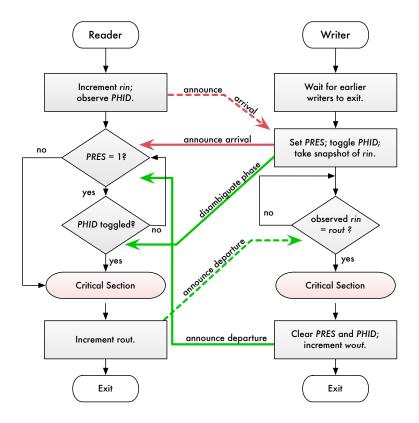

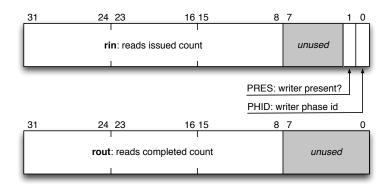

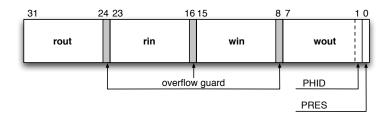

| 5.6  | Allocation of bits in PF-T locks.                                                                                   | 390   |

| 5.7        | Allocation of bits in PF-C locks                                                    | . 392 |

|------------|-------------------------------------------------------------------------------------|-------|

| 5.8        | Maximum number of jobs pending during an interval of fixed length                   | . 407 |

| 5.9        | Minimum reader parallelism                                                          | . 413 |

| <i>c</i> 1 |                                                                                     | 105   |

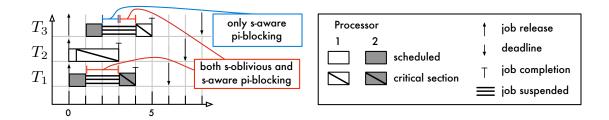

| 6.1        | S-oblivious and s-aware pi-blocking                                                 |       |

| 6.2        | Lower bound on s-oblivious pi-blocking                                              |       |

| 6.3        | Lower bound on s-aware pi-blocking                                                  | . 428 |

| 6.4        | Lower bound on s-oblivious pi-blocking due to priority boosting if $c>1$            | . 431 |

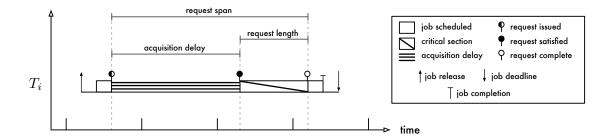

| 6.5        | Request phases under priority donation                                              | . 433 |

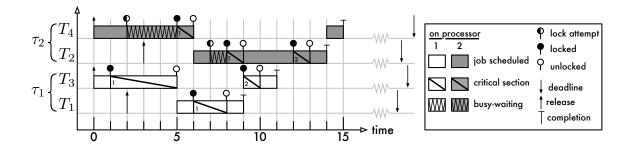

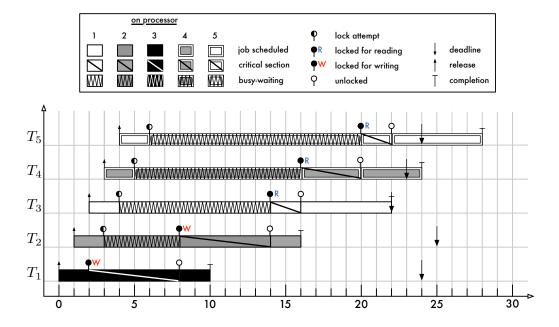

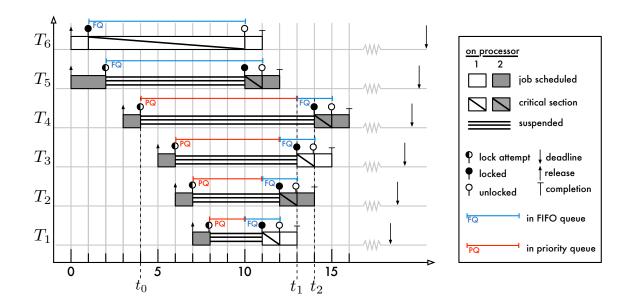

| 6.6        | Clustered mutex OMLP schedule                                                       | . 435 |

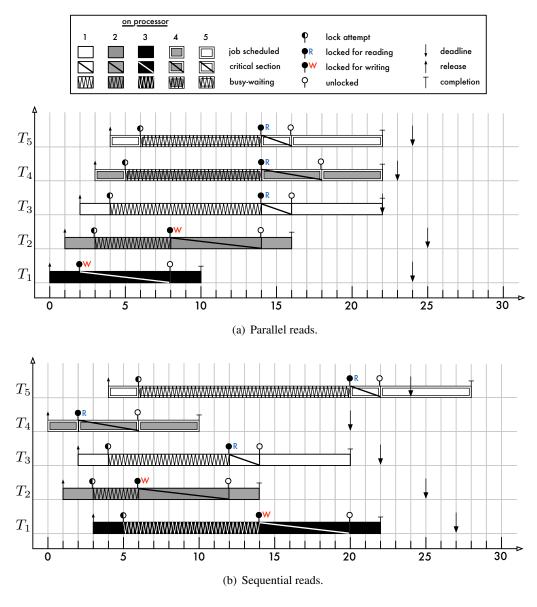

| 6.7        | Clustered RW OMLP schedule                                                          | . 441 |

| 6.8        | Clustered k-exclusion OMLP schedule                                                 | . 444 |

| 6.9        | Pi-blocking of independent jobs if $c < m$                                          | . 447 |

| 6.10       | Lower bound on s-oblivious pi-blocking in FIFO- and priority-ordered queues         | . 448 |

| 6.11       | Global OMLP schedule                                                                | . 450 |

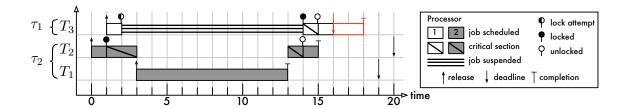

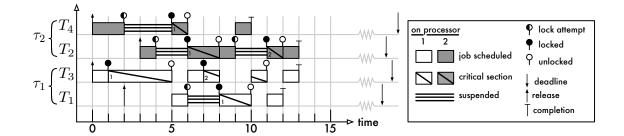

| 6.12       | Partitioned FMLP <sup>+</sup> schedule                                              | . 459 |

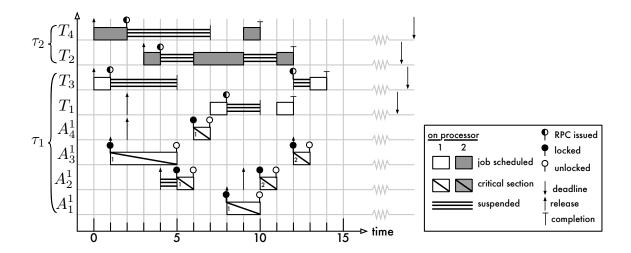

| 6.13       | $\Omega(\phi)$ s-aware pi-blocking under G-EDF scheduling with priority inheritance | . 465 |

| 6.14       | $\Omega(\phi)$ s-aware pi-blocking under G-EDF scheduling with priority boosting    | . 468 |

| 6.15       | Lower bound on s-aware pi-blocking if requests are satisfied in priority order      | . 470 |

| 7.1        | Transitive interrupt delays                                                         | . 490 |

| 7.2        | Pi-blocking due to remote ISR execution                                             | . 491 |

| 7.3        | Locking overheads in non-preemptive spinlock protocols                              | . 493 |

| 7.4        | Locking overheads in non-preemptive semaphore protocols                             | . 496 |

| 7.5        | Additional CPMD incurred by lower-priority jobs                                     | . 499 |

| 7.6        | Additional preemption overheads in preemptive semaphore protocols                   | . 503 |

| 7.7        | DPCP locking overheads                                                              | . 505 |

| 7.8        | Three scheduler invocations due to agent activation                                 | . 506 |

| 7.9        | Average critical section length grouped by spinlock type                            | . 512 |

| 7.10 | Average critical section length grouped by implementation technique                                                 | 513   |

|------|---------------------------------------------------------------------------------------------------------------------|-------|

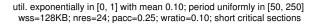

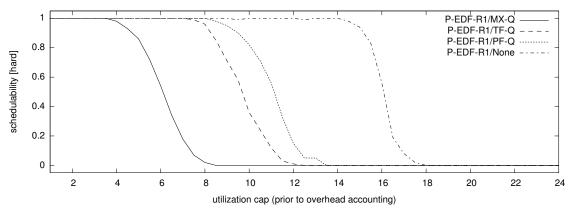

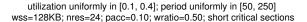

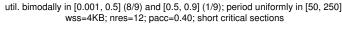

| 7.11 | HRT schedulability under P-EDF-R1 with MX-Q, TF-Q, and PF-Q spinlocks for $wratio=0.1$                              | 519   |

| 7.12 | HRT schedulability under P-EDF-R1 with MX-Q, TF-Q, and PF-Q spinlocks for $wratio=0.5$                              | 520   |

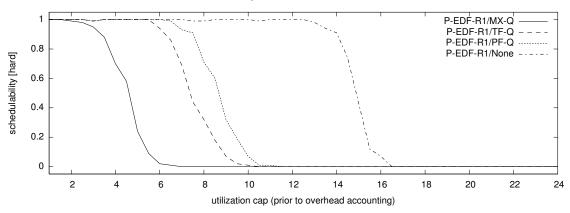

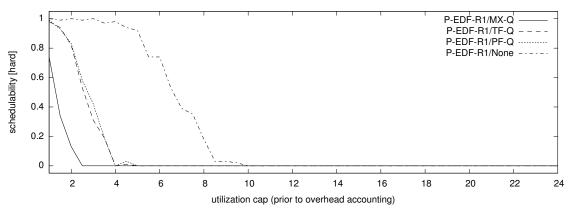

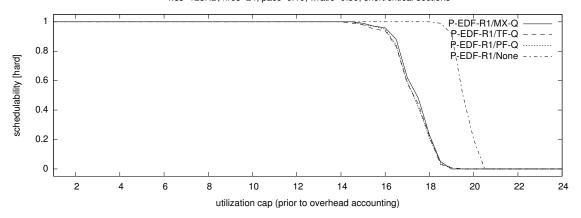

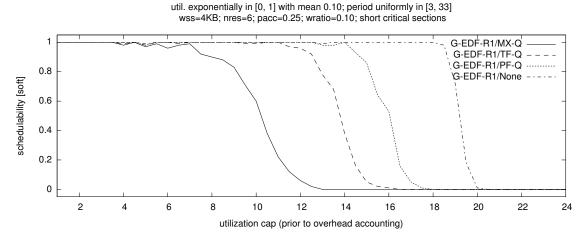

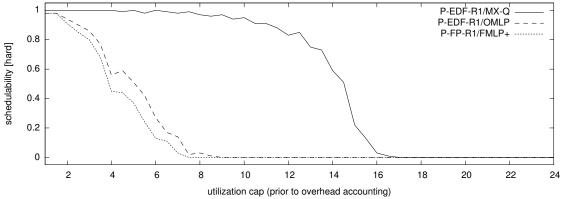

| 7.13 | SRT schedulability under G-EDF-R1 with MX-Q, TF-Q, and PF-Q spin-locks for $wratio=0.1$                             | . 522 |

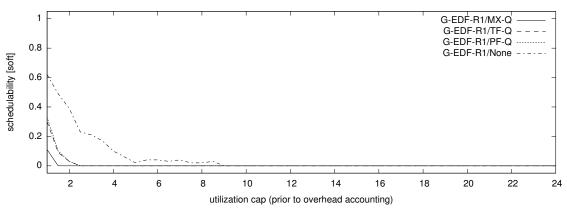

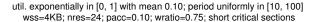

| 7.14 | SRT schedulability under G-EDF-R1 with MX-Q, TF-Q, and PF-Q spin-locks for $wratio=0.75$                            | . 523 |

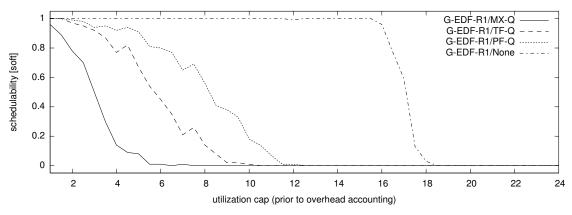

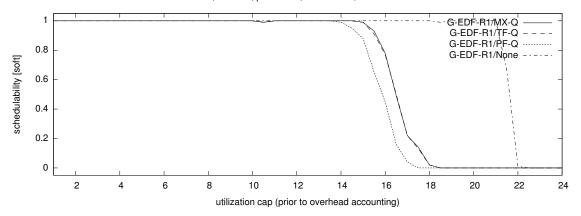

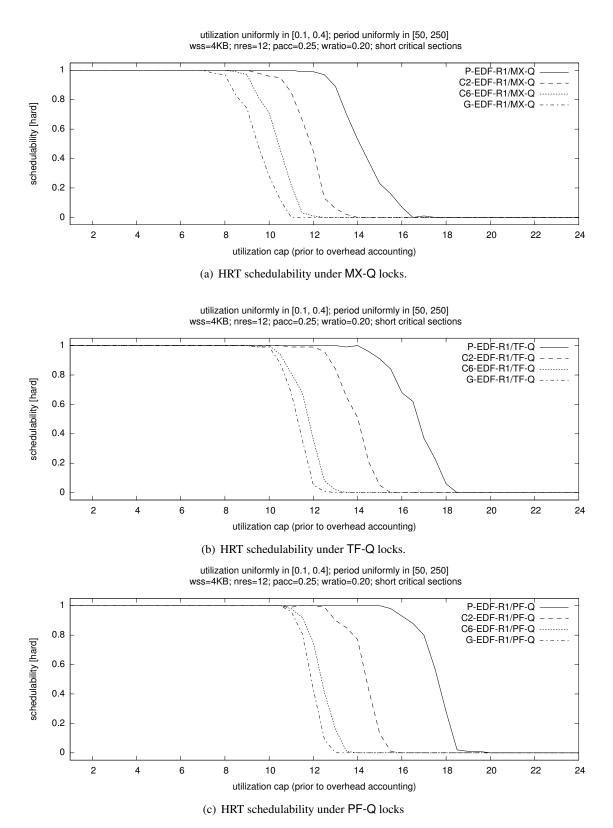

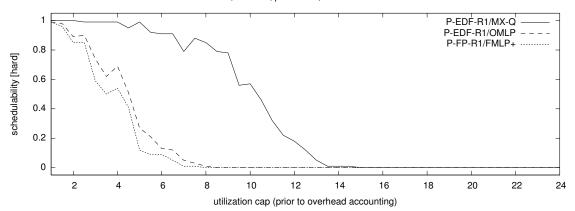

| 7.15 | HRT schedulability under P-EDF-R1, C2-EDF-R1, C6-EDF-R1, and G-EDF-R1 with MX-Q, TF-Q, and PF-Q spinlocks           | . 525 |

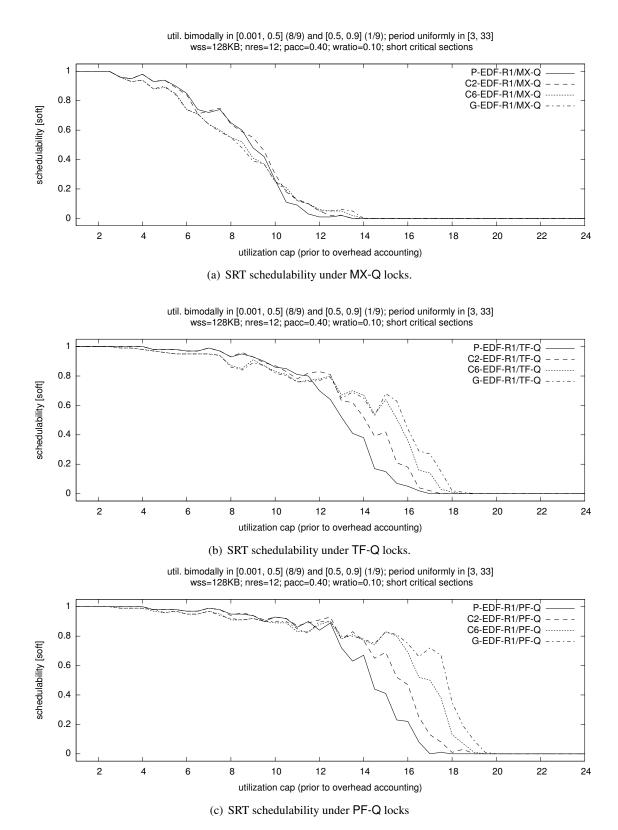

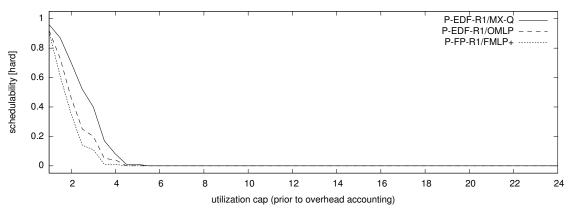

| 7.16 | SRT schedulability under P-EDF-R1, C2-EDF-R1, C6-EDF-R1, and G-EDF-R1 with MX-Q, TF-Q, and PF-Q spinlocks           | . 526 |

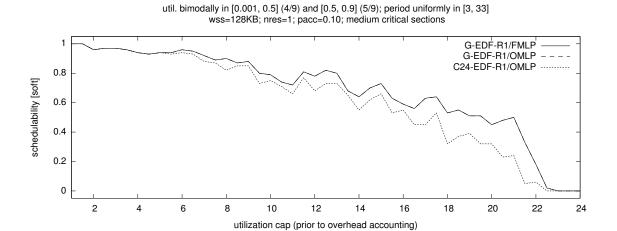

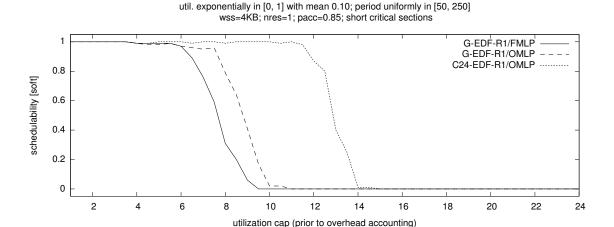

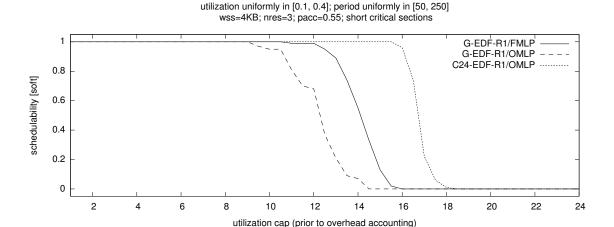

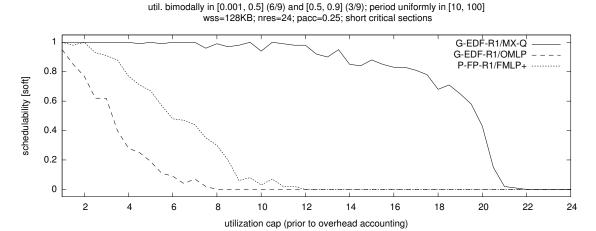

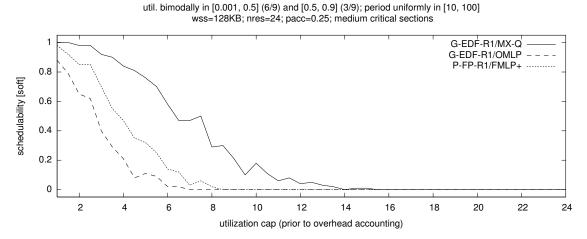

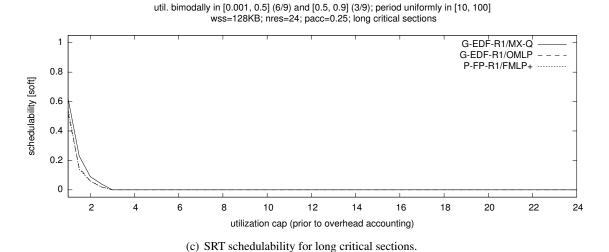

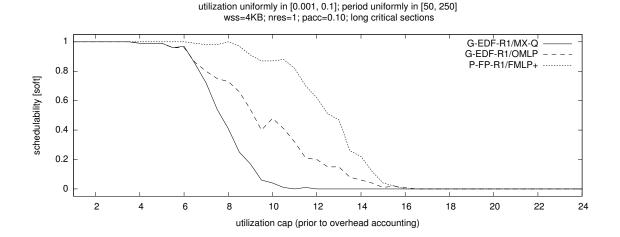

| 7.17 | SRT schedulability under the global OMLP, global FMLP, and the clustered OMLP                                       | . 529 |

| 7.18 | SRT schedulability under the global OMLP, global FMLP, and the clustered OMLP in the case of high contention        | 530   |

| 7.19 | Lower SRT schedulability under the global OMLP than under the global FMLP                                           | 531   |

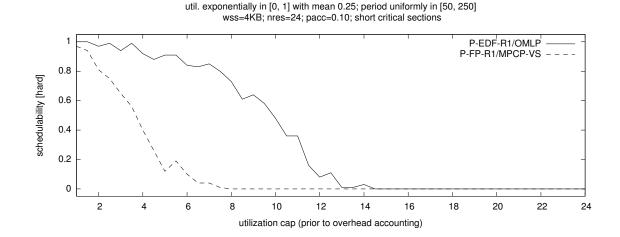

| 7.20 | HRT schedulability under P-EDF with the clustered OMLP and under P-FP with the MPCP-VS                              | . 532 |

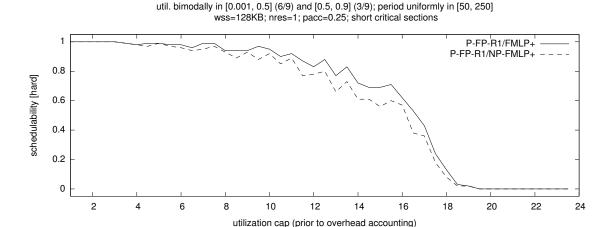

| 7.21 | HRT schedulability under P-FP-R1 scheduling with two variants of the FMLP <sup>+</sup>                              | 535   |

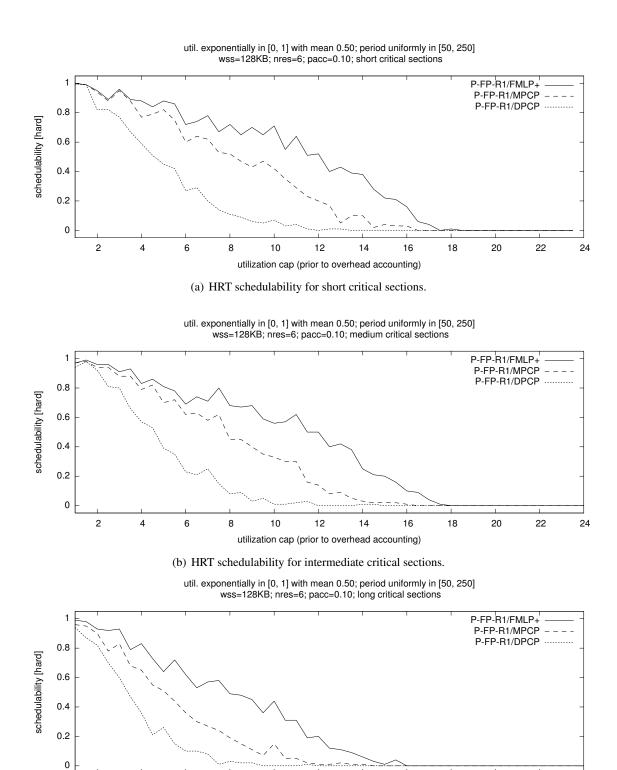

| 7.22 | HRT schedulability under P-FP-R1 scheduling with the FMLP <sup>+</sup> , the MPCP, and the DPCP                     | . 537 |

| 7.23 | Lower SRT schedulability under the FMLP <sup>+</sup> than under the DPCP                                            | 538   |

| 7.24 | HRT Schedulability under suspension- and spin-based locking protocols                                               | 540   |

| 7.25 | SRT Schedulability under suspension- and spin-based locking protocols                                               | 542   |

| 7.26 | Lower SRT schedulability under non-preemptive task-fair mutex spinlocks than under the preemptive FMLP <sup>+</sup> | 543   |

# LIST OF ABBREVIATIONS

ACPI Advanced Configuration and Power Interface

ACPI PM ACPI Power Management

APIC Advanced Programmable Interrupt Controller

API Application Programming Interface

ASN Address Space Number

C-EDF Clustered Earliest-Deadline First

C-PD<sup>2</sup> Clustered PD<sup>2</sup>

CFS Completely Fair Scheduler

COTS Components Of The Shelf

CPMD Cache-related Preemption and Migration Delay

CSI Cycle-Stealing Interrupt

DI Device Interrupt

DM Deadline-Monotonic

DPCP Distributed Priority-Ceiling Protocol

DSP Digital Signal Processor

ECU Engine Control Unit

EDF Earliest-Deadline First

EOI End Of Interrupt

ERfair Early-Release fair

ESP Electronic Stability Program

FDSO File-Descriptor-attached Shared Object

FIFO First-In First-Out

FMLP<sup>+</sup> Flexible Multiprocessor Locking Protocol (improved)

FMLP Flexible Multiprocessor Locking Protocol

FPU Floating Point Unit

FP Fixed-Priority

G-EDF Global Earliest-Deadline First

G-FP Global Fixed-Priority

GPOS General-Purpose Operating System

GPS Global Positioning System

GPU Graphics Processing Unit

GUI Graphical User Interface

HPET High-Precision Event Timer

HRT Hard Real-Time

HW Hardware

I/O Input/Output

IPC Inter-Process Communication

IPI Inter-Processor Interrupt

IQR Inter-Quartile Range

ISA Instruction Set Architecture

ISR Interrupt Service Routine

JLDP Job-Level Dynamic-Priority

JLFP Job-Level Fixed-Priority

LDID Logical Destination ID

LKM Loadable Kernel Module

MMU Memory Management Unit

MPCP-VS Multiprocessor Priority-Ceiling Protocol with Virtual Spinning

MPCP Multiprocessor Priority-Ceiling Protocol

MSRP Multiprocessor Stack Resource Policy

NCP Non-preemptive Critical section Protocol

NMI Non-Maskable Interrupt

NP-FMLP<sup>+</sup> Non-preemptive Flexible Multiprocessor Locking Protocol (improved)

NUMA Non-Uniform Memory Access

OMLP O(m) Locking Protocol

OS Operating System

P-EDF Partitioned Earliest-Deadline First

P-FP Partitioned Fixed-Priority

PCB Process Control Block

PCP Priority-Ceiling Protocol

pi-blocking Priority Inversion blocking

PIC Programmable Interrupt Controller

PIP Priority Inheritance Protocol

PIT Programmable Interval Timer

PS Fluid Processor Sharing

RMR Remote Memory Reference

RM Rate-Monotonic

RPC Remote Procedure Call

RTOS Real-Time Operating System

RW Reader-Writer

s-aware Suspension-aware

s-blocking Spin blocking

s-oblivious Suspension-oblivious

SMI System Management Interrupt

SMM System Management Mode

SMP Symmetric Multiprocessor

SRP Stack Resource Policy

SRT Soft Real-Time

TI Timer Interrupt

TLB Translation Look-aside Buffer

TPR Task Priority Register

TSC Timestamp Counter

UMA Uniform Memory Access

WCET Worst-Case Execution Time

WSS Working Set Size

## **CHAPTER 1**

# INTRODUCTION

With the recent advent of multicore chips, multiprocessors are now commonly encountered in servers, personal computers, and embedded systems (Sodan *et al.*, 2010). As a result, real-time applications—that is, applications that must satisfy temporal constraints in order to be deemed correct—are increasingly being deployed on multiprocessors (Baker, 2010). One reason for the proliferation of multicore platforms in real-time systems is that such platforms have come to constitute a significant share of the cost-efficient *components-of-the-shelf* (COTS) market (Child, 2010). Another important factor is their considerable processing capacity, which makes them an attractive choice for hosting compute-intensive tasks such as high-definition video stream processing, object recognition and tracking, and computer vision applications in general.

For example, Villalpando *et al.* (2010) evaluated Tilera's 64-core TILE64 processor (Bell *et al.*, 2008) for use in the real-time hazard detection and avoidance system of the Altair Lunar Lander (NASA, 2008). They found "that for [computer vision and image analysis] the TILE64 architecture provides excellent performance," and further recommended the platform for other onboard tasks, including spacecraft and instrument control (Villalpando *et al.*, 2010). Notably, a radiation-hardened 49-core version of the TILE64 processor, named Maestro, has been developed with the explicit purpose of enabling space-born, embedded multicore real-time systems (Malone, 2009; Crago, 2009).

Many real-time applications can be decomposed into a collection of recurrent *tasks*. The goal of this dissertation is to determine how such tasks should be supported at the operating-system level. In particular, the research presented herein is focused on two questions fundamental to the design of multiprocessor real-time operating systems (RTOSs):

Q1 Which scheduling policies offer the greatest flexibility in satisfying temporal constraints?

Q2 Which synchronization techniques should be used to enable tasks to access shared resources (such as message buffers and I/O devices) without incurring unpredictable delays?

To motivate our research, we begin by illustrating the need for predictable and efficient multicore RTOSs with two examples.

# 1.1 The Cost of Over-Provisioning

Temporal constraints naturally arise whenever computers interact with the "real world." In particular, this is the case when computers control or observe physical processes, or when human users perceive a device's reaction as slow or delayed. Real-time constraints are commonly classified as either *hard* or *soft*, with the interpretation that hard real-time (HRT) constraints must always be met, whereas violations are tolerable to a limited extent in the soft real-time (SRT) case.

An example of the former is the *electronic stability control* (or *program*, ESP) deployed in modern cars (Liebemann *et al.*, 2004). The purpose of ESP is to prevent roll-over accidents by correcting driver errors such as exaggerated steering during panic reactions. This is achieved by applying corrective forces to individual wheels when a dangerous level of lateral acceleration is detected (Liebemann *et al.*, 2004). HRT constraints are fundamental to ESP because a delay in the sensing of the current acceleration or enactment of appropriate corrections can have catastrophic consequences. Anti-lock brakes and traction control are subject to similar constraints.

In contrast, an unresponsive *graphical user interface* (GUI) usually does not have catastrophic consequences, but results in unsatisfied customers nonetheless. A recent consumer review of HP's TouchSmart interface criticized that "the [TouchSmart interface] is simply too sluggish for everyday use" (Stern, 2010). Barnes & Noble's Nook e-book reader was disparaged similarly (Topolsky, 2010). The underlying failure in both cases is that the user interface did not respond in time—while not safety-critical, noticeable graphics or audio glitches can spell financial disaster for manufacturers of consumer electronics. Similar arguments apply to popular multimedia features such as video playback and interactive games.

To impose minimum levels of predictability in safety-critical applications, governments have instituted certification authorities such as the U.S. Federal Aviation Authority (FAA) and the National Highway Traffic Safety Administration (NHTSA). A key requirement is isolation—the failure of one

subsystem should not affect the correct operation of other components. The easiest and historically most-commonly used way to ensure isolation is to employ a dedicated processor for each functionality. However, this approach has led to an increasingly unmanageable proliferation of such systems, to the effect that some modern cars contain in excess of one hundred processors (Hergenhan and Heiser, 2008). Unsurprisingly, there are strong market forces and design imperatives that require engineers to curb this spread of embedded processors: not only does the overall system complexity (and thus cost) grow with each added component, but every embedded system requires wiring and cooling, adds weight, requires space, drains power, and must be purchased, transported, stored, tested, documented, serviced, eventually replaced, and finally recycled. Thus, instead of embedding one hundred networked, slow uniprocessors throughout a car, it would be desirable to use only ten (or fewer) shared, but ten-times as powerful, multicore processors that are highly utilized.

Over-provisioning GUIs and other soft real-time applications with faster-than-necessary processors is similarly costly, and especially so in the highly competitive mobile sector (*e.g.*, smart phones and tablets), which is subject to stringent energy, cooling, and cost constraints. There are thus strong incentives to "do more with less": an increasing number of real-time tasks need to share limited physical resources on multiprocessors without compromising predictability or efficiency.

# 1.2 The Divergence of Theory and Practice

A solid RTOS foundation is thus required to fully exploit the promise of multicore technology for real-time applications. Unfortunately, the existing foundation appears increasingly insufficient, as most RTOSs in common use today still rely on approaches rooted in decades-old uniprocessor design concepts.<sup>1</sup> Motivated by these developments, research on multiprocessor real-time systems has surged in recent years and many algorithmic advances have been made. Unfortunately, these results have found only little adoption in practice.

We briefly digress to introduce needed background before discussing the current state of affairs.

### 1.2.1 Background

Each of the concepts mentioned in the remainder of this chapter is discussed in detail in Chapter 2.

<sup>&</sup>lt;sup>1</sup>See Section 2.5 for a discussion of relevant RTOSs.

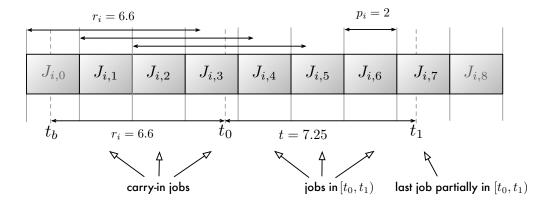

One particularly well-studied abstraction of recurrent real-time activity is the *sporadic task model*. When such a task is triggered by an (external) event such as an interrupt, it releases a sequential *job* to process the triggering event. Each job has a *deadline* by which it should complete. In this section, we restrict our discussion to *implicit deadlines*, where a job's deadline also marks the earliest-possible release time of the next job (of the same task). A task's *utilization* is the fraction of one processor's capacity that must be reserved for it. Similarly, the *total utilization* of a task set is simply the sum of all utilizations of tasks in the set.

From an RTOS point of view, the sporadic task model is a good compromise between practicality and expressiveness. It is easy to implement, well-analyzed, and can represent both cyclic tasks such as ESP and video decoding as well as event-driven tasks such as GUI applications. To avoid confusion, we use the term "task" to refer to a sporadic task on the model level and let "process" denote the OS-level concept of a sequential thread of control. A sporadic task is typically implemented as a process that executes an infinite loop, where each loop iteration corresponds to one job.

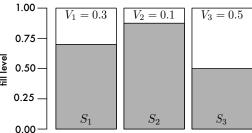

Temporal correctness. A task set is *schedulable* if it can be shown that each task meets its timing constraints. A procedure that establishes whether a task set is schedulable under a given scheduler is a *schedulability test*. In an HRT context, a sporadic task set is schedulable if each job meets its deadline (Liu and Layland, 1973). In contrast, some deadline misses are tolerable in SRT applications: a task set is SRT schedulable if *tardiness* is bounded, *i.e.*, if the magnitude of deadline misses does not exceed a (reasonably small) constant (Devi, 2006).<sup>2</sup> A task set is *feasible* if there exists *some* scheduling policy under which it is schedulable. For a task set to be feasible (either HRT or SRT) on *m* processors, its total utilization must not exceed *m*—unbounded deadline misses cannot be avoided if processors are overloaded. In the context of our discussion here, a scheduler can be considered *optimal* if any task set with total utilization at most *m* is schedulable (with regard to either HRT or SRT constraints, respectively; see Section 2.2.3 for a precise definition of scheduler optimality).

Capacity loss. To meet the design goal of maximum flexibility (recall Question Q1), an ideal RTOS should support any feasible task set. Given the above limit on total utilization (and our focus on implicit deadlines), this means that any task set with total utilization not exceeding the total processor capacity m should be schedulable. In practice, it is not possible to allocate all processor capacity to

<sup>&</sup>lt;sup>2</sup>Other notions of SRT constraints exist; see Section 2.2.2.

real-time tasks, *i.e.*, task systems with total utilization less than m may not be schedulable. Such capacity loss has two primary causes: the choice of scheduling policy and runtime overheads. With regard to the former, if the RTOS employs a non-optimal scheduling policy, then a feasible task set may not be schedulable due to algorithmic capacity loss. The latter, overhead-related capacity loss, is due to processor time that is consumed by hardware inefficiencies (e.g., cache misses) and system management activities (e.g., computing a scheduling decision). Such runtime overheads are unavoidable to some degree, but can differ significantly among schedulers and implementations. Time lost to system overheads must be accounted for when testing whether a task set is schedulable on a given platform, which reduces the amount of processor capacity effictively available to real-time tasks.

To minimize overall capacity loss, an RTOS should ideally use a scheduler that is both optimal and that incurs minimal overheads.

Uniprocessor real-time scheduling. The scheduling of sporadic tasks on uniprocessors is well understood. The two most-relevant scheduling policies are *fixed-priority* (FP) and *earliest-deadline first* (EDF) scheduling. Under FP scheduling, each task is statically assigned a unique priority prior to execution. At runtime, competing jobs are then scheduled in order of decreasing task priority. In contrast, under EDF scheduling, jobs are scheduled in order of increasing deadlines (*i.e.*, in order of urgency) and no manual priority assignment is required. In a classic result, Liu and Layland (1973) showed that, for HRT constraints, EDF is optimal, whereas FP is subject to algorithmic capacity loss (Liu and Layland, 1973). Since a task set that is HRT schedulable also has bounded tardiness, EDF is optimal in the SRT case as well.

Nonetheless, FP scheduling is much more common in practice. One likely reason is the relative ease of implementing FP efficiently (using a bitmask where each set bit indicates the presence of pending jobs at a corresponding priority level). While it is also possible to implement EDF efficiently (Short, 2010), the required techniques are conceptually more difficult and are not part of OS developer folklore (in contrast to FP implementation techniques, which are widely known). Buttazzo (2005) argued that the preference for FP is further reinforced by widespread misconceptions and myths concerning supposed advantages in practice (such as failure modes under transient overloads), which he conclusively debunked (Buttazzo, 2005). From a capacity-loss perspective, the pervasive

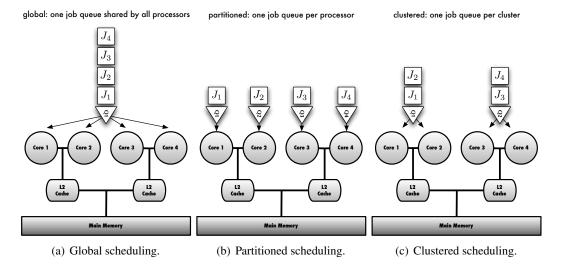

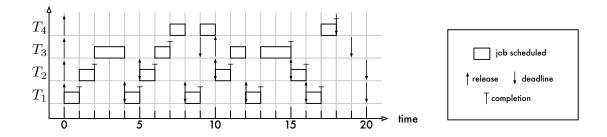

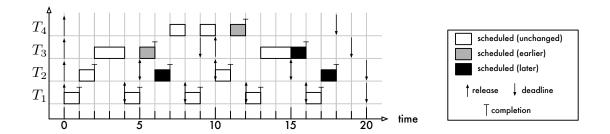

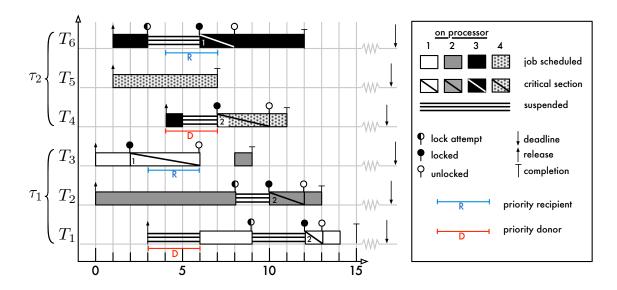

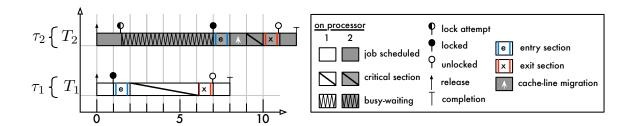

Figure 1.1: Illustration of multiprocessor scheduling approaches for four cores that share L2 caches in pairs of two. Note that L2 cache affinity is not lost when migrations occur under clustered scheduling. (See Section 2.1.2 for details.)

use of FP as the uniprocessor real-time scheduler of choice is thus not justified. Rather, it could be considered a historical accident—alas, one that has since been codified in the POSIX real-time standard (IEEE, 1993, 2003, 2008b), which mandates FP scheduling. (The POSIX standard does not prohibit additional schedulers, but few RTOSs supplement FP with other real-time schedulers such as EDF.)

#### 1.2.2 Multiprocessor Real-Time Scheduling

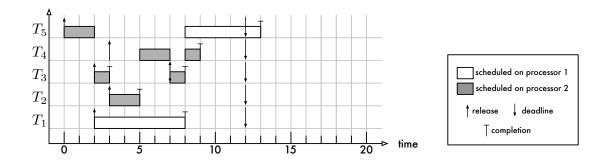

There are two fundamental classes of multiprocessor schedulers: *global* and *partitioned*. Under global scheduling (illustrated in inset (a) of Figure 1.1), all processors serve a single ready queue and jobs may migrate among processors. In contrast, under *partitioned* scheduling (illustrated in inset (b) of Figure 1.1), tasks are statically assigned to processors during an offline phase and each processor is scheduled individually using a uniprocessor policy such as EDF or FP.

There is a clear analytical answer to Question Q1: some global schedulers are *provably superior* to any partitioned approach. This is because partitioned scheduling requires tasks to be statically assigned to processors such that no processor is overloaded, which is equivalent to solving a bin-packing problem. As even an optimal packing may leave some bins incompletely filled (*i.e.*, some processors partially idle), there exist task sets with total utilization at most  $\frac{m+1}{2} + \epsilon$  that cannot be

partitioned onto m processors (Oh and Baker, 1998; Andersson et~al., 2001; Andersson and Jonsson, 2003), where  $\epsilon$  is an arbitrary small positive number. In other words, nearly up to half of the available processor capacity may be lost to the algorithmic limitations of partitioned scheduling.

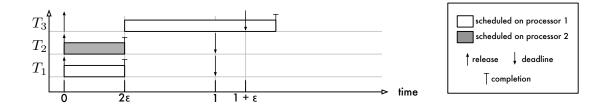

In contrast, optimal global schedulers exist. For example, consider *global EDF* (G-EDF), where the uniprocessor EDF policy is globally applied to a shared ready queue. While it has long been known that G-EDF can be subject to severe algorithmic capacity loss in an HRT context (Dhall and Liu, 1978), Devi and Anderson (2005) recently showed that G-EDF does in fact ensure bounded tardiness for any sporadic task set with utilization at most m, i.e., G-EDF is optimal in an SRT context (Devi, 2006; Devi and Anderson, 2008).

For HRT constraints, the global algorithm  $PD^2$  is optimal (Srinivasan and Anderson, 2006).  $PD^2$  is a *proportionate fair* (Baruah *et al.*, 1996), or *pfair*, scheduler, which is a class of schedulers that ensure that a task's processor allocation is always proportional to its utilization (within stringent bounds, see Chapter 2).  $PD^2$  derives its properties from dividing jobs into (many) subtasks of fixed size, each of which is assigned an individual deadline. Subtasks are scheduled on an EDF basis with additional rules to break deadline ties.<sup>3</sup> With an appropriate subtask granularity,  $PD^2$  ensures that all deadlines will be met for any task set with utilization at most m (assuming implicit deadlines).

Therefore, in theory, global scheduling is clearly preferable to partitioned scheduling.

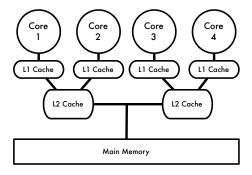

However, *in practice*, global schedulers are commonly eschewed. Many OS developers consider global scheduling to be impractical due to the associated runtime overheads and implementation complexity. For example, PD<sup>2</sup>'s subtask-based scheduling causes jobs to incur frequent preemptions and migrations. While the scheduling literature generally considers such costs to be negligible, the associated loss of cache affinity<sup>4</sup> can significantly increase a job's processor demand in practice by introducing additional cache misses. Preemptions occur less frequently under G-EDF. However, processors must still access a shared ready queue, which OS developers traditionally avoid because frequent accesses to global data structures often entail high lock contention and cache-coherency overheads. Consequently, virtually all multiprocessor-capable RTOSs employ partitioned scheduling, where most data structures and scheduling decisions are processor-local and thus cache-friendly.

<sup>&</sup>lt;sup>3</sup>The name PD<sup>2</sup> is due to its use of two tie-breaking rules and since it supersedes an earlier algorithm named PD by Baruah *et al.* (1995). Algorithm PD derives its name from the use of "pseudo-deadlines" (Baruah *et al.*, 1995).

<sup>&</sup>lt;sup>4</sup>Cache affinity and the impact of cache misses are reviewed in Section 2.1.2.

Of course, it would be unrealistic to expect global algorithms to scale to tens or hundreds of processors. However, this does not imply that the other extreme, partitioned scheduling, is the best choice. Instead, *clustered scheduling* (Calandrino *et al.*, 2007; Baker and Baruah, 2007) could be a practical, better-performing compromise. Illustrated in inset (c) of Figure 1.1, clustered scheduling is a hybrid of both global and partitioned scheduling that groups processors sharing low-level caches into disjoint *clusters*. As under partitioning, tasks are statically assigned to clusters during an offline phase. Within each cluster, jobs are then scheduled "globally" from a shared per-cluster ready queue. The intuition behind clustered scheduling is to reconcile the advantages of both partitioned and global scheduling: the impact of bin-packing issues is reduced as there are fewer and larger bins (compared to partitioned scheduling), some level of cache affinity is maintained during job migrations, and lock contention is reduced as queues are shared among fewer processors (compared to global scheduling).

Nonetheless, most multiprocessor-capable RTOSs currently rely on *partitioned fixed-priority* (P-FP) scheduling as the primary supported real-time scheduling policy. This choice reflects great conservatism: even among partitioned schedulers, P-FP is inferior to *partitioned earliest-deadline first* (P-EDF) scheduling since EDF is optimal on a uniprocessor and FP is not (Liu and Layland, 1973). Yet P-FP has remained the *traditional* RTOS scheduler due to its uniprocessor legacy and the previously mentioned POSIX-compliance reasons.

Compliance with the POSIX real-time standard (IEEE, 1993, 2003, 2008b), however, should not prevent needed innovation and adaptation. The standard is in fact silent on multiprocessor issues, and understandably so, as multiprocessor real-time systems were still an "academic curiosity" when it was first ratified. It further does not preclude RTOSs from supporting other, possibly better-performing scheduling policies in addition to the mandated FP. With the advent of the multicore age, and given that RTOSs are now being redesigned and restructured to adapt, it is presently an opportune time to revisit the choice of a "default" RTOS scheduler.

<sup>&</sup>lt;sup>5</sup>The preamble to the original POSIX real-time extension makes this explicit: "It is beyond the scope of these interfaces to support networking or multiprocessor functionality" (IEEE, 1993, p. 2). The original document has since been superseded by the "real-time and embedded application profiles" (IEEE, 2003), which define use-case-specific subsets of the (much larger) POSIX "base profile" (IEEE, 2008b). The former does mention multiprocessors, but only in the context of the absence of memory barriers and spinlocks (IEEE, 2003, p. 49). The latter does not discuss multiprocessor scheduling, but does mandate FP scheduling with at least 32 distinct priorities for OSs that support scheduling at all (IEEE, 2008b, pp. 501–505).

## 1.2.3 Real-Time Locking

Most published schedulability tests make the simplifying assumption that tasks (and hence jobs) are *independent*, that is, it is assumed that a job is never delayed by actions of other jobs. In practice, this assumption does not hold when jobs share resources that are protected by locks. For example, if a job must transmit a message, but the required network device has already been locked and is in use, then the job is *blocked*—it cannot progress until the shared resource becomes available.

Such blocking can endanger temporal correctness because it can give rise to *priority inversions*, which, intuitively, occur when a high-priority job is forced to wait for a lower-priority job. Uncontrolled priority inversions jeopardize the temporal correctness of real-time tasks because they can result in unpredictable delays. However, if the maximum delay due to resource sharing is known *a priori*, then it can be accounted for when testing whether a given task set is schedulable. An RTOS must thus incorporate a *real-time locking protocol* that allows the maximum length of priority inversion to be analytically bounded. Naturally, it is desirable to employ locking protocols that minimize the occurrence of priority inversions since frequent or long priority inversions severely limit an RTOS's suitability for ensuring stringent real-time constraints. A practical locking protocol should further be easily and efficiently implementable, just as with schedulers.

Unfortunately, few RTOSs implement any algorithm beyond basic uniprocessor priority inheritance and ceiling protocols, which are insufficient under partitioned scheduling (see Section 2.4.4.2). In effect, current RTOSs fundamentally fail to provide the means necessary to *predictably* use locks on multiprocessors (special cases aside). Given that extensions of uniprocessor protocols that are (at least theoretically) appropriate for P-FP scheduling have been available for more than 20 years (Rajkumar *et al.*, 1988; Rajkumar, 1990, 1991), this is a dire state of affairs.

Given the relative immaturity of multiprocessor real-time locking research (compared to advances in real-time scheduling), the lack of proper locking protocol support is hardly surprising. In fact, prior to the work presented herein, locking optimality questions had received little, if any, attention. As a result, goals such as "minimizing the occurrence of priority inversion" were only intuitively understood and lacked analytical precision. Instead, provably optimal multiprocessor locking protocols that are also simple and efficient to implement are needed.

# 1.3 Thesis Statement

To *fully* exploit the potential of modern multicore platforms, RTOSs will have to advance beyond the traditional, but increasingly strained uniprocessor approach of FP scheduling with priority inheritance. With regard to Question Q1, several promising multiprocessor scheduling approaches exist. With regard to Question Q2, while the multiprocessor locking protocol design space is still relatively unexplored, and questions of optimality have not received much attention in prior work, proper locking protocols for P-FP scheduling exist. Yet neither such protocols nor promising schedulers have been evaluated, much less adopted, in mainstream RTOSs to date.

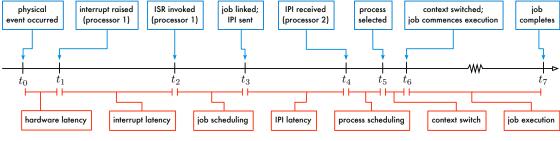

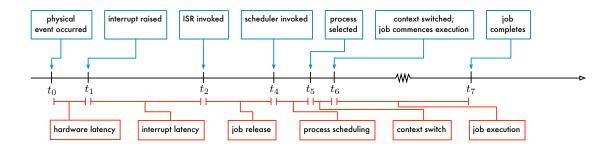

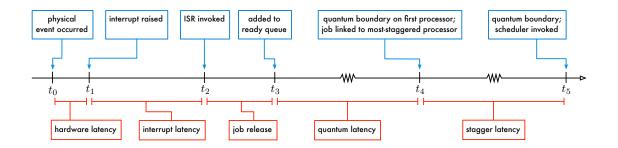

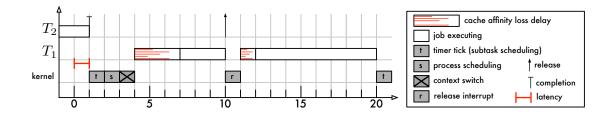

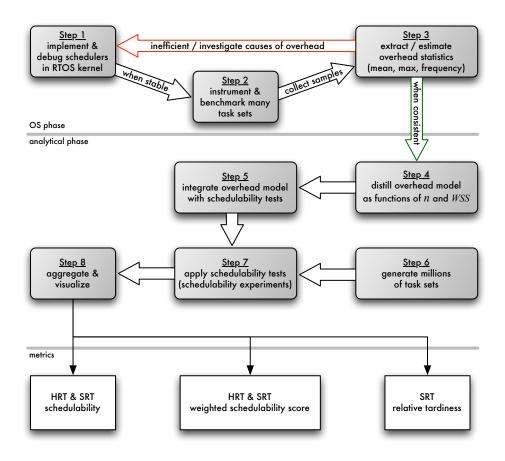

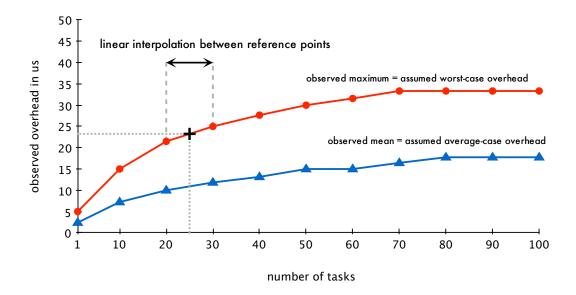

A primary cause for this growing disconnect is the open question of practicality. Runtime overheads are typically considered to be negligible in algorithm-centric research, but such overheads are rarely negligible in practice. In fact, many overhead sources can exhibit counterintuitive trends that are difficult to anticipate. As a result, there is a strong focus on overhead measurements in the RTOS community, with a particular focus on *interrupt latency*, which is a metric that reflects the RTOS's responsiveness in enacting scheduling decisions. Unfortunately, this causes a disregard for algorithmic properties, as latency by itself fails to capture schedulability analysis tradeoffs that arise when multiple tasks subject to varying timing constraints compete for processor time.

Either extreme—completely disregarding overheads or making them the sole focus—yields only incomplete and misleading answers. Are algorithmically optimal, high-overhead global schedulers still superior to non-optimal, low-overhead partitioned schedulers if overheads and algorithmic properties are both fully accounted for? If not, is clustered scheduling a viable compromise?

Motivated by these considerations, the main thesis supported by this dissertation is the following.

A "multicore-ready" RTOS should employ scheduling and synchronization algorithms that minimize the loss of processor capacity allocable to real-time tasks. When both overhead-related and algorithmic capacity loss are considered on a current multicore platform, (i) partitioned scheduling is preferable to global and clustered approaches in the HRT case, (ii) P-EDF is superior to P-FP, and (iii) clustered scheduling can be effective in reducing the impact of bin-packing limitations in the SRT case. Further, (iv) multiprocessor locking protocols exist that are both efficiently implementable and asymptotically optimal with regard to the maximum duration of priority inversion.

# 1.4 Contributions

In the following, we briefly summarize the contributions presented in the subsequent chapters.

#### **1.4.1 LITMUS**<sup>RT</sup>

Central to our work is the proposition that a meaningful comparison of multiprocessor scheduling and locking algorithms must be implementation-based. An actual RTOS is thus required. To this extent, we co-developed the Linux Testbed for Multiprocessor Scheduling in Real-Time Systems (LITMUS<sup>RT</sup>).<sup>6</sup>

As the name implies, LITMUS<sup>RT</sup> is an extension of Linux (Torvalds, 1997; Torvalds and contributors, 2010), which is a widely used open-source UNIX-like kernel. Conceptually, LITMUS<sup>RT</sup> consists of three parts: (i) it extends Linux's scheduling infrastructure with an implementation of the sporadic task model, (ii) it provides a plugin interface that allows the active scheduling policy and locking protocols to be changed at runtime, and (iii) it provides additional system calls for real-time tasks.

The Linux scheduling framework is structured as a hierarchy of *scheduling classes*. Each scheduling class encapsulates the policy used for a particular process type. For example, regular user-space processes are scheduled using CFS, a timesharing policy inspired by proportional-share fair scheduling (Tijdeman, 1980; Stoica *et al.*, 1996). Similarly, scheduling classes for low-priority background work and high-priority "real-time" processes exist. (In compliance with the POSIX standard, Linux's real-time scheduling class uses FP scheduling with support for 100 distinct priority levels.) Whenever Linux makes a scheduling decision, it polls each scheduling class in the hierarchy in top-to-bottom order until a pending task is found. LITMUS<sup>RT</sup> introduces a new scheduling class at the top of the hierarchy such that non-LITMUS<sup>RT</sup> tasks are only scheduled when no real-time workload is present.

In contrast to the regular Linux scheduling classes, the LITMUS<sup>RT</sup> scheduling class does not implement any particular policy. Instead, it defers all scheduling decisions to the active real-time

<sup>&</sup>lt;sup>6</sup>LITMUS<sup>RT</sup> is a group effort. However, the author is the principal designer and developer of the core LITMUS<sup>RT</sup> distribution and has contributed most of its significant features in the process of preparing this dissertation. Various extensions of the LITMUS<sup>RT</sup> core have been developed and described by others (Block, 2008; Calandrino, 2009; Leontyev, 2010; Bastoni, 2011); these are not the subject of this dissertation.

scheduler plugin. This simplifies experimental scheduler development and maintenance: instead of interfacing with the full Linux kernel (and its considerable complexities that tend to change from version to version), LITMUS<sup>RT</sup> plugins interface only with the LITMUS<sup>RT</sup> scheduling class via the plugin interface, which remains (mostly) stable between releases. Notably, LITMUS<sup>RT</sup> supports global scheduling policies, which are not well supported by standard Linux.

LITMUS<sup>RT</sup> further augments the Linux system call interface with additional real-time-specific system calls. In particular, LITMUS<sup>RT</sup> adds calls for real-time task and job control (*e.g.*, to configure task parameters, to wait for the next job release, to obtain the job sequence number, *etc.*) and for invoking real-time locking protocols (*e.g.*, to acquire resource handles, to lock resources, *etc.*).

An early prototype of LITMUS<sup>RT</sup> existed prior to the commencement of the work described in this dissertation (Calandrino *et al.*, 2006); however, this early version lacked several critical features. In particular, it did not allow processes to suspend for any reason (such as loading shared libraries, acquiring a semaphore, or using any kind of I/O device), to the effect that the system failed with a "kernel panic" if a real-time task attempted to suspend. Consequently, only artificial, completely processor-bound workloads could be supported. In the current version of LITMUS<sup>RT</sup> (which this dissertation is based on), these limitations have been removed and virtually no code from the beginnings of LITMUS<sup>RT</sup> remains. The design and implementation of LITMUS<sup>RT</sup> is discussed in detail in Chapter 3.

# 1.4.2 Comprehensive Overhead Accounting

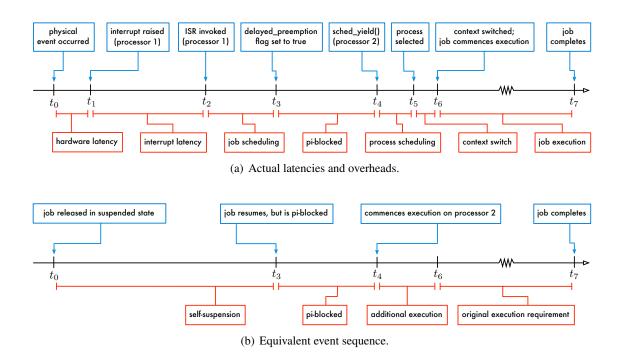

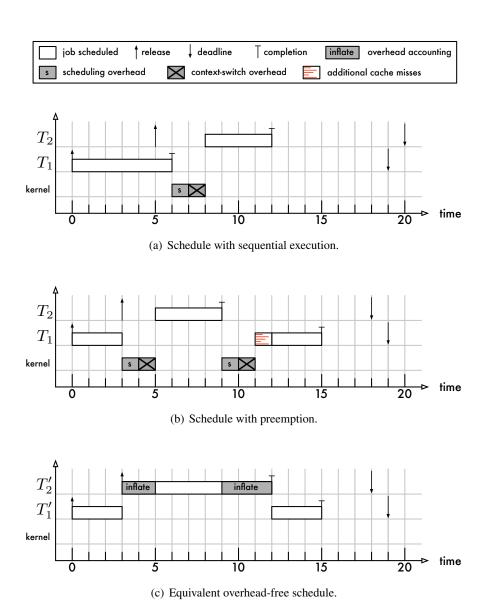

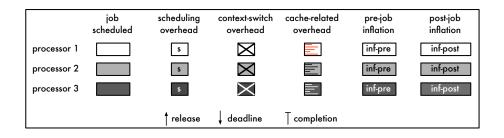

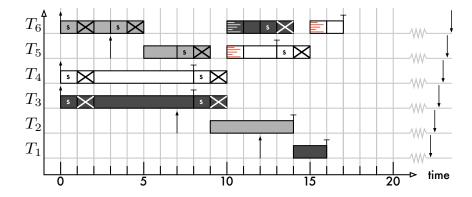

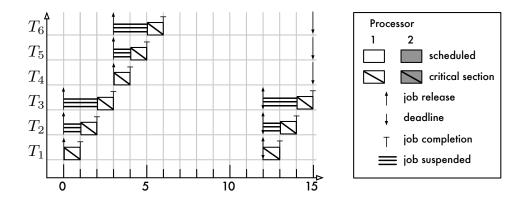

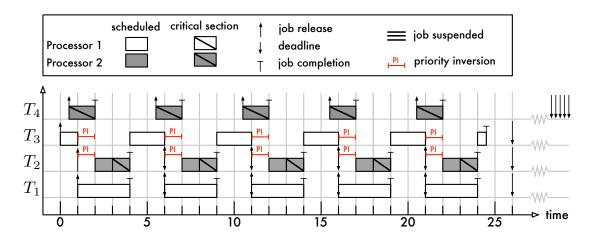

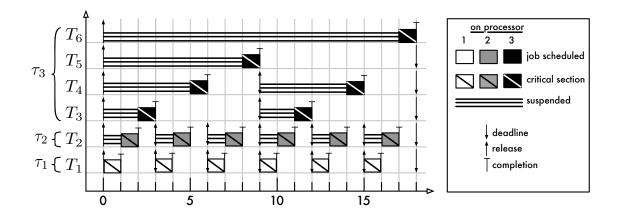

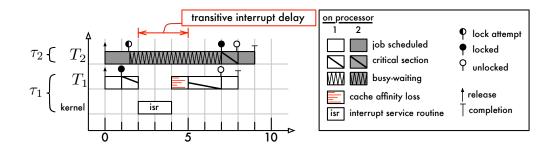

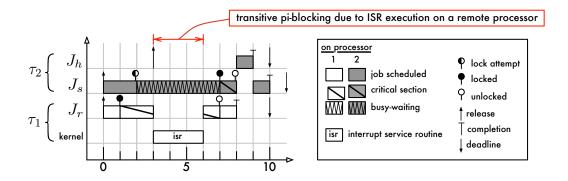

As argued above, it is critical to account for runtime overheads when establishing whether a task set is schedulable. This requires procedures for incorporating delays due to overheads into published schedulability tests that assume ideal, overhead-free execution. In particular, such procedures must be *safe*, *i.e.*, they may not underestimate delays due to overheads at runtime.