# **CPS: Medium: GOALI: Enabling Scalable Real-Time Certification for AI-Oriented Safety-Critical Systems**

**Principal Investigator** James H. Anderson,\* Kenan Distinguished Professor

### **Co-Principal Investigators**

Frank D. Smith,\* Research Professor Ron Alterovitz,\* Professor Prakash Sarathy,<sup>†</sup> Chief Engineer/Senior Program Manager

\*Department of Computer Science The University of North Carolina at Chapel Hill Chapel Hill, North Carolina 27599-3175 Phone: (919) 590-{6057, 6184, 6068} E-mail: {anderson, smithfd, ron}@cs.unc.edu

<sup>+</sup>Mission Management Control Systems Northrop Grumman Aerospace Systems Redondo Beach California 90278 Phone: 310-812-6914 Email: sriprakash.sarathy@ngc.com

June 2020

# **Project Summary**

#### **Overview**.

CPS: Medium: GOALI: Enabling Scalable Real-Time Certification for AI-Oriented Safety-Critical Systems,

James H. Anderson, PI, The University of North Carolina at Chapel Hill

In avionics, an evolution is underway to endow aircraft with "thinking" capabilities through the use of artificial-intelligence (AI) techniques. This evolution is being fueled by the availability of high-performance embedded hardware platforms, typically in the form of multicore machines augmented with accelerators. Unfortunately, avionics software certification processes, which are rooted in the twin concepts of *time and space partitioning*, have not kept pace with this evolution. On a uniprocessor, these concepts can be simply applied to decompose a system into smaller components that can be specified, implemented, and understood separately. On a multicore+accelerator platform, however, component isolation is much more difficult to achieve efficiently. This fact points to a looming dilemma: unless reasonable notions of component isolation can be provided in this context, *certifying AI-based avionics systems will likely be impractical*.

This project will address this dilemma through multi-faceted research in the CPS Core Research Areas of Real-Time Systems, Safety, Autonomy, and CPS System Architecture. It will contribute to Real-Time Systems and Safety by producing new infrastructure and analysis tools for component-based avionics applications that must pass real-time certification. It will contribute to Safety and Autonomy by targeting the design of autonomous aircraft that must exhibit certifiably safe and dependable behavior. It will contribute to CPS System Architecture by designing new methods for decomposing complex AI-oriented avionics workloads into components that are isolated in space and time.

**Intellectual merit.** This project will produce a framework for supporting components on multicore+accelerator platforms in AI-based avionics use cases. This framework will balance the need to isolate components in time and space with the need for efficient execution. Component provisioning hinges on execution time bounds for individual programs. New timing-analysis methods will be produced for obtaining these bounds at different safety levels. Research will also be conducted on performance/timeliness/accuracy tradeoffs that arise when refactoring *time-limited* AI computations for perception, planning, and control into components. Experimental evaluations of the proposed framework will be conducted using an autonomous aircraft simulator, commercial drones, and facilities at Northrop Grumman Corp.

**Broader impacts.** There has been a continuous push over the past 40 years toward more semi-autonomous and autonomous functions in avionics. This push began with auto-pilot functions and is increasingly being fueled by advances in AI software. Avionics certification procedures have not kept pace with these advances. This project will focus on a key aspect of certification: validating real-time correctness. The results that are produced will be made available to the world at large through open-source software. This software will include operating-system extensions for supporting components in an isolated way and mechanisms for forming components and assessing their timing correctness.

A special emphasis will be placed on outreach to girls and women. Such outreach will include: events involving the Graduate Women in CS (GWiCS) group at UNC, which hosts an annual research symposium targeted toward undergraduate women and other under-represented minorities; Tar Heel Hack, a hackathon for local middle and high school girls; UNC CS's Girls Who Code Club, which provides local girls in grades 6-12 with a community for learning about CS; and UNC CS's annual Open House and Science Expo. These events will include hackathon projects as well as interactive demos of autonomous systems.

Keywords: Real-Time Systems; Safety; Autonomy; CPS System Architecture

# **Project Description**

## 1 Introduction

The use of artificial-intelligence (AI) techniques to endow embedded systems with "thinking" capabilities is transforming the role these systems are playing in our everyday lives. A decade ago, the notion of producing aircraft and automobiles at mass scales that can autonomously "think" may have seemed far fetched, yet we are closer than ever to this reality today. The evolution towards this new reality of highly intelligent systems may, in fact, be the most profound development in embedded computing to date.

Unfortunately, as this evolution moves forward, a fundamental stumbling block is looming: among the use cases that utilize the AI techniques fueling this evolution, some of the most compelling ones—such as autonomous aircraft and automobiles—fall within *safety-critical* domains for which *certification* is essential. The challenge such use cases present is that, in comparison to "traditonal" embedded systems, the AI-oriented workloads that must be supported are much more complex, and the hardware needed to support them—typically multicore machines augmented with accelerators—is much more complex as well. *How should certification processes in safety-critical domains evolve to address these complexities? Can these processes be made to scale to large systems that may be subject to partial redesigns during their lifetime?*

**Focus of this project.** This project is directed at partially tackling these questions in the context of *avionics systems*. A complete certification solution would involve addressing a myriad of difficult verification-related issues, the full range of which is well beyond the scope of any single project. The specific focus of this project will be *scalable real-time certification*. Specifically, we seek to devise techniques that enable a complex AI-oriented workload to be decomposed into manageable components that are isolated from one another, so that intra-component timing constraints can be verified independently. While our primary focus in this work will be on verifying timing constraints, we note that the ability to isolate components can aid in verifying logical correctness as well. It is our hope that the body of work produced in this project can be informative to the evolution of existing certification standards for avionics.

Avionics certification. While AI computations in automotive and avionics systems may share much in common, the latter have always been subject to much stricter certification. Fundamentally, existing avionics software certification processes are rooted in the ideas of time and space partitioning. These concepts allow a system to be decomposed into components that can be specified, implemented, and understood separately. Broadly speaking, *time partitioning* means that the real-time constraints of each system component can be certified independently, and *space partitioning* means that memory accesses by one component cannot adversely affect other components. On a conventional uniprocessor flight computer, these principles can be applied to fully isolate system components from one another, enabling a separation of concerns that is crucial for providing certification authorities with high confidence in a system's correctness.

Moving forward to AI-oriented avionics workloads and the hardware platforms they require, the situation becomes much murkier. For example, time partitioning now involves not only CPUs but accelerators as well. Also, for good performance, some degree of hardware sharing is inevitable, but any sharing breaks the illusion of isolation. Despite such complexities, *avionics certification processes <u>must</u> evolve so that reasonable notions of isolation can be afforded to system components in these new use cases*.

**Overview of proposed research.** In this project, we seek to answer a single overarching question:

Can a time and space partitioning solution be found for AI-oriented avionics workloads hosted on multicore+accelerator hardware that enables the real-time correctness of an overall system to be certified with high confidence while making efficient usage of hardware resources?

We will address this question by pursuing five research goals.

• Goal 1: Produce criticality-aware timing-analysis methods for multicore+accelerator platforms. In order to support components, we need to know how long their constituent tasks take to execute, and these tasks may be of differing *criticalities*, with higher-criticality tasks requiring more stringent analysis. We will extend prior work on *measurement-based probabilistic timing analysis* (*MBPTA*) [16,21] to provide execution-time safety assurances based on criticalities in a multicore+accelerator setting.

- Goal 2: Enable cross-component temporal and spatial isolation. We will devise basic time- and space-partitioning mechanisms for multicore+acclerator platforms that approximate the uniprocessor ideal of giving components the illusion of executing on dedicated hardware. In producing such mechanisms, we will extend prior work on mitigating multicore interference (due to cache or memory contention, I/O, *etc.*) to apply in a component hierarchy where criticality-related nuances exist.

- Goal 3: Create methods for validating component timing constraints. Using the mechanisms developed under Goal 2, we will develop automatic methods for forming components and assigning hardware resources to them, and for validating intra-component timing constraints. AI computations are typically formulated as processing graphs, and the timing constraints of interest are graph response-time bounds. These graphs have complexities not considered in prior work.

- **Goal 4: Create methods for component-wise AI.** There has been a trend recently in research on AI for autonomy to aggregate functionality. Such aggregation can be harmful from a certification point of view (*and AI researchers need to be aware of this*). We will investigate different methods for decomposing avionics AI functions (*e.g.*, grouping by time horizon vs. by functionality) and assess the tradeoffs involved. We will also initiate work on *time-limited AI*.

- Goal 5: Evaluate our isolation methods in supporting "real" AI-oriented avionics workloads. We will conduct evaluations through experiments conducted at UNC using both Microsoft AirSim [82] and sub-scale drones. Additional evaluations will be conducted by our students using design and testing facilities for autonomous aircraft at Northrop Grumman as part of summer internships.

**Qualifications.** PI Anderson has published extensively on the topic of multicore real-time systems and has taken a leading role internationally in work in this area. He is an ACM Fellow and an IEEE Fellow, and his fellow citations reference this research track record. Co-PI Smith has several decades' worth of software-development experience (both at IBM and at UNC) in the areas of operating systems (OSs), compilers, networking, and file systems (*e.g.*, as a principal in the Andrew Project). Co-PI Alterovitz brings expertise on AI and robotics to the project. In 2019, he received the Presidential Early Career Award for Scientists and Engineers (PECASE). This is the highest honor bestowed by the US government to early-career scientists and engineers. Co-PI Sarathy is the mission-management technical lead at Northrop Grumman Corp. for several DoD projects directed at advanced avionics for unmanned systems. His areas of technical expertise include avionics applications of neural networks in decision-making paradigms.

**Organization.** In the rest of this proposal, we provide needed background (Sec. 2), describe the research we propose to undertake and our experimental and collaboration plans (Secs. 3-5), discuss broader impacts (Sec. 6), and discuss results by the investigators from prior NSF support (Sec. 7).

# 2 Key Concepts and Related Work

In this section, we present needed background on trends in avionics, the use of AI techniques in realizing autonomous functionality, avionics certification, and real-time systems. Due to space constraints, *our overview of prior work focuses on research of direct relevance to our research agenda*.

### 2.1 Emerging Trends in Avionics

Smallish drones (which usually do not require certification) have seen greater innovation in AI-based autonomy than larger aircraft (which do), yet autonomy in the latter has been increasing for 40 years.

**Evolution of autonomy in avionics.** The most successful instance of autonomy has been the *autopilot* function installed in piloted fly-by-wire aircraft in the mid-1980s by Boeing and Airbus [91]. Autopilot initially provided flight control for cruising, but more advanced functions are now integrated into a full *flight-management system (FMS)* that enables autonomous control from just after take-off to landing [83]. Conventional FMSs are firmly rooted in control theory, with control laws implemented as ordinary sequential programs without the learning or adaptation capabilities inherent in AI-based applications.

Autonomy for unmanned aerial vehicles (UAVs). A UAV is essentially a "remotely piloted aircraft." Notable (large) military UAVs include the MQ-9 Reaper (offensive strikes), the RQ-4 Global Hawk (surveillance and reconnaissance), and the MQ-1B Predator (multi-mission). In these systems, the ground-based crew is responsible for mission control and strikes, but flight operation is mostly autonomous, using control laws similar to those in conventional FMSs. More recently, UAVs providing even greater autonomy have been demonstrated, such as the Navy's MQ-25, an unmanned aerial refueling tanker.

In the private sector, smallish UAVs—referred to as *drones* in this document—weighing up to 55 pounds and costing \$1,000–\$10,000, have been licensed for operation by the US Federal Aviation Administration (FAA). As of March 2020, over 440,000 commercial drones had been registered with the FAA [25]. Camera-equipped drones are used in applications in fields as varied as agriculture, construction, real estate, and law enforcement, to name a few.

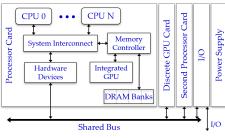

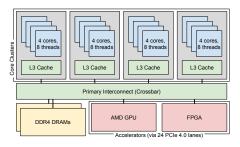

**Hardware trends.** In large aircraft, the dominant hardware infrastructure is based on the concept of *integrated modular avionics* (*IMA*), which is defined in several ARINC (Aeronautical Radio, Inc.) reports (the core ones being 629, 651, and 659) [74]. The goal of IMA is to integrate all major aircraft systems (*e.g.*, flight management) onto a few (ideally one) hardware modules. The canonical module is a cabinet with a power supply, a bus, and plug-in slots for processors, memory, sensors, and I/O, as shown in Fig. 1. In contemporary IMA systems, a slot may hold a plug-

in board containing a system-on-chip (SoC) with a multicore processor and integrated GPU along with on-board memory. Configurations with separate slots for a multicore processor, a discrete GPU or other accelarator, and shared DRAM are also possible if applicable ARINC specifications are met. More recently, embedded systems meeting *size*, *weight*, *power*, *and cost* (*SWaP-C*) requirements are providing much greater computing power with SoC platforms that include accelerators.

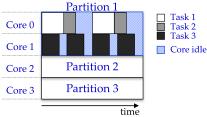

**Software trends.** The IMA concept is rooted in the sharing of hardware among software components, which can create non-deterministic effects due to interference. The IMA design recognizes this issue and includes a real-time OS (RTOS) design specification in ARINC report 653 [75]. The fundamental OS concept in ARINC 653 is a *partition*. A partition encapsulates a set of related software components and affords them isolation in *time* (execution) and *space* (memory). Space isolation is provided via functions for memory protection. Time isolation is achieved with a two-level scheduling mechanism. Time slices are first allocated to partitions, and, within each partition, an in-partition scheduler allocates time to its contained tasks. On multicore platforms, the current specification allows only

tasks. On multicore platforms, the current specification allows only one partition per core<sup>1</sup> (effectively obviating partition time slicing) but a single partition can execute on multiple cores, as shown in Fig. 2.

Due to the extreme limitations on SWaP-C, avionics software for autonomous functions in drones has been mostly limited to basic flight controls and GPS navigation. As a result of the increasing computational capability of embedded hardware platforms, however, computationally demanding AI functions are being used on several commercial and small military drones, such as the RQ-11 Raven and Desert Hawk III.

### 2.2 AI Applications and Workloads for Autonomy

In this section, we review two highly promising uses of AI in avionics for autonomous operation.

**Computer vision (CV).** One of the most fundamental capabilities an autonomous aircraft must have is *perception, i.e.,* the ability to sense and understand its environment. Cameras arguably provide the richest and most cost-effective sensing capabilities. With one or more cameras operating at rates fast enough to convey motion information, CV algorithms can effectively provide the required perception capabilities.

Figure 1: A sample hardware platform.

Figure 2: Three partitions on four cores. Partitions 2 and 3 each execute on one core, while Partition 1 executes on two cores. In-partition scheduling is shown for Partition 1.

<sup>&</sup>lt;sup>1</sup>This restriction is under study for change. The results of this project would be highly informative in making this change.

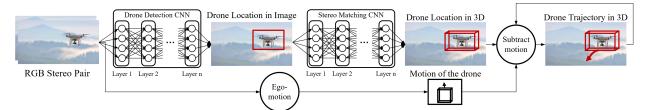

Figure 3: Example drone detection/tracking graph, comprised of two deep neural networks and additional nodes.

**Example.** Fig. 3 illustrates how CV algorithms might be used to detect and track other drones that may cross a given drone's flight path. First, the drone performs *object detection* to identify any other drones. This is done using a *convolutional neural network* (*CNN*) to quickly obtain a *bounding box* for any drone. Second, the drone must determine whether another drone is a collision threat. This is done by analyzing the other drone's relative position in 3D via another CNN performing *stereo matching* [50], and then estimating the other drone's motion relative to *ego-motion* (*i.e.*, self-motion). Next, *object tracking* is performed by remembering and tracking any detected drone's position over time. CV methods can then build a *3D geometry map* of the environment indicating the location and motion of obstacles, such as other drones.

**Planning and control.** Another important capability of an autonomous aircraft is for it to automatically decide where to move, including both short-term decisions (to react to obstacles such as other drones) and longer-term decisions to accomplish its mission. Planning algorithms typically compute waypoints for the aircraft to reach that accomplish the aircraft's task while avoiding obstacles represented in the 3D geometry map, and control algorithms enable the drone to move through the waypoints. Modern control methods for autonomous drones often use machine learning, *e.g.*, evaluating a neural network or other learned model that was pre-trained on a combination of simulation and physical drones to enable fast motion in highly dynamic settings that are challenging to model using traditional control approaches [37].

**Importance of accelerators and isolation.** The neural networks used to realize these two capabilities consist of a number of sequentially executed "layers," many of which run convolutions with matrix-matrix operations [50]. Convolutions are computationally expensive when implemented by a single CPU thread, but can be structured to run on hundreds of parallel threads/cores on a GPU or some other accelerator.

Advances in multicore+GPU embedded platforms are already enabling AI capabilities in commercial drones. For example, Skydio 2 can autonomously avoid collisions while following a tracked object by using an NVIDIA Jetson TX2 with six ARM cores and a 256-core GPU to process six camera feeds [84]. Enhanced autonomy will require supporting many more accelerator-using computations, which will be difficult to certify if not isolated from one another. Unfortunately, *accelerator sharing breaks isolation*.

### 2.3 Avionics Software Certification

In the US, the FAA is responsible for certifying the safety and airworthiness of commercial aircraft.<sup>2</sup> The European Union Aviation Safety Agency (EASA) performs the same function in the EU (using similar processes as the FAA). The FAA process involves a byzantine network of related (and often overlapping) documents for regulations, advisories, directives, orders, notices, *etc.*, as well as a collection of documents providing "guidelines," "considerations," and "positions," which are actually de facto standards [24].

**Software certification.** For the certification of avionics software (this project), the primary documents are ARP 4761 [86] for the *safety-assessment process*, ARP 4754 [78] for the *development process*, and DO-178C [76] for the *compliance process*. DO-178C is supplemented by documents that address specific tools and technologies recommended: DO-248 (clarifications and rationales), DO-330 (tool qualification), DO-331 (model-based development), DO-332 (object-oriented technology), and DO-333 (formal methods).

ARPs 4761 and 4754 define five *design assurance levels* (*DALs*), often called *criticality levels*, based on the severity of software-failure impacts. As shown in Table 1, DO-178C refers to the same five levels and defines verifiable per-level objectives. High-level *requirements* are defined for software components according to their designated criticality level. These requirements are then refined into detailed requirements for the processes, modules, function calls, and program statements in the component.

<sup>&</sup>lt;sup>2</sup>The US military has its own airworthiness certification agencies but has the option of FAA certification.

| Level | Failure Condition | Interpretation                                                          |  |  |  |

|-------|-------------------|-------------------------------------------------------------------------|--|--|--|

| A     | Catastrophic      | Failure may cause a crash.                                              |  |  |  |

| B     | Hazardous         | Failure has a large negative impact on safety or performance            |  |  |  |

| C     | Major             | ailure is significant, but has a lesser impact than a Hazardous failure |  |  |  |

| D     | Minor             | Failure is noticeable, but has a lesser impact than a Major failure     |  |  |  |

| E     | No Effect         | Failure has no impact on safety, aircraft operation, or crew workload.  |  |  |  |

| Hazardous | Failure has a large negative impact on safety or performance             |

|-----------|--------------------------------------------------------------------------|

| Major     | Failure is significant, but has a lesser impact than a Hazardous failure |

| Minor     | Failure is noticeable, but has a lesser impact than a Major failure      |

| No Effect | Failure has no impact on safety, aircraft operation, or crew workload.   |

|           | Table 1. DO 170C with a liter levels                                     |

| Table | 1: | DO-178C | critical | lity | levels. |

|-------|----|---------|----------|------|---------|

|       |    |         |          |      |         |

We are mainly interested in *real-time requirements* like "task  $\tau_i$  must issue a cockpit warning within 100ms of stall detection." Ensuring such requirements requires knowing task worst-case execution times (WCETs). FAA document CAST-32A [23] gives guidance for determining WCETs on multicore platforms.

Regarding accelerators, the FAA has approved the use of GPUs to realize display functions. However, in this project, we are interested in using accelerators to speed critical planning and control steps.

### 2.4 Real-Time Systems

This project is aimed at avionics systems comprised of *components*, some providing AI functions, that must be isolated from one another. In reality, such a system would likely transition among different functional *modes* in response to external events, with only certain components (or portions thereof) being active in a given mode. For conciseness, we only consider the problem of ensuring isolation in a single mode herein, though all of the work we discuss can be generalized to multi-mode systems.

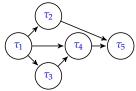

As we have seen, AI computations tend to be expressed as processing graphs. While AI graphs often have cycles, the most widely studied notion of a real-time processing graph is that given by the sporadic DAG (directed acyclic graph) model [13]. Under this model, graph nodes represent tasks (programs), and edges denote precedence constraints. For example, in Fig. 4, the ith invocation, or *job*, of task  $\tau_2$  cannot start execution until the *i*<sup>th</sup> job of task  $\tau_1$

Figure 4: A DAG example.

completes. A sporadic DAG G has a designated source node with no incoming edges. The entire graph G is implicitly executed cyclically, with successive invocations of its source being at least  $T_G$  time units apart, where  $T_G$  is G's period. The main timing constraint of interest is an end-to-end response-time bound, which indicates the maximum allowed time for a given graph invocation to complete.

We hereafter assume that each component of interest is comprised of a set of processing graphs, but the graphs we consider generalize sporadic DAGs in several ways. First, a graph may have multiple sources (e.g., to support graphs that fuse data from different sources that execute at different rates). Second, each graph node is assigned a criticality level (as in DO-178C). Third, graphs may have cycles (e.g., to enable processing historical data, as in Fig. 3).<sup>3</sup> Fourth, graph nodes may access accelerators. Fifth, certain graph nodes may be allowed to execute in parallel to lower response times. Note that the computational model assumed here is quite general—even an ordinary task can be viewed as a (single-node) graph.

Timing analysis vs. schedulability analysis. The goal of *timing analysis* is to produce an execution time bound  $C_i$  for each task  $\tau_i$ . Usually, a single WCET is required, though our mixed-criticality context is more nuanced (see below). The goal of schedulability analysis is to verify that timing constraints are met (in our case, that end-to-end response-time bounds are acceptable). Of relevance to schedulability is the processor share required by each task  $\tau_i$ , as given by its *utilization*  $U_i = C_i/T_G$ . When assessing schedulability on a multiprocessor, it is often necessary to restrict utilizations in some way. This results in *capacity loss*, *i.e.*, unavailable processing capacity. In addition to such schedulability-induced capacity loss, overhead-related loss can occur due to OS activities, task migration costs, etc. Interference across cores on a multicore platform can also cause capacity loss. The rigid ARINC 653 scheduling strategy for partitions is subject to severe *capacity loss*, mainly because it allocates cores at the granularity of whole partitions.

Mixed-criticality analysis. Pessimistic WCETs can induce significant capacity loss. A technique for mitigating this loss was proposed by Vestal, who (while working in the avionics industry) proposed dealing

<sup>&</sup>lt;sup>3</sup>If tasks are sequential, then each node implicitly has a self-loop. Here we are referring to more complicated cycles.

|         |                                                                                       |      |      | 2021   |       |       |       | 2022  |      |               |        | 2023  |    |  |  |

|---------|---------------------------------------------------------------------------------------|------|------|--------|-------|-------|-------|-------|------|---------------|--------|-------|----|--|--|

|         |                                                                                       | Q1   | Q2   | Q3     | Q4    | Q1    | Q2    | Q3    | Q4   | Q1            | Q2     | Q3    | Q4 |  |  |

|         | Task 1: Develop new MBPTA method for criticality-aware multicore+accelerator analysis |      |      |        |       |       |       |       |      |               |        |       |    |  |  |

| Goal #1 |                                                                                       |      |      | +      |       |       | •     | ¥     |      |               |        |       |    |  |  |

|         | Task 3: Evaluate new MBPTA method enemy tasks for interference measurements           |      |      |        |       | Info  | ormed | l by  | Tas  | <b>6</b>      |        |       |    |  |  |

|         | Task 4: Evaluate trade-offs in forbidden zone policies                                |      |      |        |       | 5     |       |       |      |               |        |       | _  |  |  |

| Goal #2 | Task 5: Explore additional time partitioning approaches for accelerators              |      |      |        |       | 4     |       |       |      |               |        |       |    |  |  |

|         | Task 6: Implement cache partitioning with hardware multithreading                     |      |      |        |       | •     |       |       |      |               |        |       |    |  |  |

|         | Task 7: Explore criticality-aware spatial isolation guarantees                        |      |      |        |       | 4     |       |       |      |               |        |       |    |  |  |

|         | Task 8: Evaluate component composition impact on acceptability graphs                 |      |      | In     | form  | ed b  | y Tas | ks 1  | -7   |               |        |       |    |  |  |

|         | Task 9: Develop heuristic and approximation approaches to component composition       |      |      |        |       | 4     | Infor | med   | by i | <b>Fask</b> s | s 1-7  |       |    |  |  |

|         | Task 10: Develop response-time analysis for intra-component scheduling                |      |      |        |       |       |       | nfor  | mec  | by T          | asks   | 48    | 5  |  |  |

| Goal #4 | Task 11: Develop techniques to subdivide planning tasks into horizon-based components | Info | rmed | d by ˈ | Task  | s 1-1 | 0     |       |      |               |        |       |    |  |  |

| Goal #4 | Task 12: Explore performance trade-offs for perception and control                    |      |      |        | L     | 1     | Infor | med   | by   | <b>Fask</b> s | s 1-1( | D     |    |  |  |

| Goal #5 | Task 13: Conduct experiments at Northrup Grumman                                      |      | an   | d inte | ermit | tentl | y dur | ing t | he a | cade          | emic y | year  |    |  |  |

|         | Task 14: Perform experiments using AirSim simulator                                   |      |      | ╞      |       | -     | nforn | ned k | у Т  | asks          | 1-12   |       |    |  |  |

|         | Task 15: Perform evaluation with sub-scale drone                                      |      |      |        |       |       | -     | Info  | orme | d by          | Task   | (s 1- | 12 |  |  |

|         | Task 16: Broader impacts activities                                                   |      |      |        | Inf   | orme  | d by  | Tas   | (s 1 | 15            |        |       |    |  |  |

Figure 5: Gantt chart of the project timeline. Intra-goal task dependencies are shown with arrows, and inter-goal dependencies are labeled with text.

with less-critical tasks less pessimistically [94]. Under his proposal, each task in a system with *L* criticality levels has a *provisioned execution time (PET)* specified at every level, and *L* system variants are analyzed: in the Level- $\ell$  variant, the schedulability of all Level- $\ell$  tasks is verified with Level- $\ell$  PETs assumed for all tasks (at any level). The degree of pessimism in determining PETs is level-dependent, with more conservatism applied to higher levels. We intend to apply similar ideas in the context of processing graphs.

### 2.5 The Looming Certification Dilemma

After many years of trying, industry and the FAA/EASA seem to be finally converging on a basic approach to safety certification for avionics software on multicore platforms. However, this basic approach, while rooted in time and space partitioning, may result in significant capacity loss by overly restricting the allocation of cores to partitions. *Such loss will limit the range of future applications that can be supported*.

Perhaps of even greater concern is a looming set of issues beyond multicore. New hardware in the form of *accelerators (especially GPUs)* will soon be required for emerging AI-oriented avionics. Current certification methods and tools cannot deal with accelerators. Consider that a CV application written as a sequential program actually executes partially on a CPU core and partially on a GPU, and these executions may overlap in time. The GPU execution is usually not preemptable while the CPU is. Further, efficient use of a GPU may require sharing it among different components. These factors greatly complicate all aspects of certification. *Multicore CPUs and accelarators must be treated holistically for certification*.

### **3** Research Description

In this project, we will resolve the avionics certification dilemma described above by pursuing a research agenda that focuses on five goals. First, we will strengthen the certification process by producing criticality-driven timing analysis that targets multicore+accelerator platforms. Second, we will produce methods for isolating different system components in space and time on such platforms while allowing some degree of hardware sharing. Third, based on these methods, we will devise techniques for creating components and validating their timing constraints. Fourth, we will elevate research on AI for autonomy by making time and component-wise certification first-class concepts. Fifth, we will experimentally assess the efficacy of the methods we produce using an advanced avionics simulator, sub-scale drones, and facilities at Northrop Grumman. We elaborate on the first four of these goals below and consider the fifth in Sec. 4. Our research agenda maps to a three-year research plan, which is depicted in Fig. 5.

**Hardware platform.** To facilitate discussing our research goals, we first describe our intended hardware platform, the AMD Ryzen 9 3950X, which is illustrated in Fig. 6. This platform has 16 physical cores (shown in blue), each supporting two simultaneous hardware threads, subdivided among four clusters (shown in grey) with a shared L3 cache each—a design intentionally similar to ARM's next-generation embedded CPU [92]. The 3950X supports AMD's Quality of Service extensions [6], which include hardware support for partitioning L3 caches and memory buses (shown in green). The 950X contains 24 PCIe

4.0 lanes, providing 48 GB/s of bandwidth for accelerators. With this high bandwidth, up to 12 GPUs could be connected.

In our initial work on hardware accelerators, we intend to use AMD Radeon VII GPUs (shown in red). The Radeon VII is one of AMD's most powerful GPUs. Our choice of AMD over the market leader NVIDIA is due to the fact that AMD GPUs offer *an open-source software stack* (unlike NVIDIA) and *hardware partitioning support* [70]. *Openness is essential from a safety point of view.*<sup>4</sup> As the project advances, we will likely consider other accelerators (both GPUs and FPGAs), and more of them.

Figure 6: AMD Ryzen 9 3950X.

**Software platform.** We will implement the isolation mechanisms developed in this project in LITMUS<sup>RT</sup> [1], a real-time variant of Linux developed by our group. Our choice of LITMUS<sup>RT</sup> over a commercial RTOS is largely due to its open-source nature and our familiarity with it. Also, the point of this project is to demonstrate the efficacy of resource-allocation *principles* that can be applied in a variety of RTOSs.

#### 3.1 Goal 1: Produce Criticality-Aware Multicore+Accelerator Timing Analysis

Supporting isolated components on a multicore+accelerator platform entails adequately provisioning hardware resources for components, but to do so, we need valid task execution costs. This observation gives rise to our first research challenge: *Given a task with a specified criticality level and a (possibly empty) set of dedicated hardware resources, how can we determine execution costs that account for contention on non-specified hardware resources for all relevant criticality levels?* Such a task may execute on a CPU and/or accelerator.

**Problems with existing timing analysis.** Existing timing-analysis methods fall short in this setting. The classical approach is *static timing analysis*, which relies on detailed knowledge of the task being executed and the platform executing it. When multiple tasks/components can interfere with one another, knowing the exact state of the platform becomes essentially impossible, preventing static analysis. This problem is even worse when dealing with accelerators that have black-box components, such as many GPUs.

An alternative to static analysis is *measurement-based probabilistic timing analysis (MBPTA)*, which attempts to probabilistically bound task execution times by examining a relatively small sample of jobs [16,21]. The majority of recent MBPTA work has focused on a family of methods known as *extreme value theory (EVT)*. Traditionally, sound EVT analysis has required observed execution times to be identically and independently distributed (IID) [11,27,72], but such times will often have statistical dependencies. There is currently no agreement on how to work around this issue [16,21,49]. Both a review of the literature on EVT and our own preliminary experiments show it is not useful for timing analysis in a safety-critical context. But if neither static analysis nor EVT are viable options, how can we build a certifiable system?

A new MBPTA method. We propose to develop a new version of MBPTA that acknowledges that the measurements used to build any estimates are themselves a source of uncertainty and subject to random variation. In particular, we will build our schedulability analysis around *safe WCETs*, or sWCETs, where each task  $\tau_i$  has an sWCET  $S_i^q$ , determined as a function of a sample of execution times, such that when  $E_i$  is a random variable corresponding to the execution time of a randomly selected job of  $\tau_i$ ,  $\Pr(E_i \leq S_i^q) = q$  holds; the ideal situation is to have q approach one. In this definition, *both*  $E_i$  and  $S_i^q$  are random variables; consequently, the value of q accounts for not only variations in  $E_i$ , but also the possibility that the execution time samples used to determine  $S_i^q$  does not give a good idea of the true distribution of  $\tau_i$ 's possible execution times. Existing MBPTA methods do not generally account for the latter factor. When a single task needs costs at multiple criticality levels, higher q values will correspond to higher criticality levels.

In recent work [68], we provided one possible method for determining  $S_i^q$  for a given value of q, or, alternatively, the appropriate value of q for a given  $S_i^q$  value. This method relies on the assumption that our observed execution-time samples constitute IID samples from  $\tau_i$ 's true execution-time profile, but we found empirically that our method produces accurate results even when samples are not IID.

<sup>&</sup>lt;sup>4</sup>Clearly, safety-critical designs will exist with proprietary details, but such a design cannot be truly safe if it is based on an underlying substrate with unknowable behaviors. Royalty-free, open APIs are actually key to industry adoption.

In this project, we plan to expand on this work by improving scalability—in our current method, *q* increases slowly with respect to the number of samples used—and reducing reliance on the assumption that samples are IID. One promising way forward may be using the Saw variant of Chebyshev's Inequality [80], which estimates population extremes based only on sample mean and variance and does not rely on data being IID. In addition, we will develop a method to determine *q* values that are appropriate for specific criticality levels as specified in the FAA System Safety Handbook [26]. Since we need our execution times to be valid when hardware resources are accounted for, our sample measurements need to be obtained when tasks are competing for resources against "enemy" tasks designed to create high levels of interference. We will develop enemy tasks for this purpose starting from the techniques recently described in [43]. A similar approach should work for analyzing contention on accelerators. One advantage our method will have is that, since we do not require any platform knowledge, but only observed measurements, we are well-placed to develop sound timing analysis should the need arise for some black-box accelerators.

#### 3.2 Goal 2: Enable Time and Space Partitioning on Multicore+Accelerator Platforms

Our work under Goal 2 will be directed at developing the requisite *mechanisms* that can be applied to isolate components in space and time. The *effective use* of such mechanisms is the focus of Goals 3 and 4.

We seek to allocate both processing (CPU and accelerator time) and non-processing (caches, memory, buses, *etc.*) resources required for exclusive use by a given component  $\mathcal{P}$ . We assume that  $\mathcal{P}$  consists of one or more processing graphs (see Sec. 2.4) and has a specified *reservation* indicating its needed hardware resources. Working out the exact details of an effective notion of a "reservation" will be a research issue we need to resolve. For our purposes here, it suffices to consider a notion of a reservation defined by three parameters, *C*, *T*, and *H*, indicating that  $\mathcal{P}$  is active for a duration of *C* time units during each period of *T* time units, and when active, it requires exclusive access to a set *H* of hardware resources; *H* would, for example, specify CPU and accelerator requirements as well as cache and memory partitions. All hardware resources used by  $\mathcal{P}$  that are not specified in *H* would be considered as contended by other components.

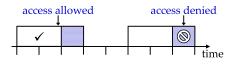

**Time partitioning.** Any time-partitioning strategy must ensure that  $\mathcal{P}$  has exclusive access to all processing resources in *H* when it is active. For the sake of concreteness, we propose one such strategy here, though others will be investigated in this project. In the specific approach here, we ensure the time partitioning of CPU resources via budgeting: during each period of time T,  $\mathcal{P}$  is allocated a *time slice* of length *C*, and during this time slice, it has exclusive access of all CPUs specified in *H*. Dealing with accelerators is a bit trickier. For them, we propose to employ the concept of a *forbidden zone* [35], as depicted in Fig. 7. To ensure that accelerator usage completes before a time-slice boundary, accesses requested too near the end of a time slice (within the forbidden zone) may be delayed until  $\mathcal{P}$ 's next time slice.

We propose two forbidden-zone variants. The first is pessimistic: all accelerator accesses within a forbidden zone are prevented. The second is more optimistic but requires the ability to preempt accelerator use: access is allowed within the forbidden zone, but execution will be aborted if the time slice ends (the access must be re-tried in the next time slice). We will explore many trade-offs here. For example, short accelerator

Figure 7: A component  $\mathcal{P}$  with C = 3 time units, T = 5 time units, and a 1-time-unit forbidden zone.

accesses may be allowed to optimistically execute, but long accesses may be prevented. Also, we will explore forbidden zones of different durations (*e.g.*, a common per-slice duration vs. durations that are per-resource or per-resource request) as well as dividing zones into optimistic and pessimistic regions.

**Space partitioning.** On a multicore+accelerator platform, space partitioning involves more than simply ensuring memory protection and policing the flow of information across components. In particular, the illusion of space partitioning can be broken on such a platform when concurrently executing components access common non-processing resources such as caches, memory, buses, *etc.* In recent years, the issue of eliminating interference with respect to such resources has been investigated extensively by the real-time systems community [3–5, 10, 18, 19, 29, 31–33, 45, 53–56, 59–61, 71, 89, 96, 97, 101, 102], including by our group [9, 17–19, 19, 56–59, 96]. However, in the context of this project, several new issues arise that need to be resolved. We mention two such issues here to provide a sense of the scope of this work.

The first issue pertains to the use of hardware multi-threading, which the FAA has flagged as being of importance to enable in avionics use cases [66]. Our 3950X hardware platform enables higher performance by providing two hardware threads per core. Unfortunately, concurrent thread execution on the same core can create unacceptably high interference for highly critical tasks. In contrast, for less-critical tasks, hardware threading may be very useful. We plan to investigate this issue, and examine the feasibility of partitioning both the L2 and L3 caches on the 3950X (through a combination of page coloring [51] and the 3950X's Quality of Service extensions) on a per-thread basis when threading is in use. Note that enabling hardware threading has implications for the timing-analysis research proposed under Goal 1.

The second issue arises due to our intent to elevate these isolation issues from the level of mere tasks to *components*. In a holistic sense, we envision the handling of non-processing resources as being *hierarchical* in our context. Across components, we seek to maintain strong isolation invariants, but within components, hardware-isolation techniques also may be of value, but in a less-strict way that hinges on criticalities. For instance, within a component, less-critical tasks may be provided with weaker isolation guarantees than highly critical tasks Also, within a component, it might be reasonable to partition a GPU into multiple *virtual GPUs* [44], but across components, we want no concurrent sharing of accelerators whatsoever.

### 3.3 Goal 3: Create Methods for Validating Component Timing Constraints

Goal 3 is directed at the problem of determining a (C, T, H) reservation for each component  $\mathcal{P}$  such that cross-component interference is minimized (using the mechanisms from Goal 2) and all timing constraints are satisfied, assuming known per-criticality-level task execution times (obtained using the methods from Goal 1), each a function of the allocated hardware resources.

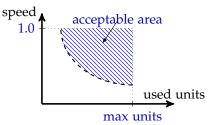

Abstracting processing resources as an exclusive virtual platform. A component  $\mathcal{P}$  with a reservation (C, T, H) has exclusive access to each processing resource (CPU or accelerator) specified in H for a fraction of time given by C/T. In describing some of the research proposed below, it is convenient to view  $\mathcal{P}$  as if it executes on a dedicated virtual platform consisting of possibly fewer CPUs and accelerators (as specified by H) than the actual platform, each executing at a slower speed, approximately C/T.

Acceptability graphs. Given this notion of a virtual platform, we can reflect the space of viable reservation choices for a given component  $\mathcal{P}$  by means of an *acceptability graph* whose axes specify the number of allocated processing resources and their speeds; a 2D version of such a graph is shown in Fig. 8. In such a graph, we define the set of all points such that the corresponding reservation is sufficient to ensure  $\mathcal{P}$ 's timing constraints as  $\mathcal{P}$ 's *acceptable area*. This area gives the reservation choices that are viable for  $\mathcal{P}$ .

**Exploring reservation options.** To understand how to best provision systems, we need to explore various issues concerning the pros and cons of different reservation choices. We mention two such issues here.

The first issue involves *component composition*. As the number of accelerators is limited, it might be necessary to combine multiple components into one, *e.g.*, it would not be reasonable to allow one component that uses all accelerators on our 3950X platform to execute alone if it requires only (say) four of the 3950X's 16 cores. To decide which components can be combined, we need to understand how the acceptability graphs for two different components  $\mathcal{P}$  and  $\mathcal{P}'$  *compose*—*i.e.*, what does the graph for  $\mathcal{P} \cup \mathcal{P}'$  look like?

The second issues involves *over-provisioning*. One way to attempt to avoid having to re-provision a system as components are modified during its service lifetime is by giving its components more hardware resources than they minimally require. This observation gives rise to several questions. What factors would favor one over-provisioning choice over another? How do we determine which hardware resources are the real "pinch points" that might require re-allocation if not over-allocated? If a component is over-allocated resources, then spare resource capacity will be available at runtime—how should it be utilized?

<sup>&</sup>lt;sup>5</sup>This notion of a virtual platform suffices to highlight some of our research ideas but over-simplifies matters. For example, due to limits on or contention for non-processing resources (*e.g.*, cache and memory space), the speed could be lower. Unfortunately, we lack sufficient space to properly delve into these and other nuances.

Allocating components. Given solutions to the problems described above, we will develop methods that determine which components need to be combined, the (C, T, H) reservation parameters for all resulting components, and a corresponding periodic timeline schedule. Our problem is related to bin-packing in that we can view cores as "bins" to be allocated but has many additional nuances. As bin-packing itself is NP-complete in the strong sense, we will likely need to resort to finding heuristics, though exact solutions might be possible that are reasonable for small problem sizes.

**Scheduling.** Given a component  $\mathcal{P}$  with reservation (*C*, *T*, *H*), we need to determine how to schedule its contained graphs and compute response-time bounds for them. While real-time graph scheduling has been studied extensively before—representative publications include [7,12,22,46–48,62,81,98,99]—several extensions to prior work will be required for our purposes. Most importantly, scheduling in our context is within a "limited processing supply" setting, where the component  $\mathcal{P}$  is active for only *C* time units out of every *T* time units. Also, the graphs that are our focus entail interacting with accelerators, can have multiple sources with different rates, and can have nodes of different criticalities. Finally, these graphs may contain cycles (as in Fig. 3), *i.e.*, they are not necessarily DAGs. While some of these issues have been considered to a limited extent before (*e.g.*, obviating multiple source rates by converting to a large single-rate DAG [28,79,88,93]), no response-time analysis exists that fully addresses them all.

### 3.4 Goal 4: Create Methods for Component-Wise AI

In Goal 4, we will refactor the AI components of an autonomous drone into components amenable to real-time certification. We will take into account that the effectiveness of a drone's AI components in real-world systems will ultimately depend on both the quality of the AI algorithms' results (*e.g.*, the accuracy of the CV algorithm or the ability of a planner to compute an obstacle-avoiding path) as well as the timing of those results, since a perfect solution computed too late may be useless.

AI software of autonomous drones. The AI software for an autonomous drone typically includes three major aspects: perception, planning, and control. *Perception* involves reading raw sensor data and translating it into a representation that is useful to planning and control. Common low-cost sensors on drones include GPS, inertial measurement unit (IMU), and cameras, and the perception component processes data from these sensors using CV methods to estimate the drone's location and to determine the presence, type, and movement of obstacles in its environment, as shown in Fig. 3. *Planning*, sometimes referred to as *navigation*, involves determining paths for the drone so it moves to accomplish an objective in a safe manner that avoids obstacles. *Control* involves computing low-level commands (*e.g.*, electric currents for each of the drone's motors) such that the drone moves along the path computed by the planner. Due to space constraints, we will focus our discussion below on planning and control. Due to the need to avoid obstacles, *planning* and control are particularly relevant for autonomous drones operating in cluttered environments, *e.g.*, indoors and in low-altitude outdoor flying in urban environments.

The need for time-limited AI. To improve the dynamic performance of autonomous vehicles, recent research approaches are increasingly integrating perception, planning, and control, often using machine learning to achieve the integration (e.g., [30,63,77,85,87]). For example, an integrated control and planning component computes both a path and an associated feedback controller for that path. This tight integration can enable a drone to avoid dynamic obstacles more effectively and at a higher speed by considering the full range of available motor torques rather than a simplified motion model when computing a path to avoid obstacles. Also, perception can be blended with both planning and control by learning mappings directly from pixels to motor torques. However, a growing danger of tightly integrating perception, planning, and control is that an autonomous drone's AI increasingly becomes one large monolithic component. A large component has the potential to increase the quality of the AI's results, but also makes it increasingly challenging to ensure that the computation completes in a short, bounded time period. We believe time limits must be considered as a fundamental constraint when designing AI software for drones. For an AI algorithm to be effective for an autonomous drone, it must (i) be of high quality, e.g., a CV algorithm accurately detects obstacles and a planner effectively avoids them, and (ii) satisfy timing constraints, e.g., it is not useful to accurately detect an obstacle only after it can no longer be avoided. Hence, the effectiveness of an AI algorithm depends on <u>both</u> the quality and the timing of the result.

Creating horizon-based certifiable components. We will investigate approaches to refactor the AI of an autonomous drone into time-limited AI components that will facilitate real-time certification. One approach we will consider is creating AI components based on time horizons, *i.e.*, the amount of time into the future that the component considers when generating its results. For example, a short-term planning and control component with a 1-sec. horizon is useful for avoiding collisions with high-speed obstacles since it allows the drone to consider nearby objects in its environment that it might encounter in the next second. A medium-term component with a horizon on the order of 10 secs. would enable efficient motion in cluttered environments where many obstacles may be present. A long-term component with a horizon of minutes or hours would enable planning for mission goals, e.g., waypoints that enable the drone to reach a far away destination or to inspect a region of interest. We will consider components for each horizon that are amenable to determination of safe WCETs and acceptable response-time bounds, which should be substantially shorter than the component's time horizon. Specifically, we will investigate components for these time horizons that blend planning and control, including model-predictive controllers, learned controllers, and search-based geometric planners [20,85,87]. To reduce duplicative computations, we will also investigate approaches to enable the planning and control components with different horizons to share some information without too adversely impacting time and space isolation guarantees.

### 3.5 CPS Research Focus

This project will break new ground on many fronts in the core CPS research areas of *real-time systems*, safety, autonomy, and CPS system architecture. Notably, it will show how to decompose complex avionics software that runs on complex hardware into manageable components that are separated in space and time, while allowing for efficient platform usage. The need to evolve avionics software systems in this way has been widely recognized in industry, but avionics companies need the help of experts on real-time resource-allocation tradeoffs such as ourselves to make this evolution happen. By thoroughly delving into these tradeoffs, this project can be a key enabler for future avionics certification procedures that can accommodate forward-looking AI-oriented features. The CPS research community can produce paper after paper about the importance of these features, but they will never become part of certified avionics systems unless these certification procedures evolve! In experimental efforts (see Sec. 4), we will explore the safe integration of the overall component-based framework arising from our work within the control harness of advanced avionics simulators, sub-scale avionics systems, and systems at Northrop Grumman. We will also provide an open-source implementation of this framework in LITMUSRT to provide a straightforward path for integration into commercial RTOSs. While the focus of this project is avionics, our results will be of use in any CPS domain of a safety-critical nature where complex software must be hosted on complex hardware, and a decomposition of a system into components would be useful for certification-notable domains of this kind include autonomous automobiles, medical robots, space vehicles, etc.

# 4 Evaluation/Experimentation Plan

This section describes our *integration* of the "cyber" results achieved by Goals 1-4 with "physical" drone hardware, and our intended evaluations.

### Goal 5: Evaluate our Methods in Supporting "Real" AI-Oriented Avionics Workloads

This proposal claims that our results will enable the development of autonomous functions for avionics where *temporal safety* is the critical requirement. Our evaluation experiments will use both simulated and physical drones to produce the types of evidence that would be needed for a certification argument that the timing requirements for safety have been met.

**Evaluation with a drone flight simulator.** There are obviously serious difficulties inherent in evaluating new avionics software by using it to fly an actual drone (injury to humans, damage to property, drone damage or loss, *etc.*). We therefore plan to first test and evaluate the software we produce with *AirSim* from Microsoft Research [82], a widely used environment simulator for AI research on autonomous vehicles. We discuss later our plans for evaluations using a physical drone.

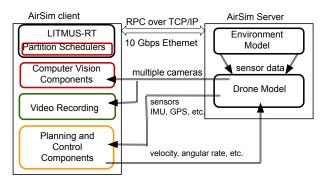

**AirSim.** AirSim uses the Unreal Engine by Epic Games to produce photo-realistic scenes along with accurate physical models of drone dynamics. As shown in Fig. 9, AirSim can be used as a remote procedure call (RPC)-based client-server system with the simulated environment and drone model(s) running on the server. The server provides to the client images of the simulated environment from multiple cameras and readings from sensors (*e.g.*, IMU, GPS). The server can also provide ground-truth data needed for evaluations, such as image depth and disparity, along with

Figure 9: Diagram of AirSim components

collision-event reports. The client can use image and sensor data to provide perception, planning, and control for flying, and send control parameters to the drone model for changing velocity, destination, *etc.*

We will configure our AirSim client as shown in Fig. 9 to use LITMUS<sup>RT</sup> (see Sec. 3) augmented with the time and space isolation features we develop. These features will enable critical components on the client (*e.g.*, object detection) to run alongside, and be isolated from, less-critical components (*e.g.*, aerial video recording), without the excessive capacity loss of current ARINC 653 methods (see Fig. 2).

**Evaluation methods.** To evaluate our time and space partitioning methods, we will instantiate a subset of AI-based avionics components consisting of (i) CV for object recognition and tracking, and (ii) planning algorithms for navigating the drone to accomplish its task while avoiding obstacles. We will also include a non-AI component (video recording) to exercise the isolation from interfering non-critical workloads. We plan to use open-source implementations of these AI components adapted to run on our client platform.

AirSim's environment model provides several built-in environments of varying complexity but also allows for the creation of custom environments. AirSim was used for a drone racing competition called *Game of Drones* at NeurIPS 2019 [64]. Competitors could participate in challenges emphasizing perception, navigation, and collision avoidance. We plan to use their open source "race track" environments as a starting point for evaluations and then craft additional scenarios of varying complexity, which will include static and dynamic obstacles that the perception and planning algorithms will need to detect and consider. Our evaluation metrics will summarize the success of the drone in navigating its environment during a set interval of time without encountering unsafe events. The AirSim server reports unsafe events such as collisions or near-misses along with navigation errors. In addition to success metrics reported by AirSim, we will also monitor metrics relevant to our research, such as graph response times, cache and memory usage, *etc.* (*Monitoring* is actually an important part of FAA-approved certification.) In addition to the metrics used in the AirSim evaluations, we will use microbenchmarks throughout the research outlined in Sec. 3, notably to assess various provisioning choices and sharing vs. isolation tradeoffs. Success here will be demonstrated by showing that a given component's temporal safety is unaffected by other co-running components, even adversarial ones that stress any non-isolated hardware resources.

**Evaluation using a sub-scale drone.** Once our implementation has been sufficiently vetted in AirSim, we will conduct further evaluations using an actual drone. AirSim provides a portable library that is API compatible with their client-server API so software verified by simulation can move to a physical drone using a compatible flight controller (*e.g.*, Pixhawk [73]). We will use a commercial drone (*e.g.*, a kit compatible with Pixhawk [36]) and outfit it with sensors, battery, and an embedded computer system. Our drone will then be capable of operating autonomously, by a remote pilot, or as a combination of both.

Experiments to evaluate the drone's performance for autonomous object detection, tracking, and collision avoidance while following pre-planned paths will be conducted outdoors. We will conduct pathnavigation trials in different lighting conditions and with a variety of obstacles. In some trials, the drone under test will share its airspace with a remote-piloted drone to test avoidance of moving objects. We will use most of the same metrics for success as in the AirSim simulations (*e.g.*, completion time and number of unsafe incidents on a given route), plus measurements such as response times. **Evaluation using Northrop Grumman facilities.** PI Anderson has been collaborating with Northrop Grumman Aerospace Sector (NGAS) over the last two decades in the area of real-time systems schedulability and temporal assurance. This ongoing collaboration provides a sound basis for our mutual collaboration on this effort. NGAS's focus on airworthiness and certification of unmanned system avionics on multicore systems aligns well with the research goals of this effort. We expect to leverage NGAS's activities and facilities to evaluate and demonstrate concepts developed herein, including detailed aircraft simulations that can be used to drive and evaluate our prototypes. This work will be mostly done by our graduate students during summer internships at NGAS. We have had many interns work at NGAS in the past and will continue this relationship under this effort. As in the past, the challenge problems from NGAS that we work on will have IP-related details sanitized so that our results can be freely published.

# 5 Project Management and Collaboration Plan

This project brings together researchers in the areas of multicore and GPU computing (Anderson and Smith), operating systems (Anderson and Smith), real-time systems (Anderson), AI and Robotics (Alterovitz), and avionics (Sarathy). This collaboration plan explains how this diverse team will interact.

**Roles.** PI Anderson (UNC) will lead the overall effort, including coordination. His work on real-time systems and GPU management is central to bringing the project together. Co-PI Sarathy (NGAS) will provide guidance and supervision of identifying and shaping avionics challenge problems and supplying representative use cases. He will serve in a technical evaluator role, leveraging his years of experience at Northrop Grumman, to properly assess the potential utility of solutions developed in this effort. He will coordinate the demonstration of these capabilities, where applicable, to relevant NGAS programs for potential insertion and transition. This uniquely close connection to industry will be enhanced by students interning at Northrop Grumman under Sarathy's supervision. Co-PI Smith (UNC) will oversee the experimental work discussed in Sec. 4. His extensive background on GPU programming and OS development makes him ideally suited to lead this work. Co-PI Alterovitz (UNC) will oversee the AI refactoring work discussed in Sec. 3.4. He will bring to the project his considerable experience developing planning and control algorithms for autonomous systems.

**Project management.** The project will commence with an in-person kick-off meeting at UNC. Thereafter, bi-weekly Zoom meetings will be held. These meetings will be attended by all investigators and supported students and any other interested parties at Northrop Grumman. These meetings will be used to discuss progress, difficulties, and future plans. Additionally, subgroups will meet weekly to coordinate research with each of the investigators individually. Additional meetings will be scheduled on an ad hoc basis to produce papers. Some in-person meetings that involve travel may occasionally be held as well.

**Internships.** It is expected that one or more of the supported students will intern at Northrop Grumman each summer or longer (where practical). These students will evaluate the software and results produced in the project using facilities at Northrop Grumman, as explained in Sec. 4. They will also participate in safety-critical software projects to gain industry certification experience. A letter of commitment from Northrop Grumman is included with this submission.

**Design repository.** UNC will create and maintain a repository as a central place for information sharing. Artifacts generated, including design documents, technical reports, publications, use cases, presentations, test data, and software, will be stored and accessible for team members.

**Dissertations and honors theses.** This project is expected to form the basis for the dissertations of at least three Ph.D. students and the honors theses for several undergraduate students. (Undergraduate students do their thesis work as part of course work rather than paid positions.) Collaborations among the students will be encouraged by requiring them to work on joint papers for conference submission.

# 6 Broader Impacts

This project will have broader impacts on many fronts: it will provide needed "cross pollination" between academia and industry by having participants from both sectors; it will benefit students by providing

fuel for several new dissertations and undergraduate honors theses, and by providing industry internship opportunities; it will benefit teachers by providing new courseware; it will benefit the research community by contributing open-source software; it will benefit underrepresented groups through outreach efforts. The investigators have a sustained track record with respect to *all* of these activities.

We lack sufficient space to discuss each of these avenues for impact in detail. We have therefore opted to focus our attention here on three particular areas of impact that are somewhat unique to our project. (Additional details are provided in the supplemental document on *Broadening Participation in Computing*.)

**Societal impact.** The results of this project will provide a sound basis for informing the evolution of avionics certification standards as they embrace AI functionality. The PI has been involved in ongoing efforts by the Army, Navy, and Air Force to create such standards in the military sector, so more immediate impact can be expected there. The proposed research will also aid in educating the current engineering workforce with respect to the design and development of future control systems using advanced embedded hardware platforms. Such education will be done through meetings, workshops, and seminars with engineers on site at NGAS and at industry-focused events such as the AIAA Aviation Forum.

**Impact within the research community and industry.** We expect that the open-source component framework we intend to implement and maintain will transform how experimental research related to real-time avionics systems is done, much the way our development of LITMUS<sup>RT</sup> transformed the way experimental work is done in the real-time systems community. We plan to host tutorial sessions to promote our open-source framework at top conferences such as the IEEE Real-Time Systems Symposium (RTSS). We also plan to host a workshop at an AI/robotics conference to discuss the importance and challenges of considering real-time constraints and certification in AI algorithms designed for autonomous drones. Additionally, Wind River is a key partner of Northrop Grumman, and this close working relationship offers an ideal avenue for exporting our research ideas, as implemented in LITMUS<sup>RT</sup>, into a commercial RTOS.

**Broadening the participation of women and girls in computing.** To say that there is a dearth of women in real-time and embedded computing would be a vast understatement. When the PI became chair of the IEEE Technical Committee on Real-Time Systems (TCRTS) in 2016, he was asked to provide demographic statistics for the most recent flagship real-time conference, RTSS 2015. Of the 175 people who attended that event, only eight (yes, eight) were women! <sup>6</sup>

The UNC CS department features multiple groups and events that are already making efforts to broaden the participation of many underrepresented groups in computing. UNC's Graduate Women in CS (GWiCS) group hosts an annual research symposium to help undergraduate women and other under-represented minorities learn about research opportunities in CS. GWiCS also hosts Tar Heel Hack, in which local middle and high school girls participate in a six-hour hackathon. UNC CS also supports a Girls Who Code Club, which provides local girls in grades 6-12 with a community in which to learn about CS, and PearlHacks, which is one of the first all-female hackathons in the country. Additionally, UNC CS hosts an annual Open House and Science Expo, as well as Maze Day, which is an annual department event during which over 150 K-12 students with visual impairments visit to explore CS-related demos.

We intend to continue our involvement in these activities through the following actionable objectives:

- Tar Heel Hack project and Maze Day experience. We will incorporate some of our results into a Raspberry Pi and sensor-enabled Lego Robot hackathon project for future Tar Heel Hack events, to introduce the girls to various nuances of autonomy. We will also create an interactive robot building and sound-enabled motion debugging experience for Maze Day.

- CS Department demos. Using an F1/10-scale car and a home assistive robot, we have demoed our prior research for hundreds of local students at the UNC Science Expo and the CS Department Open House. In this vein, we will devise new demos involving autonomous drones, cars, and other robots for these events, as well as for Girls Who Code Club meetings, Tar Heel Hack, and PearlHacks.

- New first-year undergraduate seminar course. We will explore CPS topics ranging from control theory to path planning and AI applications in a new first-year undergraduate seminar course. We will also explore various aspects of the ethics of computing and other related topics.

<sup>&</sup>lt;sup>6</sup>PI Anderson was the first TCRTS chair to create a Diversity Committee in an attempt to begin rectifying this problem.

- Undergraduate and graduate CPS courses. In recent years, we have expanded our course offerings in CPS at both the undergraduate and graduate levels. We will incorporate results from this project into these courses, and produce freely available teaching materials.

- **REU opportunities and local outreach.** We will provide summer REUs for students from local colleges and universities to contribute to our work, and reach out to these schools to give talks on research and the process of applying to graduate CS programs. (Between them, Anderson and Alterovitz have chaired the UNC CS Graduate Admissions Committee for the past 19 years.)

### 7 Results From Prior NSF Support

Co-PI Sarathy has not received prior NSF support.

**Anderson and Smith.** CPS 1837337, CPS: Medium: GOALI: Real-Time Computer Vision in Autonomous Vehicles: Real Fast Isn't Good Enough, \$1,000,000, 10/1/2018-12/31/2021.

**Intellectual merit.** In this project (which will be in its final year when the proposed project starts), we have been investigating how to support real-time CV-based workloads on embedded automotive platforms. A key goal is to develop a real-time variant of OpenVX, a recently ratified CV API that allows algorithms to be specified in a graph-based way [52]. OpenVX has quickly emerged as the CV API of choice for embedded use cases, but lacks concepts relevant to real-time analysis, such as execution rates, priorities, *etc.* We have produced new research results on a number of topics, including techniques for increasing parallelism in CNN execution and GPU access [70,100], scheduling methods and schedulability analysis for OpenVX [7,8], the use of hardware threads to increase parallelism in real-time multicore systems [67–69], techniques for trading speed for accuracy in CNNs [95]. and algorithms and analysis for multiprocessor real-time scheduling and synchronization [2,34,65,90]. In total, we have produced 12 papers under the auspices of this grant, including one best paper awardee [34].

**Broader impacts.** Some of the experimental work in this project has involved using an F1/10-scale autonomous car. This car has been demoed at the UNC Science Expo, the CS Department Open House, and various GWiCS events (see Sec. 6). Two of the students in this project were also members of a UNC team that won the F/10 Autonomous Racing Challenge at CPS Week 2019. The results of this project have been featured in invited talks given by the investigators at military venues, universities, and conferences. Three Ph.D. students have been supported by this project; all are expected to complete their degrees in the next year. Two undergraduate students have also conducted research related to this project. Three graduate students have worked as summer interns at General Motors Research as part of this project.

# **Alterovitz.** CCF-1533844, XPS: FULL: DSD: Parallel Motion Planning for Cloud-Connected Robots, \$670,536, 9/1/2015–8/31/2020.

**Intellectual merit.** We developed a new software framework for motion planning for cloud-connected robots that effectively parallelizes motion planning and distributes the computation across the robot's embedded processor and cloud-based multicore servers. Our approach enables battery-powered robots, which may not have the compute power to quickly solve complex motion-planning problems using their embedded processor, to leverage the cloud while accounting for network latency and bandwidth limitations [38, 40–42]. We also developed algorithms that parallelize robot motion planning when executing tasks learned from human-provided demonstrations [14, 15]. We also created motion planning templates (MPT), an open-source robot motion planning library to share many of the results of this project [39].