# COMP311: COMPUTER ORGANIZATION!

Lecture 4: Transistors, Logic Gates

tinyurl.com/comp311-fa25

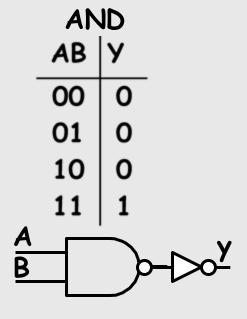

# AND

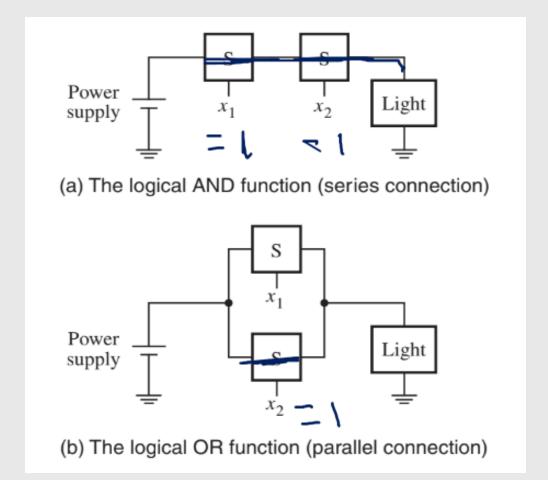

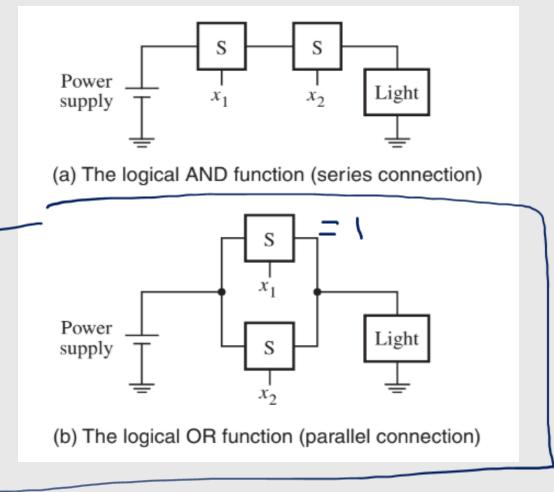

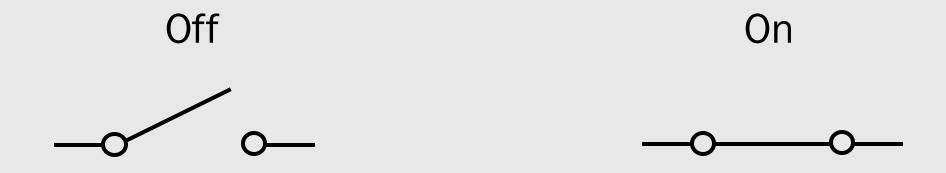

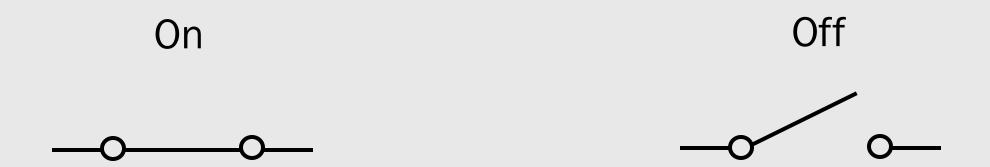

#### **Functions with Two Switches**

- Two switches can be connected either in series or in parallel

- Using a series connection, the light will be turned on only if both switches are closed. If either switch is open, the light will be off.

- $L(x1, x2) = x1 \cdot x2$ where L = 1 if x1 = 1 and x2 = 1, L = 0 otherwise.

Two basic two-input logic functions

is logical AND

#### Functions with Two Switches

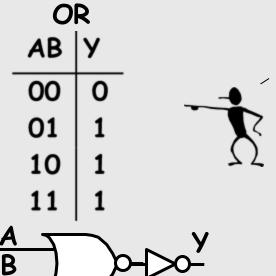

With a parallel connection of the two switches, the light will be on if either the x1 or x2 switch is closed. The light will also be on if both switches are closed. The light will be off only if both switches are open.

> - L(x1, x2) = x1 + x2where L = 1 if x1 = 1 or x2= 1 or if x1 = x2 = 1, L = 0 if x1 = x2 = 0.

■ "+" is logical OR

Two basic two-input logic functions

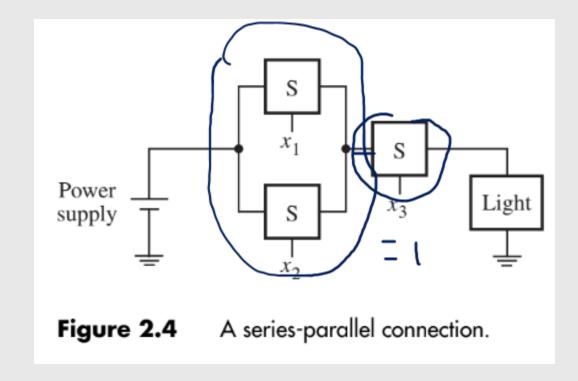

#### A Three-Switch Function

Three switches can be used to control the light in more complex ways. This seriesparallel connection of switches realizes the logic function:

-

$$L(x1, x2, x3) = (x1 + x2) \cdot x3$$

The light is on if  $x3 = 1$  and, at

■ The light is on if x3 = 1 and, at the same time, at least one of the x1 or x2 are 1.

#### **Truth Tables**

- Every logical function over a finite set of inputs can be described in a tabular fashion that enumerates all possible input combinations and provides the associated output.

- Functions expressed this way are called truth tables.

| $x_1$ | $x_2$ | $x_1 \cdot x_2$ | $x_1 + x_2$ |

|-------|-------|-----------------|-------------|

| 0     | 0     | 0               | 0           |

| 0     | 1     | 0               | 1           |

| 1     | 0     | 0               | 1           |

| 1     | 1     | 1               | 1           |

|       |       | AND             | OR          |

**Figure 2.6** A truth table for the AND and OR operations.

| $x_1$ | <i>x</i> <sub>2</sub> | <i>x</i> <sub>3</sub> | $x_1 \cdot x_2 \cdot x_3$ | $x_1 + x_2 + x_3$ |

|-------|-----------------------|-----------------------|---------------------------|-------------------|

| 0     | 0                     | 0                     | 0                         | 0                 |

| 0     | 0                     | 1                     | 0                         | 1                 |

| 0     | 1                     | 0                     | 0                         | 1                 |

| 0     | 1                     | 1                     | 0                         | 1                 |

| 1     | 0                     | 0                     | 0                         | 1                 |

| 1     | 0                     | 1                     | 0                         | 1                 |

| 1     | 1                     | 0                     | 0                         | 1                 |

| 1     | 1                     | 1                     | 1                         | 1                 |

**Figure 2.7** Three-input AND and OR operations.

# Pondering Truth Tables

# TRANSISTORS

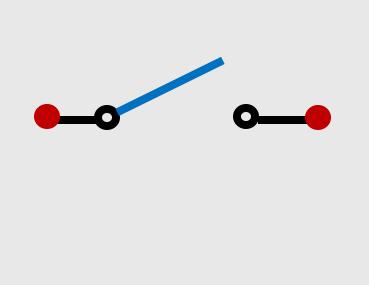

#### Transistors are like switches

Switches are controlled by physical contact

**Transistors** are controlled by a **voltage**

# Two States: Binary!

- Transistors can be in two distinct states: on or off

- This is why our machines communicate in binary (1s and 0s)!

# Logic Levels

- Instead of specifying the exact voltage level (e.g. 3V or 5V), we'll simply use binary terms when discussing transistors.

- We'll either have a high voltage or a low voltage.

- There are a few different terms for these voltage levels.

- High voltage

- logic high = logic 1 = 1

- Low voltage

- logic low = logic 0 = 0

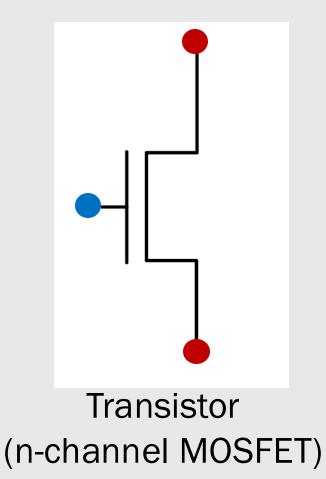

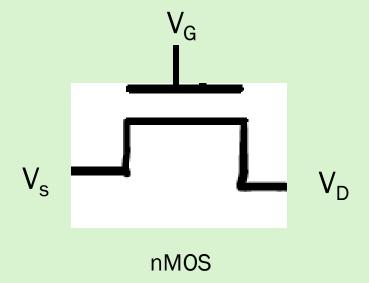

#### **Transistors**

- We will be working with two types of transistors

- nMOS transistors

- pMOS transistors

- There are three terminals

- Gate: controls whether the transistor is on or off

- Source and Drain: endpoints

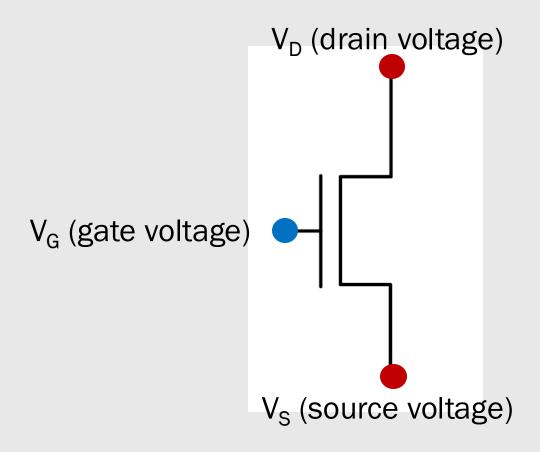

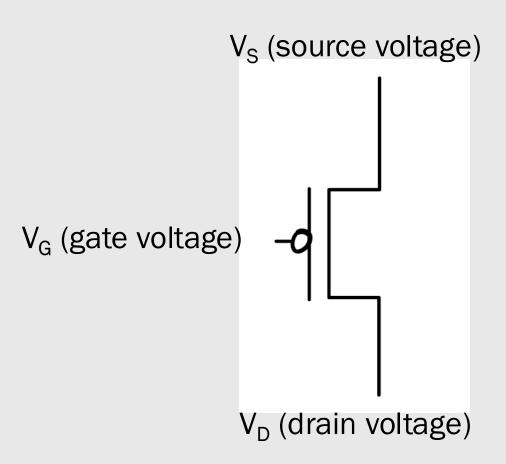

# **Transistor Symbol**

Switch

The terminal labeled with the blue dot determines whether current can flow between the terminals labeled with the red dot. 15

- There are three terminals

- Gate: controls whether the transistor is on or off

- Source and Drain: endpoints

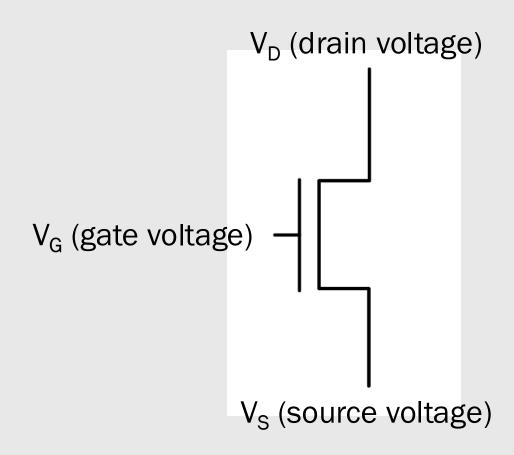

- If the gate voltage is high (logic 1), current can flow between source and drain

- The source and drain will be connected and will have the same voltage

- If the gate voltage is low, current cannot flow between source and drain

- The source and drain are not connected

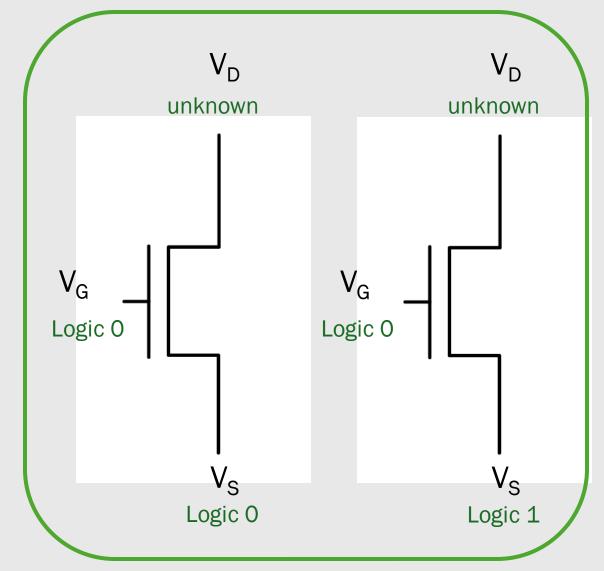

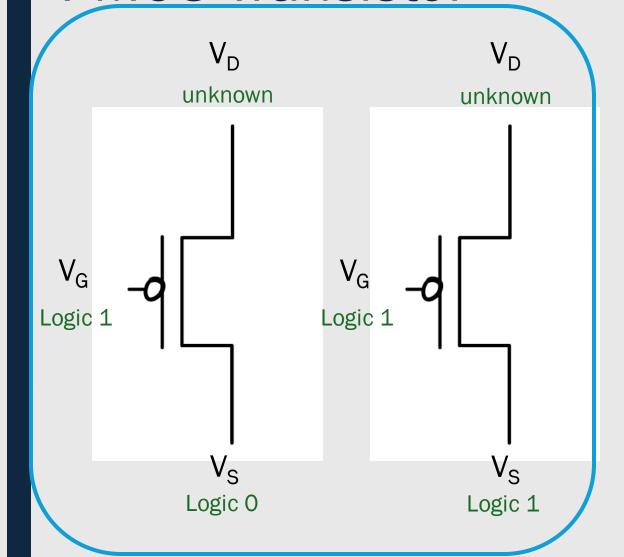

Let's say that we know the values of  $V_G$  and  $V_S$ . What is the value of  $V_D$  in each of the following diagrams?

V<sub>G</sub> is high, so source and drain are connected

V<sub>G</sub> is low, so source and drain are not connected

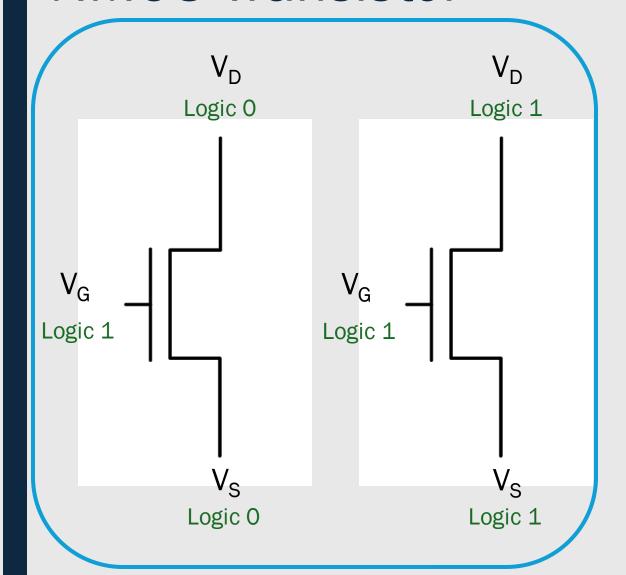

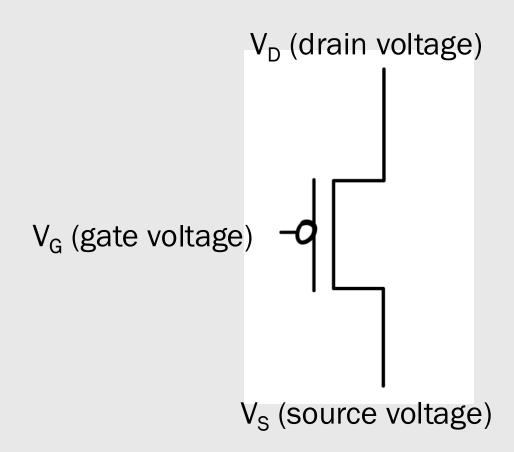

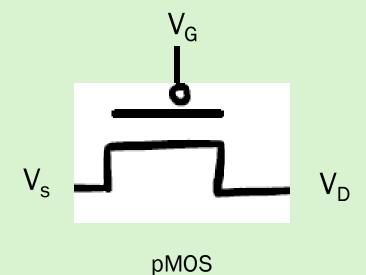

- There are three terminals

- Gate: controls whether the transistor is on or off

- Source and Drain: endpoints

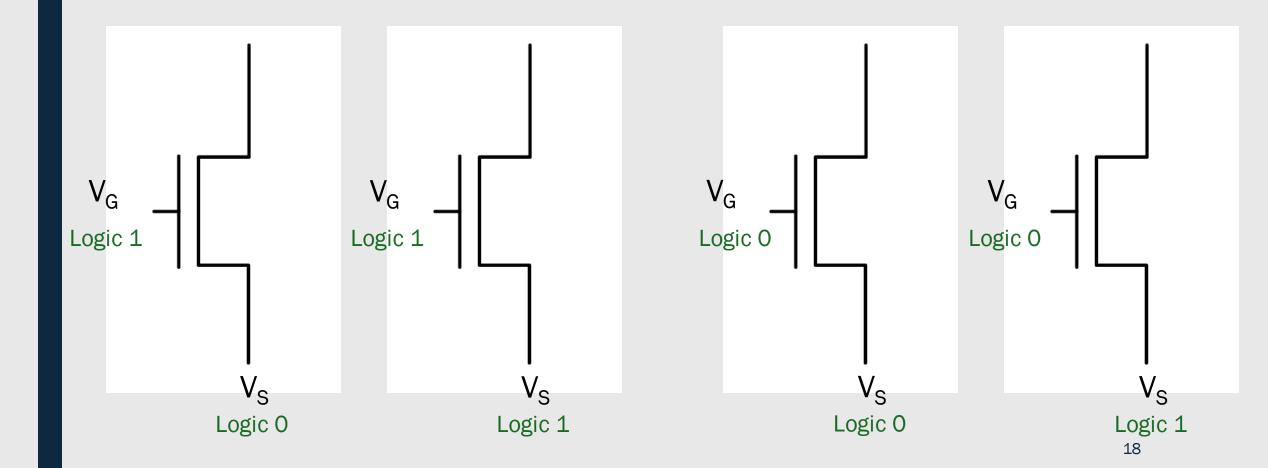

- If the gate voltage is low (logic 0), current can flow between source and drain

- This source and drain will be connected and will have the same voltage

- If the gate voltage is high, current cannot flow between source and drain

- The source and drain are not connected

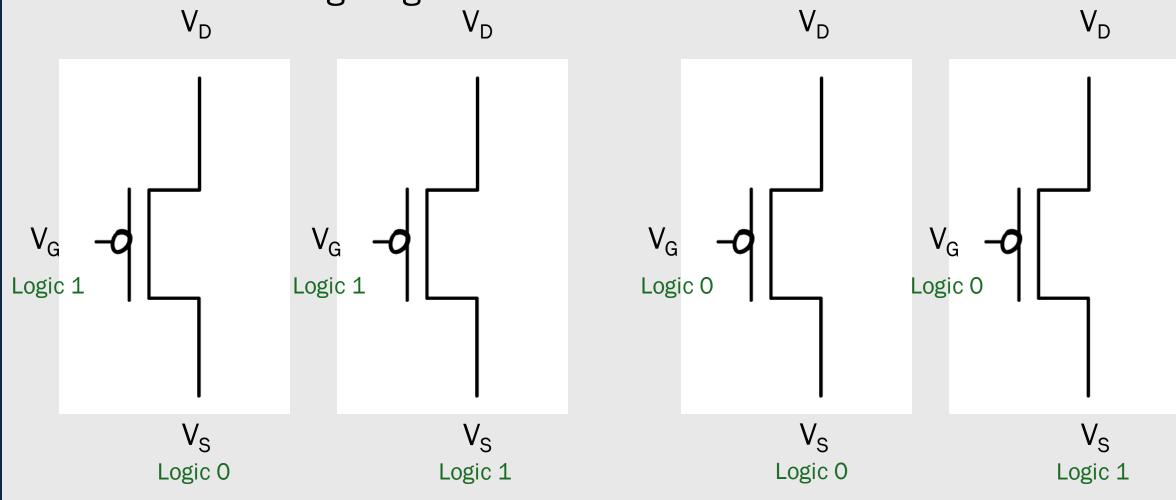

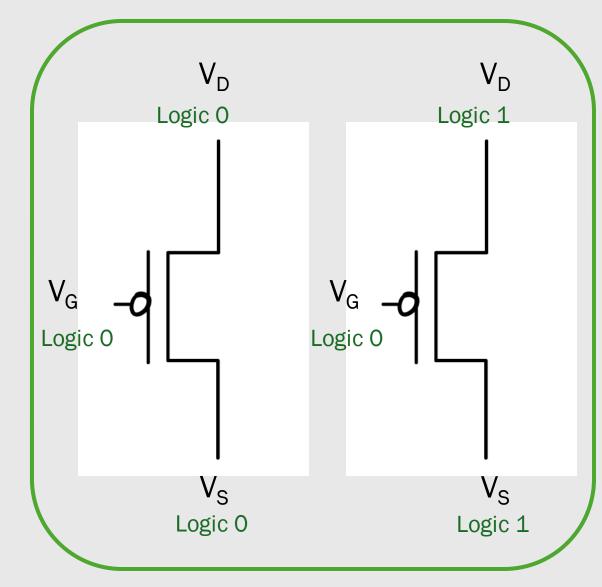

Let's say that we know the values of  $V_G$  and  $V_S$ . What is the value of  $V_D$  in each of the following diagrams?

V<sub>G</sub> is high, so source and drain are not connected

V<sub>G</sub> is low, so source and drain are connected

# Two Types of Transistors

|                                 | nMOS       | pMOS       |

|---------------------------------|------------|------------|

|                                 |            |            |

| Behaves as an open switch when  | Vg is low  | Vg is high |

| Behaves as a closed switch when | Vg is high | Vg is low  |

Acts as a(n) \_\_\_\_\_ (open/closed) switch when the gate voltage (Vg) is low.

Meaning that current \_\_\_\_\_ (can/cannot) flow between source and drain.

Acts as a(n) \_\_\_\_\_ (open/closed) switch when the gate voltage (Vg) is high.

Meaning that current \_\_\_\_\_ (can/cannot) flow between source and drain.

Acts as a(n) \_\_\_\_\_ (open/closed) switch when the gate voltage (Vg) is low.

Meaning that current \_\_\_\_\_ (can/cannot) flow between source and drain.

Acts as a(n) \_\_\_\_\_ (open/closed) switch when the gate voltage (Vg) is high.

Meaning that current \_\_\_\_\_ (can/cannot) flow between source and drain.

# BUILDING LOGIC GATES WITH TRANSISTORS

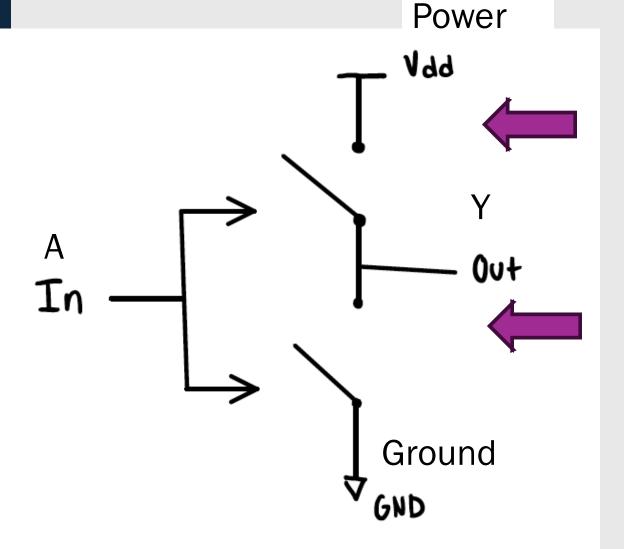

# Designing An Inverter

I want to design a circuit that takes as an input a one-bit value and outputs the complement of that number.

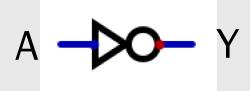

Symbol

Truth Table

| Α | Υ |

|---|---|

| 0 | 1 |

| 1 | 0 |

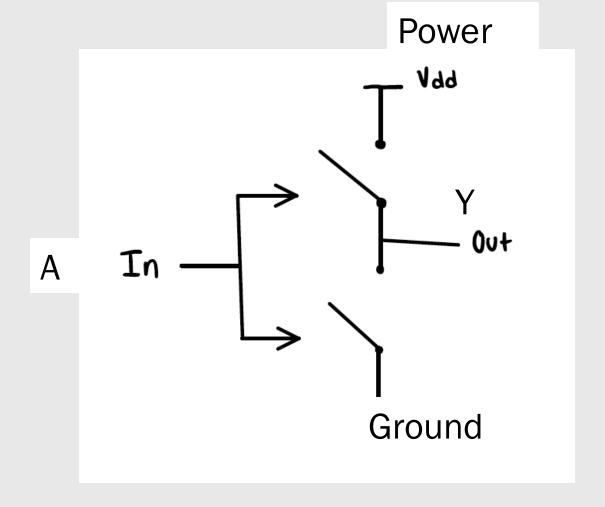

# New Components

- Power

- a component that produces a logic high value

- Ground

- a component that produces a logic low value

#### An Inverter with Switches

#### An Inverter with Switches

- When the input is 0

- The top switch is closed.

- The bottom switch is open.

- This will connect power to the output which will make the output 1.

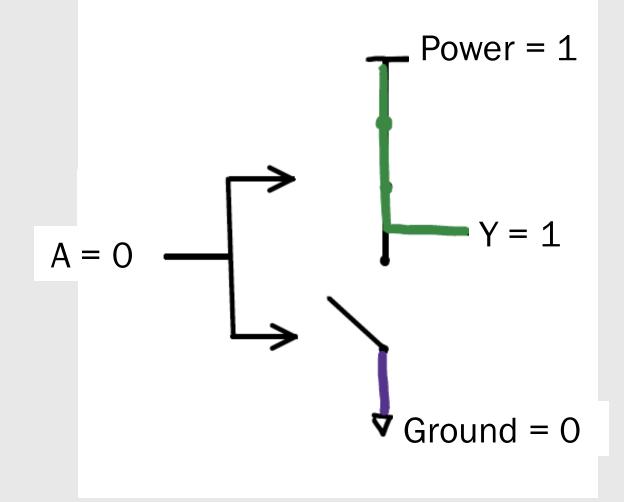

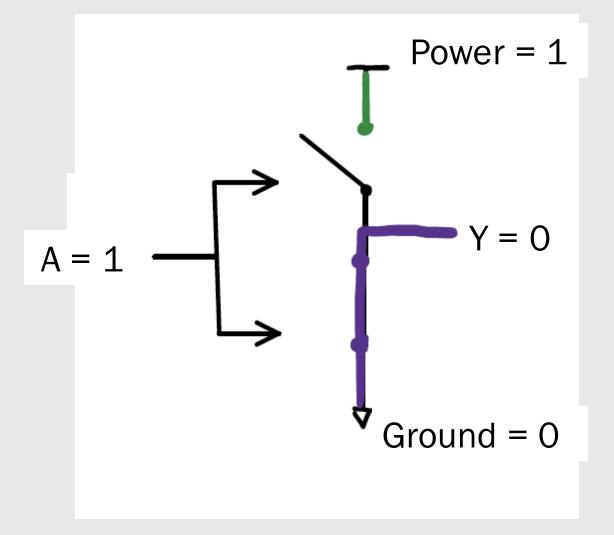

#### An Inverter with Switches

- When the input is 1

- The bottom switch is closed.

- The top switch is open.

- This will connect ground to the output which will make the output 0.

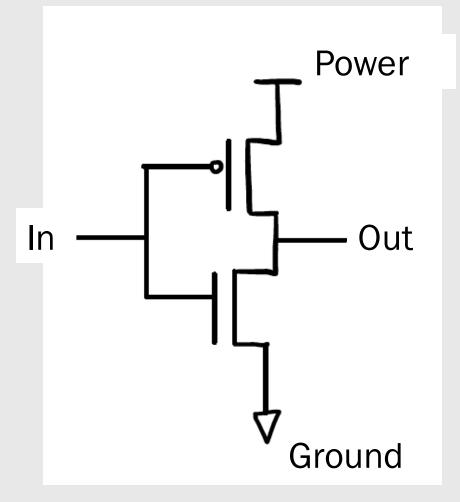

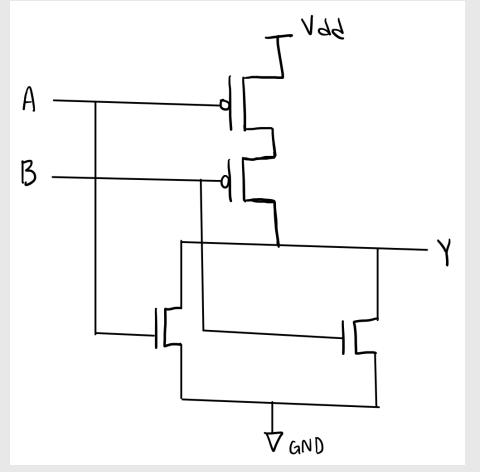

# **Building Logic Gates with Transistors**

- Due to the physical characteristics of the transistors (which we don't have the physics background to get into in this class)...

- We use nmos transistors to connect the output to ground

- We use pmos transistors to connect the output to power

# Building an Inverter with Transistors

Should this switch be replaced by an nmos or pmos transistor?

Should this switch be replaced by an nmos or pmos transistor?

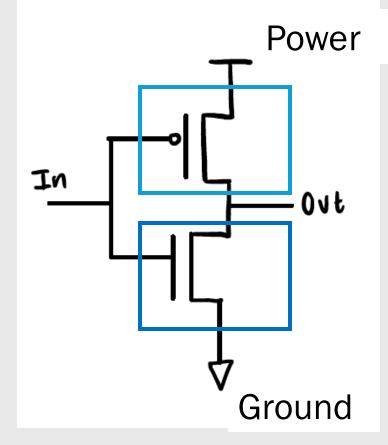

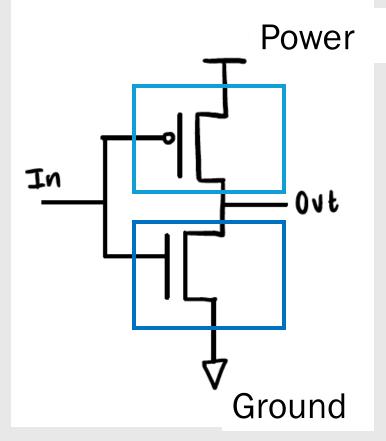

# **CMOS** Inverter

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

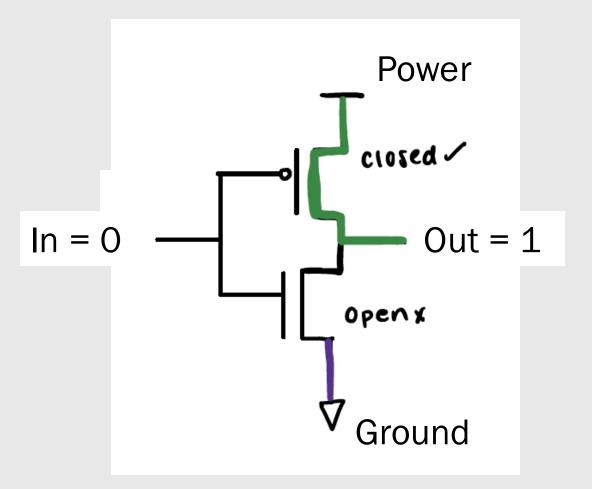

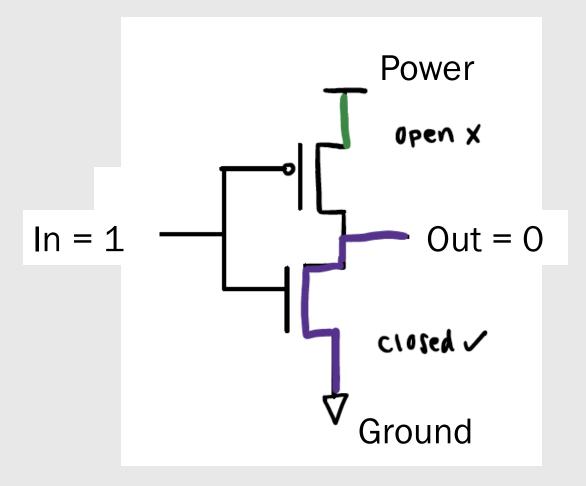

# **CMOS** Inverter

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

# **CMOS** Inverter

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

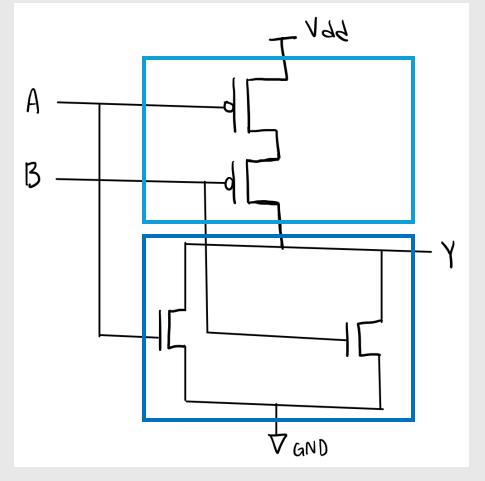

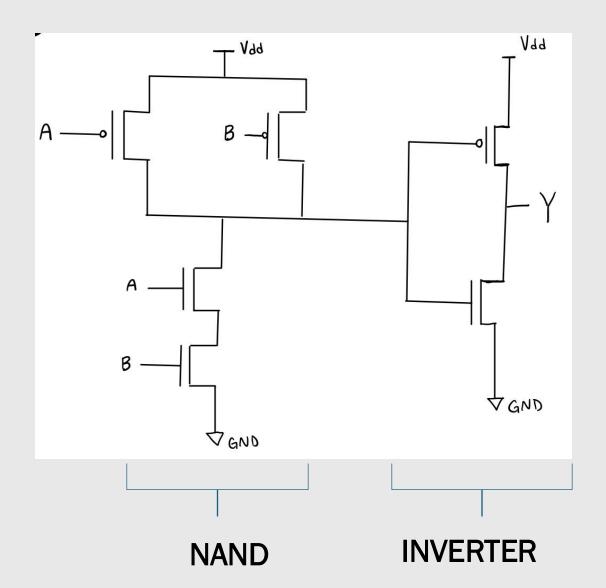

#### **CMOS Gates**

- CMOS = Complementary MOS

- The pMOS and nMOS transistors complement each other to form the logic gate

- Common confusion

- CMOS is not a type of transistor!

- It is a technology that combines both nMOS and pMOS transistors

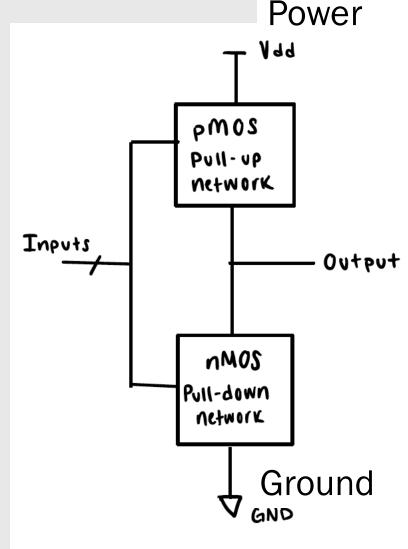

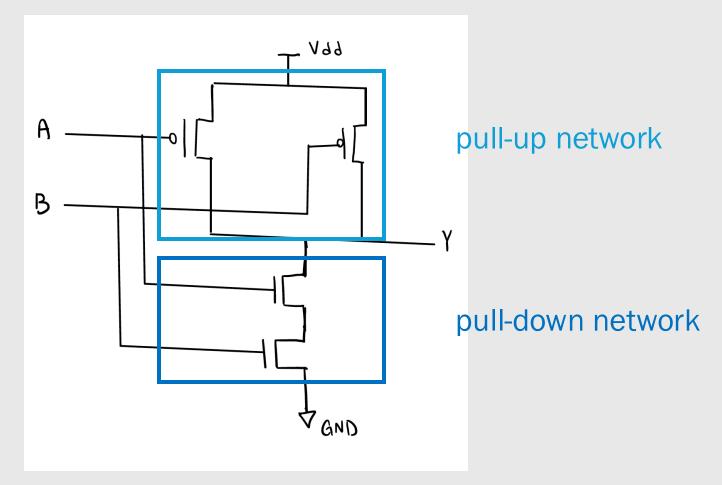

# Pull-up and Pull-down Networks

- Only one network will be on at a time

- The pull-up network drives the output when the output is 1

- The pull-down network drives the output when the output is 0

#### **CMOS** Inverter

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

pull-up network

pull-down network

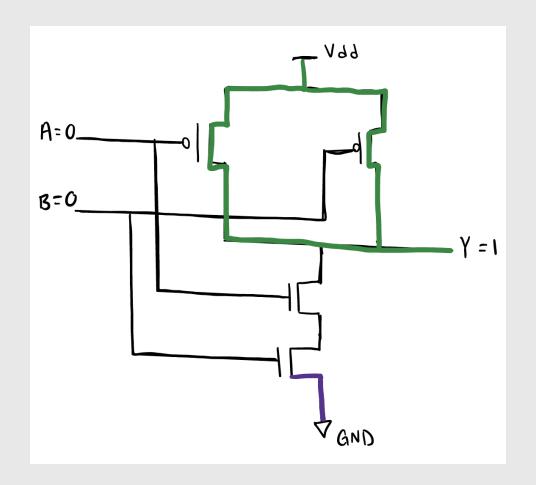

## **CMOS** Tracing

| In | Out |

|----|-----|

| 0  | 1   |

| 1  | 0   |

pull-up network

pull-down network

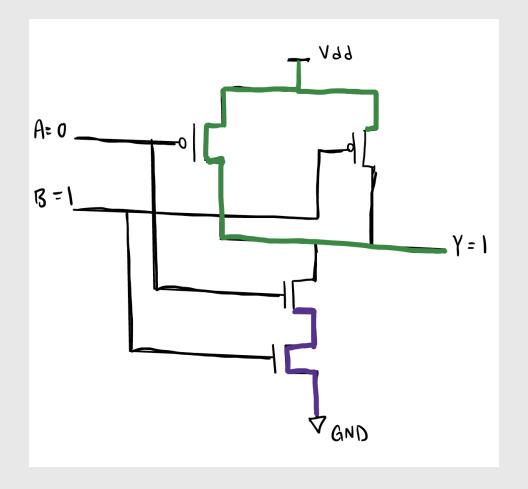

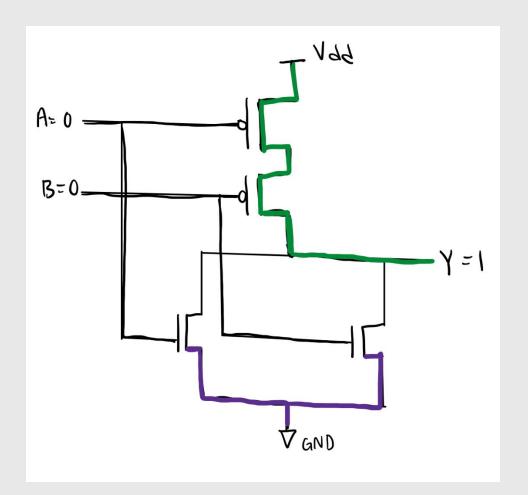

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Α | В | Υ |

|---|---|---|

| O | 0 | 1 |

| O | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| Α | В | Υ |

|---|---|---|

| O | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

both pMOS on, pull-up works

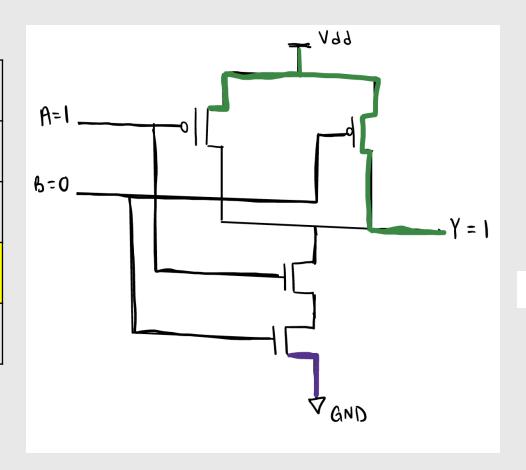

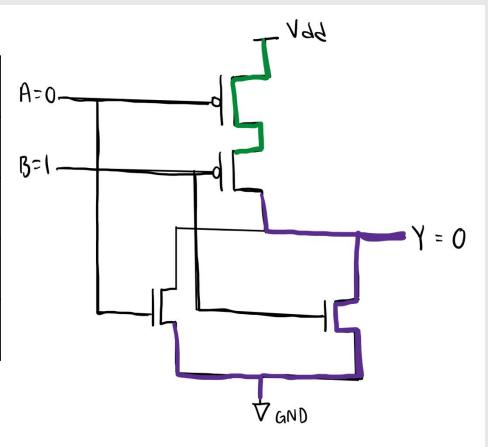

| Α | В | Υ |

|---|---|---|

| О | 0 | 1 |

| O | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

A's pMOS still on, output pulled high

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

B's pMOS still on, output pulled high

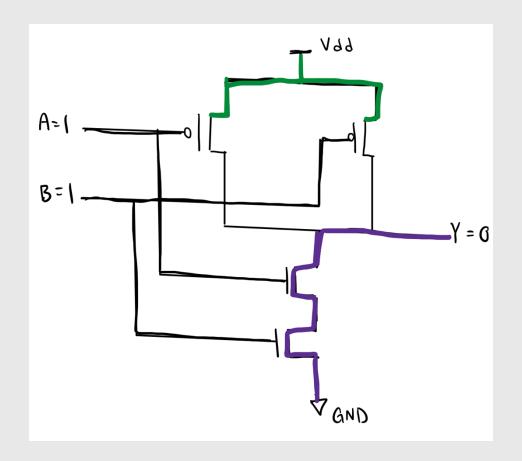

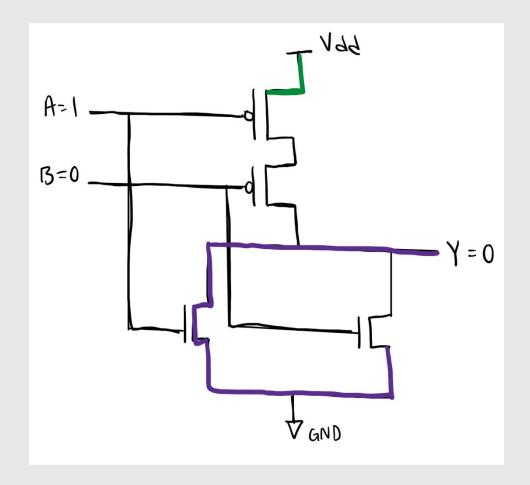

| Α | В | Υ |

|---|---|---|

| O | 0 | 1 |

| O | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

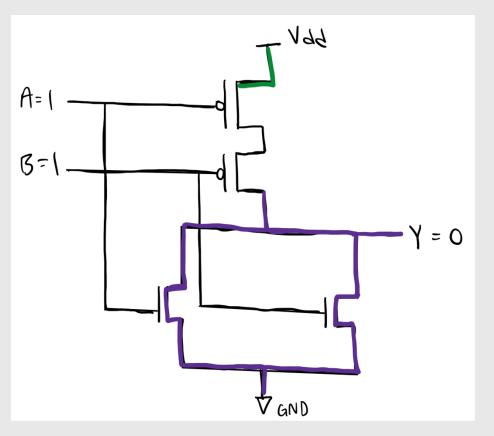

both pMOS off, both nMOS on → path to ground

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

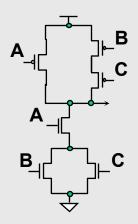

#### General CMOS Gate Recipe

Step 1. Figure out pulldown network that does what you want (i.e the set of conditions where the output is '0')

e.g.,

$$F = A*(B+C)$$

Step 2. Build the "opposite" version of that network to figure out when the output should be 1.

Step 3. Combine the two so you have a circuit that always pulls the output either up to 1 or down to 0.

But isn't it hard to wire it all up?

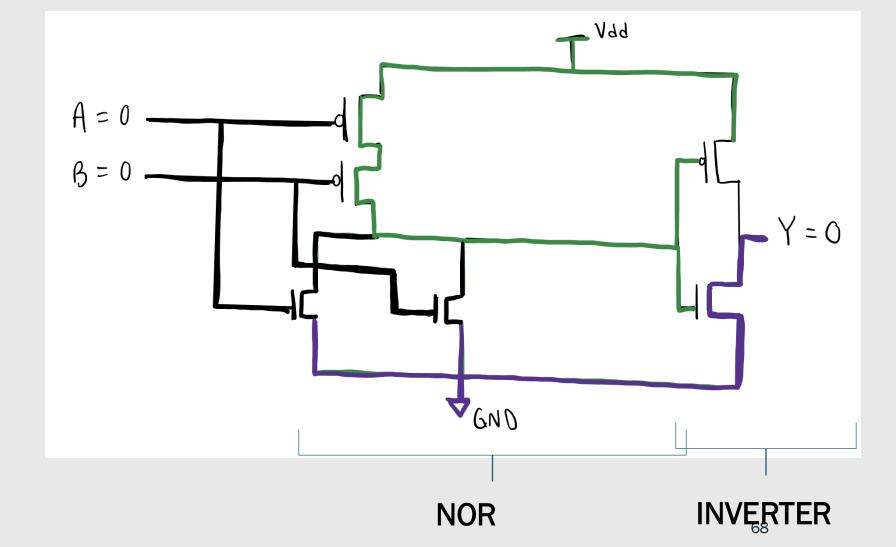

| А | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| О | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

| Α | В | Υ |

|---|---|---|

| O | 0 | 1 |

| O | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

pull-up network

pull-down network

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

both pMOS on, output pulled up

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| O | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

B's nMOS on, pulls down

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

A's nMOS on, pulls down

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

both nMOS on, strong pull down

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

| Α | В | Υ |

|---|---|---|

| 0 | 0 | 0 |

| О | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

## **Transistor Count**

| Gate | Number of Transistors |

|------|-----------------------|

| NOT  | 2                     |

| AND  | 6                     |

| OR   | 6                     |

| NAND | 4                     |

| NOR  | 4                     |

| XOR  | 12                    |

| XNOR | 12                    |

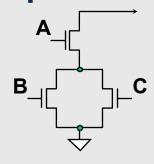

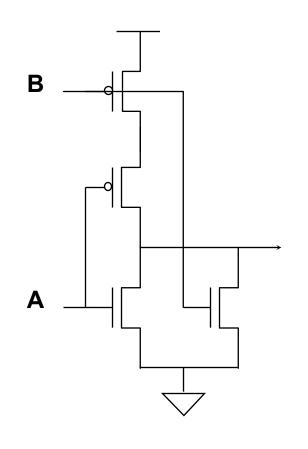

#### What function does this gate compute?

| Α | В | <b>C</b> |

|---|---|----------|

| 0 | 0 |          |

| 0 | 1 |          |

| 1 | 0 |          |

| 1 | 1 |          |

|   |   |          |

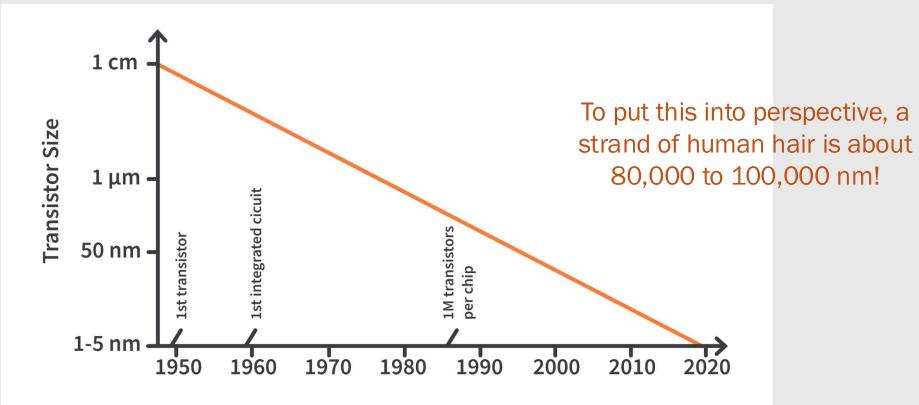

#### **Transistor Size**

- The first transistor was successfully demonstrated in 1947, at Bell Laboratories (the research arm of AT&T)

- Transistor size has exponentially decreased year after year leading to huge gains in performance and processing capabilities

#### Technology Node (nanometer size)

- You may have heard that the new M4 chips use a 3nm technology node. What does that mean?

- Historically, the node name was closely related to the physical distance between the source and drain terminals (known as the gate length).

- We are reaching the limits of how small we can make the gate length.

- The performance improvements that we see in transistor technology today are based on more factors than just the gate length.

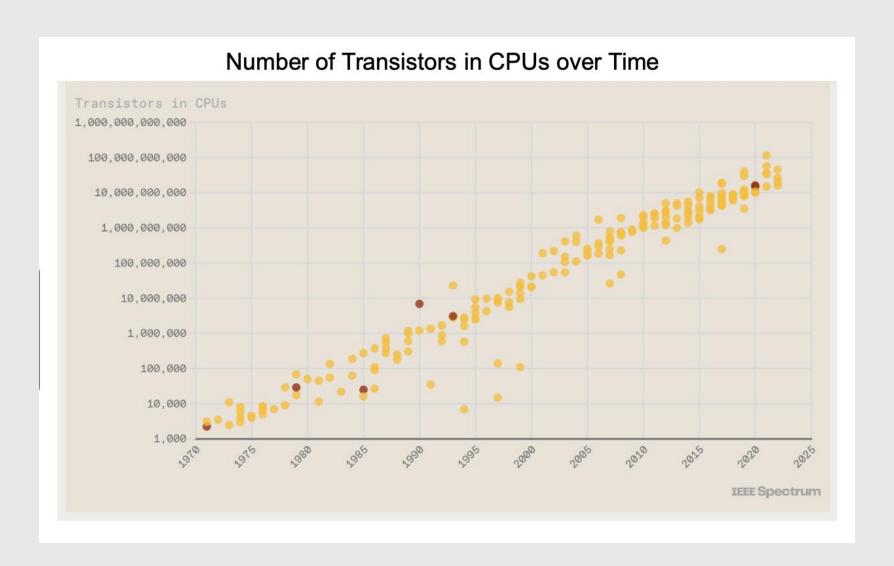

#### Recall: Moore's Law

# LOGIC GATES

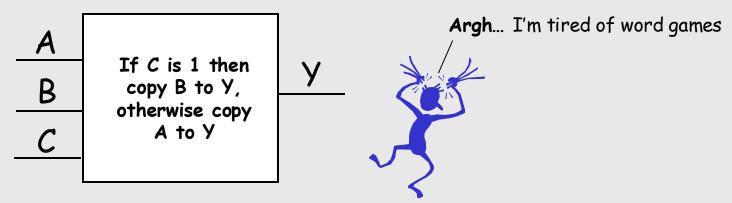

#### Now can we design larger systems!

We need to start somewhere – usually with a functional specification

If you are like most pragmatists you'd rather be given a table or formula than solve a puzzle to understand a function. The fact is, every combinational function can be expressed as a table.

"Truth tables" are a concise description of the combinational system's function, where an output is specified for \*every\* input combination.

#### Inverter/Not Gate

Symbol

Truth Table

| Α | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

Equation

$$Y = \overline{A}$$

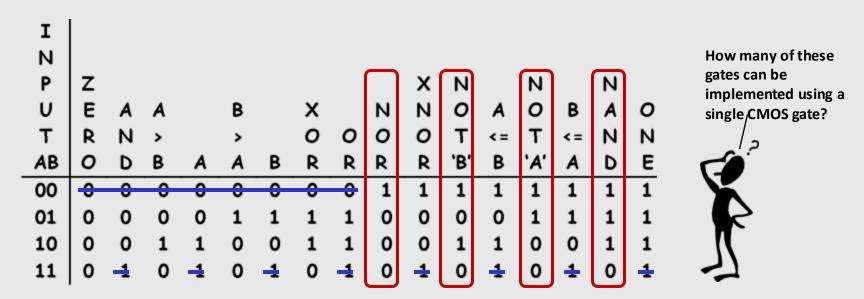

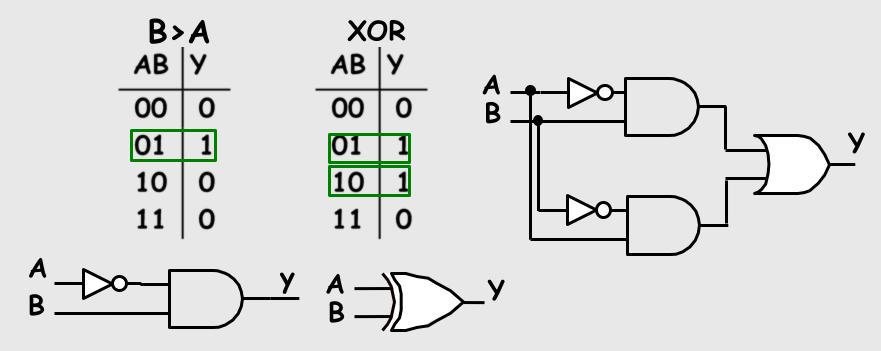

#### What Gates can we build?

Recall, we need to design our gates using a pull-up network of pMOS transistors and a pull-down network of nMOS transistors

|                                 | AND |   | 0  | OR |    | NAND |    | )R |

|---------------------------------|-----|---|----|----|----|------|----|----|

| What gates can we               | AB  | У | AB | У  | AB | У    | AB | У  |

| - build?<br>- define?           | 00  | 0 | 00 | 0  | 00 | 1    | 00 | 1  |

| - define:                       | 01  | 0 | 01 | 1  | 01 | 1    | 01 | 0  |

| Let's start by                  | 10  | 0 | 10 | 1  | 10 | 1    | 10 | 0  |

| considering only 2-input gates. | 11  | 1 | 11 | 1  | 11 | 0    | 11 | 0  |

How many possible 2-input gates are there?

**KEY IDEA:** As many as there are 2-input truth tables.

#### All the gates!

There are only 16 possible 2-input gates... Let's examine all of them. Some we already know, others are just silly.

Do we really need all of these gates?

Nope! Once we realize that we can describe all of them using just AND, OR, and NOT

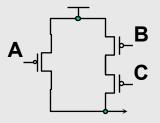

#### Composing gates: AND and OR

Each can be constructed using a pair of CMOS gates

AND is just NAND with an inverter, and OR is just NOR with an inverted output.

These two gates are particularly important.

Using them will allows us to develop a systematic approach for constructing any combinational function.

#### Composing gates

How many different gates do we really need?

We can always do it with 3 different types of gates (AND, OR, INVERT), and sometimes with 2, but, can we use fewer?

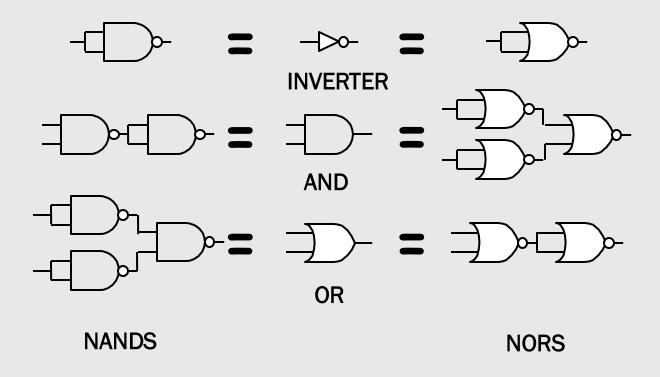

#### One will do!

NANDs and NORs are UNIVERSAL!

A UNIVERSAL gate is one that can be used to implement \*ANY\* COMBINATIONAL FUNCTION. There are many UNIVERSAL gates, but not all gates are UNIVERSAL.

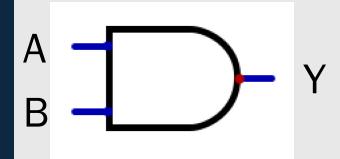

#### **AND Gate**

Symbol

**Truth Table**

| Α | В | Y |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Equation

$$Y = A \times B$$

or

$Y = AB$